Совмещённый блок деления и вычисления квадратного корня с

advertisement

УДК 621.382(06) Микроэлектроника

С.А. НИКОЛКО

НИИ системных исследований РАН, Москва

СОВМЕЩЁННЫЙ БЛОК ДЕЛЕНИЯ И ВЫЧИСЛЕНИЯ

КВАДРАТНОГО КОРНЯ С ПЛАВАЮЩЕЙ ЗАПЯТОЙ

ДВОЙНОЙ ТОЧНОСТИ

В статье описаны трудности, вставшие перед автором во время добавления в

блок деления функции вычисления квадратного корня.

В настоящее время в НИИСИ РАН разрабатывается 64 разрядный

RISC процессор К3. Перед автором была поставлена задача - добавить в

уже имеющийся блок деления [1] функцию вычисления квадратного

корня. Объединение этих двух вычислителей в один блок обусловлено

однотипностью алгоритма их работы.

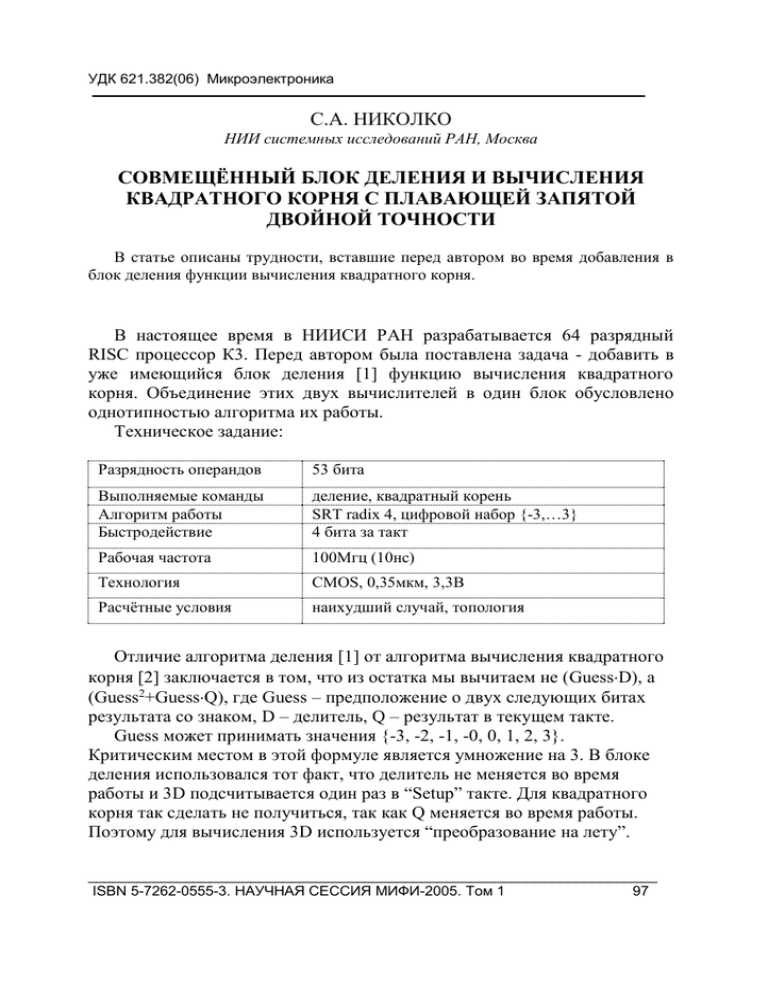

Техническое задание:

Разрядность операндов

53 бита

Выполняемые команды

Алгоритм работы

Быстродействие

деление, квадратный корень

SRT radix 4, цифровой набор {-3,…3}

4 бита за такт

Рабочая частота

100Мгц (10нс)

Технология

CMOS, 0,35мкм, 3,3В

Расчётные условия

наихудший случай, топология

Отличие алгоритма деления [1] от алгоритма вычисления квадратного

корня [2] заключается в том, что из остатка мы вычитаем не (GuessD), а

(Guess2+GuessQ), где Guess – предположение о двух следующих битах

результата со знаком, D – делитель, Q – результат в текущем такте.

Guess может принимать значения {-3, -2, -1, -0, 0, 1, 2, 3}.

Критическим местом в этой формуле является умножение на 3. В блоке

деления использовался тот факт, что делитель не меняется во время

работы и 3D подсчитывается один раз в “Setup” такте. Для квадратного

корня так сделать не получиться, так как Q меняется во время работы.

Поэтому для вычисления 3D используется “преобразование на лету”.

______________________________________________________________________

ISBN 5-7262-0555-3. НАУЧНАЯ СЕССИЯ МИФИ-2005. Том 1

97

УДК 621.382(06) Микроэлектроника

Критический блок SRT_Guess, задержка на котором составляет 4200

пс, состоит из блока предсказания Guess, сумматора R_Short и

мультиплексора. Основное увеличение задержки при добавлении

функции квадратного корня произошло из-за усложнения блока

предсказания, теперь он содержит две функции и мультиплексор.

Задержка на сумматоре R_Short осталась такой же.

Самым сложным местом, с точки зрения синтеза, является

мультиплексор, управляющие сигналы которого идут во все блоки и

являются частью всех околокритических путей и поэтому сильно

нагружены.

Ещё одной проблемой стало то, что мультиплексор является блоком

ручного синтеза, то есть, написан с помощью элементов библиотеки и

синтезатору запрещено его менять. У триггера Guess есть прямой и

инверсный выходы. Вместо того чтобы менять местами входы

мультиплексора и равномерно нагружать прямой и инверсный выходы

триггера Synopsys design compiler нагрузил только прямой выход

триггера. Эту проблема тоже была решена вручную.

После синтеза топологии была получена указанная в ТЗ рабочая

частота 100МГц, с запасом 70 пс.

Список литературы

1. Николко С.А. Реализация алгоритма деления чисел с плавающей запятой двойной

точности //Электроника, микро – и наноэлектроника. Сборник научных трудов. М.: МИФИ,

2004.- С.209-212

2. Square root theory - http://www.dattalo.com/technical/theory/sqrt.html

______________________________________________________________________

ISBN 5-7262-0555-3. НАУЧНАЯ СЕССИЯ МИФИ-2005. Том 1

98