Анализатор пакетов интерфейса rapidio

advertisement

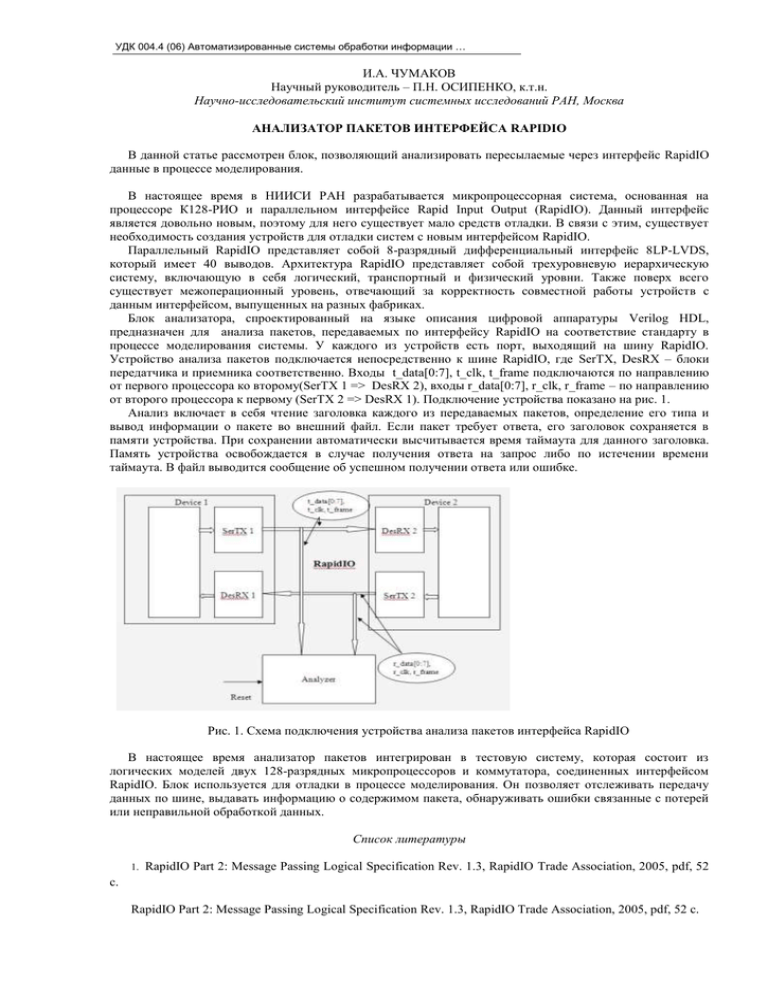

УДК 004.4 (06) Автоматизированные системы обработки информации … И.А. ЧУМАКОВ Научный руководитель – П.Н. ОСИПЕНКО, к.т.н. Научно-исследовательский институт системных исследований РАН, Москва АНАЛИЗАТОР ПАКЕТОВ ИНТЕРФЕЙСА RAPIDIO В данной статье рассмотрен блок, позволяющий анализировать пересылаемые через интерфейс RapidIO данные в процессе моделирования. В настоящее время в НИИСИ РАН разрабатывается микропроцессорная система, основанная на процессоре К128-РИО и параллельном интерфейсе Rapid Input Output (RapidIO). Данный интерфейс является довольно новым, поэтому для него существует мало средств отладки. В связи с этим, существует необходимость создания устройств для отладки систем с новым интерфейсом RapidIO. Параллельный RapidIO представляет собой 8-разрядный дифференциальный интерфейс 8LP-LVDS, который имеет 40 выводов. Архитектура RapidIO представляет собой трехуровневую иерархическую систему, включающую в себя логический, транспортный и физический уровни. Также поверх всего существует межоперационный уровень, отвечающий за корректность совместной работы устройств с данным интерфейсом, выпущенных на разных фабриках. Блок анализатора, спроектированный на языке описания цифровой аппаратуры Verilog HDL, предназначен для анализа пакетов, передаваемых по интерфейсу RapidIO на соответствие стандарту в процессе моделирования системы. У каждого из устройств есть порт, выходящий на шину RapidIO. Устройство анализа пакетов подключается непосредственно к шине RapidIO, где SerTX, DesRX – блоки передатчика и приемника соответственно. Входы t_data[0:7], t_clk, t_frame подключаются по направлению от первого процессора ко второму(SerTX 1 => DesRX 2), входы r_data[0:7], r_clk, r_frame – по направлению от второго процессора к первому (SerTX 2 => DesRX 1). Подключение устройства показано на рис. 1. Анализ включает в себя чтение заголовка каждого из передаваемых пакетов, определение его типа и вывод информации о пакете во внешний файл. Если пакет требует ответа, его заголовок сохраняется в памяти устройства. При сохранении автоматически высчитывается время таймаута для данного заголовка. Память устройства освобождается в случае получения ответа на запрос либо по истечении времени таймаута. В файл выводится сообщение об успешном получении ответа или ошибке. Рис. 1. Схема подключения устройства анализа пакетов интерфейса RapidIO В настоящее время анализатор пакетов интегрирован в тестовую систему, которая состоит из логических моделей двух 128-разрядных микропроцессоров и коммутатора, соединенных интерфейсом RapidIO. Блок используется для отладки в процессе моделирования. Он позволяет отслеживать передачу данных по шине, выдавать информацию о содержимом пакета, обнаруживать ошибки связанные с потерей или неправильной обработкой данных. Список литературы 1. RapidIO Part 2: Message Passing Logical Specification Rev. 1.3, RapidIO Trade Association, 2005, pdf, 52 с. RapidIO Part 2: Message Passing Logical Specification Rev. 1.3, RapidIO Trade Association, 2005, pdf, 52 с. УДК 004.4 (06) Автоматизированные системы обработки информации … RapidIO Part 3: Common Transport Specification Rev. 1.3, RapidIO Trade Association, 2005, pdf, 32 с. RapidIO Part 4: 8/16 LP-LVDS Physical Layer Specification Rev. 1.3, RapidIO Trade Association, 2005, pdf, 160 с.