3. Основные логические операции над двоичными числами

advertisement

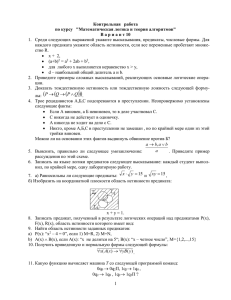

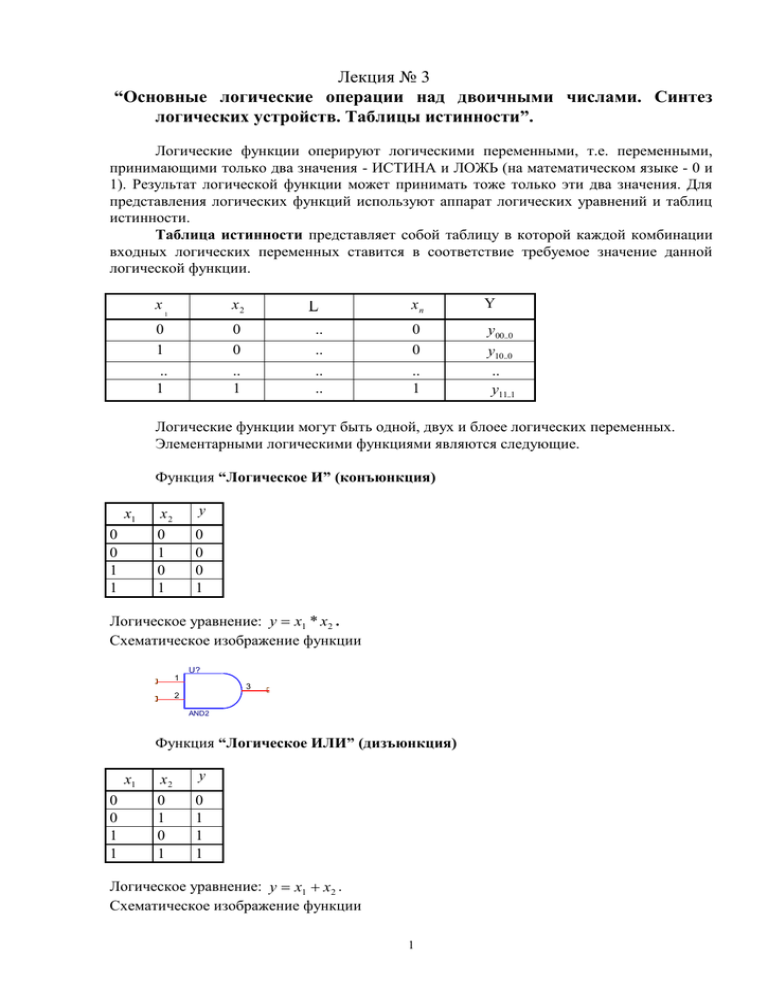

Лекция № 3 “Основные логические операции над двоичными числами. Синтез логических устройств. Таблицы истинности”. Логические функции оперируют логическими переменными, т.е. переменными, принимающими только два значения - ИСТИНА и ЛОЖЬ (на математическом языке - 0 и 1). Результат логической функции может принимать тоже только эти два значения. Для представления логических функций используют аппарат логических уравнений и таблиц истинности. Таблица истинности представляет собой таблицу в которой каждой комбинации входных логических переменных ставится в соответствие требуемое значение данной логической функции. x1 x2 L xn Y 0 1 .. 1 0 0 .. 1 .. .. .. .. 0 0 .. 1 y00..0 y10..0 .. y11..1 Логические функции могут быть одной, двух и блоее логических переменных. Элементарными логическими функциями являются следующие. Функция “Логическое И” (конъюнкция) x1 0 0 1 1 y x2 0 1 0 1 0 0 0 1 Логическое уравнение: y x1 * x2 . Схематическое изображение функции U? 1 3 2 AND2 Функция “Логическое ИЛИ” (дизъюнкция) x1 0 0 1 1 x2 0 1 0 1 y 0 1 1 1 Логическое уравнение: y x1 x2 . Схематическое изображение функции 1 U? 1 3 2 OR2 Функция “Логическое НЕ” (отрицание) x y 0 1 1 0 Логическое уравнение: y x . Схематическое изображение функции U? 1 2 NOT Логические теоремы. A A A A* A A A 1 1 A*0 0 A0 A A *1 A A A A A 1 A* A 0 A* B B* A A B B A A * ( B C) A * B A * C A A* B A A B * C ( A B) * ( A C) A B C K A * B * C*K A * B * C*K A B C K Используя данные теоремы, любую логическую функцию можно реализовать посредством блоков “И” и “НЕ” или “ИЛИ” и “НЕ” (это доказал Шеффер в 1913г.). Схемы элементов «И-НЕ» (штрих Шеффера), «ИЛИ-НЕ» (Стрелка Пирса) и «НЕ», реализованные на комплементарных МОП-транзисторах (КМОП-технология), представлены на рисунке. 2 VCC T2 Ui Uo T1 NOT 0 Пример: Функция “ИСКЛЮЧАЮЩЕЕ ИЛИ” (сложение по модулю 2). Схемотическое изображение функции U? 1 3 2 XOR x1 0 0 1 1 x2 0 1 0 1 y 0 1 1 0 y x1 x2 x1 * x2 x1 * x2 x1 * x2 * x1 * x2 x1 x2 x1 x2 Обычно при постановке задачи логическую функцию представляют в виде таблицы истинности. Для получения уравнения логической функции и его минимизации используют метод “карт Карно”. В соответствии с этим методом для получения уравнения логической функции необходимо: 1. Составить таблицу истинности функции в которой должны быть представлены все возможные сочетания входных сигналов и соответствующие им состояния выхода. В случае, когда состояние входа не оказывает влияния на выход, ставится X (любое значение). 2. Разбить все входные переменные на две группы произвольным образом. 3. Составить прямоугольную таблицу. Вдоль осей таблицы отложить последовательные состояния выделенных групп переменных в коде Грея. 4. Заполнить ячейки, расположенные на пересечении строк и столбцов таблицы значениями функции, соответствующими текущей комбинации состояний входных переменных. 5. Выделить в таблице все группы, содержащие 1 (либо 0). 6. Записать уравнение функции по выделенным группам. Пример: Функция задана таблицей истинности. 3 A B C Q 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 0 0 1 0 1 1 1 Составим карту Карно для данной функции. AB C 0 1 00 0 0 01 0 1 11 1 1 10 0 1 Выделяем группы, содержащие “1”. Согласно выделенным группам записываем уравнение логической функции. Q A* B B *C A*C Схематическое изображение функции: U1 A B 1 3 2 AND2 U2 U4 1 3 C 2 AND2 1 2 3 4 Q OR3 U3 1 3 2 AND2 Рассмотрим основные виды комбинационных логических устройств. Полным дешифратором называется устройство, имеющее n входов и 2 n выходов, причем каждой комбинации значений входных сигналов соответствует сигнал, равный 1, только на одном выходе. В качестве примера рассмотрим дешифратор на 2 входа. Его таблица истинности имеет вид. X1 X2 Q0 Q1 Q2 Q3 0 0 1 0 0 0 0 1 0 1 0 0 1 0 0 0 1 0 4 1 1 0 0 0 1 Т.о., логические уравнения для соответствующих выходных разрядов дешифратора имеют вид: Q0 X 1 * X 2 ; Q1 X 1 * X 2 ; Q2 X 1 * X 2 ; Q3 X 1 * X 2 . Схема, реализующая подобное устройство имеет вид. Q0 AND2 X1 Q1 AND2 INV X2 Q2 AND2 INV Q3 AND2 Полный дешифратор, дополненный общим разрешающим входом называется дешифратором-демультиплексором. Если добавить в рассмотренный дешифратор общий разрешающий вход E, то его уравнения примут вид: Q0 E * X 1 * X 2 ; Q1 E * X 1 * X 2 ; Q2 E * X 1 * X 2 ; Q3 E * X 1 * X 2 . Примером подобного дешифратора может служить микросхема 1533 ИД7 (74ALS138), представляющая собой дешифратор 3*8 с тремя входами общего разрешения: единичным G1, нулевыми G2AN и G2BN. Работа микросхемы разрешена если G1=1 & G2AN=0 & G2BN=0. A B C G1 G2AN G2BN Y0N Y1N Y2N Y3N Y4N Y5N Y6N Y7N 74138 Т.о., дешифраторы осуществляют преобразование двоичного кода в унитарный код, т.е. код, только один из разрядов которого равен 1. Шифраторы выполняют функцию обратную дешифраторам, т.е. преобразуют унитарный код в двоичный. Таблица истинности шифратора на 4 входа имеет вид: X1 X2 X3 X4 Q0 Q1 1 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 1 0 0 0 0 1 1 1 5 Уравнения для соответствующих выходов шифратора имеют вид: Q0 X 1 * X 2 * ( X 3 * X 4 X 3 * X 4 ) X 1 * X 2 * ( X 3 X 4 ) ; Q1 X 1 * X 3 * ( X 2 * X 4 X 2 * X 4 ) X 1 * X 3 * ( X 2 X 4 ) . Схема, реализующая указанные уравнения имеет вид. X1 Q0 INV X2 AND2 AND2 Q1 INV AND2 AND2 X3 XOR2 INV X4 XOR2 Мультиплексором называется комбинационная схема, имеющая m адресных и 2 m информационных входов, а также один выход, на который подается сигнал с того информационного входа, чей адрес в данный момент присутствует на адресных входах. Рассмотрим мультиплексор на 2 входа X и Y с адресным входом S. Таблица истинности такого устройства имеет вид: X 0 0 1 1 0 0 1 1 Y 0 1 0 1 0 1 0 1 S 0 0 0 0 1 1 1 1 Q 0 0 1 1 0 1 0 1 Этой таблице истинности соответствует следующее уравнение выхода Q S * X S *Y Этому уравнению соответствует схема. 6 U1 1 XN 3 2 U4 1 AND2 3 2 U2 QN 1 YN OR2 3 2 AND2 U3 1 S 2 NOT При добавлении общего разрешающего входа E получим устройство, называемое селектор-мультиплексор. При этом его уравнение примет вид. Q E * (S * X S * Y) Примером подобного устройства может служить микросхема 1533КП7 (74ALS151), представляющая собой селектор-мультиплексор на 8 каналов с общим входом разрешения G. U? 4 3 2 1 15 14 13 12 11 10 9 7 D0 D1 D2 D3 D4 D5 D6 D7 W Y 6 5 A B C G 74151 Демультиплексоры выполняют функцию, обратную мультиплексорам, т.е. производят коммутацию одного информационного входного сигнала на 2 m выходов, где m - число адресных входов. Рассмотрим демультиплексор на 2 выхода. Его таблица истинности имеет вид: X 0 1 0 1 S 0 0 1 1 Q0 0 1 0 0 Q1 0 0 0 1 Этой таблице истинности соответствуют уравнения выходов: Q0 S * X ; Q1 S * X . Этим уравнениям соответствует схема. 7 S Q0 INV X AND2 Q1 AND2 Создадим устройство для суммирования двух двоичных чисел X 1 и X 2 . Опишем закон формирования младшего разряда суммы S 0 и переноса в следующий разряд c1 с помощью таблицы истинности. x10 x 2 0 s0 c1 0 0 1 1 0 1 0 1 0 0 0 1 0 1 1 0 Т.о. получим уравнения для младшего разряда суммы и переноса: s0 x10 * x 20 x10 * x 20 x10 x 20 c1 x10 * x 20 По полученным уравнениям получаем схему т.н. полусумматора. U1 1 X10 3 S0 2 X20 XOR U2 1 3 C1 2 AND2 Обозначим разработанное устройство блоком S0. X0 Y0 S0 S0 C1 Закон формирования любого следующего разряда суммы и разряда переноса в следующий разряд описывается таблицей истинности. x1n x 2 n cn sn cn1 0 0 0 0 0 1 0 1 1 0 0 0 0 1 0 8 0 1 1 1 1 1 0 0 1 1 1 0 1 0 1 0 1 0 0 1 1 0 1 1 1 Т.о. получаем уравнения для произвольного разряда суммы и переноса: sn x1n * x 2n * cn x1n * x 2n * cn x1n * x 2 n * cn x1n * x 2n * cn cn * ( x1n * x 2 n x1n * x 2 n ) cn * ( x1n * x 2 n x1n * x 2 n ) cn * ( x1n x 2 n ) cn * ( x1n x 2n ) cn ( x1n x 2 n ) cn 1 cn * x1n cn * x 2n x1n * x 2n cn * ( x1n x 2n ) x1n * x 2 n cn * ( x1n x 2 n ) x1n * x 2n Т.о. получаем схему суммирования чисел произвольной разрядности. CN XN YN SN S0 S0 U? 1 3 CN+1 2 OR2 Включая параллельно несколько подобных схем можно получить устройство для суммирования произвольного числа разрядов. A[0..N ] S B[0..N ] S[0..N ] Создадим схему, реализующую преобразование прямого кода числа в его дополнительный код. Как извесно для этого необходимо найти обратный код числа и прибавить к нему 1. Схема, вычисляющая обратный код числа описывается уравнением yn xn Эта схема называется “инвертор”. U1 1 XN 2 YN NOT Обозначим это устройство как A[0..N ] I A'[0..N ] 9 Подав на один вход сумматора код с выхода инвертора, а на другой код числа “1”, на выходе сумматора получим дополнительный код числа. A[0..N ] I S "1" D[0..N ] Обозначим это устройство D A[0..N ] D[0..N ] Включив параллельно несколько схем вышеописанного мультиплексора получим мультиплексор на требуемое число разрядов. X[0..N ] Y[0..N ] M Q[0..N ] S Создадим устройство, способное складывать или вычитать два числа, в зависимости от состояния управляющего сигнала c. Для этого необходимо подать на один вход сумматора код одного из чисел, а на другой его вход подать либо прямой либо дополнительный код второго из чисел, в зависимости от состояния управляющего входа c. Такую коммутацию сигналов можно осуществить с помощью мультиплексора. A[0..N] B[0..N] D S M Q[0..N] S Разработанное устройство представляет арифметическо-логического устройсва процессора. собой A[0..N ] B[0..N ] ALU Q[0..N ] S 10 примитивный прообраз