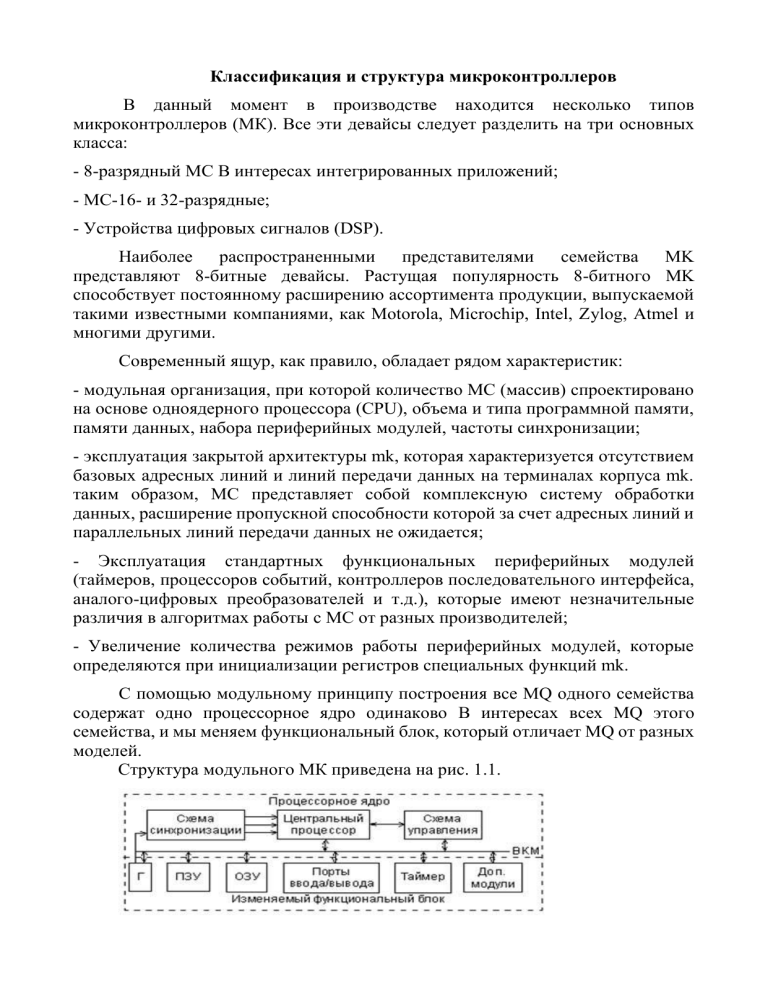

Классификация и структура микроконтроллеров В данный момент в производстве находится несколько типов микроконтроллеров (МК). Все эти девайсы следует разделить на три основных класса: - 8-разрядный MC В интересах интегрированных приложений; - MC-16- и 32-разрядные; - Устройства цифровых сигналов (DSP). Наиболее распространенными представителями семейства MK представляют 8-битные девайсы. Растущая популярность 8-битного MK способствует постоянному расширению ассортимента продукции, выпускаемой такими известными компаниями, как Motorola, Microchip, Intel, Zylog, Atmel и многими другими. Современный ящур, как правило, обладает рядом характеристик: - модульная организация, при которой количество MC (массив) спроектировано на основе одноядерного процессора (CPU), объема и типа программной памяти, памяти данных, набора периферийных модулей, частоты синхронизации; - эксплуатация закрытой архитектуры mk, которая характеризуется отсутствием базовых адресных линий и линий передачи данных на терминалах корпуса mk. таким образом, MC представляет собой комплексную систему обработки данных, расширение пропускной способности которой за счет адресных линий и параллельных линий передачи данных не ожидается; - Эксплуатация стандартных функциональных периферийных модулей (таймеров, процессоров событий, контроллеров последовательного интерфейса, аналого-цифровых преобразователей и т.д.), которые имеют незначительные различия в алгоритмах работы с MC от разных производителей; - Увеличение количества режимов работы периферийных модулей, которые определяются при инициализации регистров специальных функций mk. С помощью модульному принципу построения все MQ одного семейства содержат одно процессорное ядро одинаково В интересах всех MQ этого семейства, и мы меняем функциональный блок, который отличает MQ от разных моделей. Структура модульного МК приведена на рис. 1.1. Рисунок – 1.1 Ядро процессора Состоит в себя: - главный процессор; - внутренняя командная строка (BCM), состоящая из адресных шин, данных и шин управления; - Схема синхронизации МК; - схема управления режимами работы MK, включая поддержку режимов с низким энергопотреблением, начальный запуск (сброс) и т.д. Изменяемая функциональная единица Состоит в себя - модули памяти различных типов и объемов, - порты ввода / вывода, - Модули тактового генератора (G), - Таймер. В интересах относительно простых MCS модуль управления прерываниями является частью ядра процессора. В более сложных МК есть отдельный модуль с разработанными функциями. Сменный функциональный блок также может включать дополнительные модули, такие как компараторы напряжения, аналого-цифровые преобразователи (АЦП) и другие. Каждый модуль предназначен В интересах работы в рамках MK с учетом протокола VCM. Такой подход позволяет создавать MCS различной структуры в одном семействе. Структура процессорного ядра Главными характеристиками, определяющими процессорного ядра MK, представляют: производительность - набор записей В интересах хранения промежуточных данных; - система команд центрального процессора; - способы адресации операндов в памяти; - Организация процессов сканирования и выполнения заказа. С точки зрения системы управления и того, как обращаться к операнду, ядро процессора является одним из двух принципов построения процессора: - Устройства с архитектурой CISC, реализующие так называемый Компьютерный сложный набор инструкций (Компьютер со сложным набором инструкций; - Устройства с архитектурой RISC, которые реализуют компьютерную систему с уменьшенным набором команд (Компьютер с уменьшенным набором команд). Устройства CISC выполняют большой набор команд с расширенными возследуетстями адресации, с целью дать разработчику возследуетсть выбрать наиболее подходящую команду В интересах выполнения требуемой операции. Прием команды на выполнение осуществляется в течение нескольких рабочих циклов на байт. Время выполнения заказа может варьироваться от 1 до 12 циклов. Однако система управления, как правило, не является ортогональной, то есть не все команды могут использовать один из методов адресации В интересах одного из регистров процессора. Среди MP с архитектурой CISC есть MP компании Intel, MP семейств NS05, NS08 и NS11 компании Motorola и ряд других. В интересах процессоров с архитектурой RISC набор выполняемых команд сведен к минимуму. В интересах выполнения более сложных операций необходимо комбинировать команды. В этом случае все команды имеют формат фиксированной длины (например, 12 -, 14- или 16-битный), который извлекает команду из памяти и выполняется за один час (час) синхронизации. Система управления процессором RISC предполагает, что все регистры процессора могут использоваться на равной основе. Это обеспечивает дополнительную гибкость в ряде операций. MK с процессором RISC Состоит в себя MK AVR от Atmel, MK PIC16 и PIC17 от microchip и другие. В целом, Устройства RISC обладают более высокой производительностью, чем CISC MP, при той же внутренней тактовой частоте магистрали. Однако на практике неоднозначным и неясным. вопрос оценки эффективности является Во-первых, оценка производительности MK по времени выполнения команд разных систем (RISC и CISC) не совсем точна. Обычно производительность MP и MK оценивается по количеству операций передачи от журнала к журналу, которые могут быть выполнены за одну секунду. В MK с процессором CISC время выполнения операции реестра в реестре составляет 1-3 цикла, что, по-видимому, ниже производительности MK с процессором RISC. Однако стремление уменьшить формат управления при сохранении ортогональности системы управления RISC приводит к вынужденному ограничению количества регистров, доступных в одной команде. Следовательно, операция по переносу содержимого одного из доступных регистров в другой (не источник операнда и не рабочий) требует использования двух команд. Эта необходимость часто возникает, когда содержимое одного из регистров общего назначения (RHN) передается на один из портов MC. В то же время большинство процессоров CISC имеют команды В интересах передачи содержимого RON на один из портов ввода-вывода системы управления. То есть более сложная система управления иногда позволяет реализовать более эффективный метод выполнения операции. Во-вторых, оценка производительности МК по скорости передачи "логлог" не учитывает специфику реализованного конкретного алгоритма управления. Таким образом, при разработке быстродействующих автоматизированных устройств управления акцент следует делать на синхронизации умножения и деления при реализации уравнений различных функций преобразования. Поэтому в критических ситуациях, требующих высокой производительности, следует оценить производительность ряда операций, которые в основном используются в алгоритме управления и имеют ограничения на выполнение. В-третьих, следует также учитывать, что частоты синхронизации, указанные в справочных данных на MK, обычно соответствуют частоте подключенного кварцевого резонатора, в то время как время цикла процессора определяется частотой обмена в соответствии с DCM. Соотношение этих частот индивидуально В интересах каждого МК и должно приниматься во внимание при сравнении производительности различных моделей контроллеров. Что касается организации процессов выборки и выполнения заказов, то в современных MP используется одна из двух уже упомянутых архитектур: - фон Нейман (Принстон); - Гарвард. Основной особенностью фоновой архитектуры Neuman является эксплуатация освобожденной памяти В интересах хранения программ и данных, как показано на рисунке. 1.2. Главным преимуществом архитектуры Фон Неймана является упрощение девайсы MP, поскольку доступна только обычная память. Кроме того, эксплуатация единой области памяти позволило быстро перераспределять ресурсы между областями программ и данных, что значительно повысило гибкость приложений с точки зрения разработчика программного обеспечения. С помощью размещению стека в общей памяти был облегчен доступ к его содержимому. Неслучайно архитектура фон Неймана стала основной архитектурой универсальных компьютеров, в том числе персональных. Главной особенностью архитектуры Гарварда является эксплуатация специальных адресных пространств В интересах хранения команд и данных, как показано на рисунке. 1.3. Рисунок - 1.2 Рисунок - 1.3 Рисунок 1.2 – Структура МПС с фон-неймановской архитектурой Рисунок 1.3 – Структура МПС с гарвардской архитектурой Структура и порядок функционирования процессора Процессор обычно представляет собой отдельный чип или часть чипа (в случае микроконтроллера). Чип процессора должен иметь следующие результаты: - адреса автобусов, - Шина данных - проверьте автобусы. - вывод внешнего тактового сигнала или кварцевого резонатора (CLK), поскольку процессор всегда является заблокированным устройством. - вывод исходного сброса сигнала сброса. Когда питание включено в случае чрезвычайной ситуации или сбой процессора, подача этого сигнала вызывает запуск процессора и заставляет его запустить начальную программу запуска. - Шина питания-обычно имеет напряжение питания (+5 В или + 3,3 В) и общую линию ("заземление"). Иногда несколько сигналов и шина умножаются, с целью уменьшить количество контактов микросхемы процессора. Основные функции процессора: - битовая глубина шины данных определяет скорость работы системы; - битовая глубина адресной шины определяет допустимую сложность системы; - количество управляющих сигналов на шине управления; определяет разнообразие режимов замены и эффективность замены процессора другими системными девайсыми. Чем выше тактовая частота процессора, тем быстрее он работает, тем быстрее выполняется команда. Однако производительность процессора определяется не только тактовой частотой, но и особенностями его структуры. Современные Устройства выполняют большинство команд за один такт и имеют инструменты, необходимые В интересах параллельного выполнения нескольких команд. Тактовая частота процессора имеет нижний и верхний пределы. Когда превышен верхний предел частоты, процессор может перегреться и выйти из строя, и, самое главное, они не всегда происходят нерегулярно. Поэтому вы должны быть очень осторожны с изменением этой частоты. После активации процессор переходит на первый адрес программы запуска и запускает эту программу. Эта программа предварительно записана в постоянную (энергонезависимую) память. После завершения начальной загрузки процессор начинает запускать основную программу в постоянной памяти или оперативной памяти, В интересах которой он, в свою очередь, выбирает все команды. Процессор может отвлекаться от этой программы из-за внешних сбоев или запросов PDP. Процессор выбирает команды памяти, используя циклы воспроизведения вдоль ствола. При необходимости процессор записывает данные в память или девайсы ввода - вывода с эксплуатациям циклов записи или считывает данные из памяти или устройств ввода-вывода с эксплуатациям циклов чтения. Таким образом, основные функции процессора заключаются в следующем: - выбор (воспроизведение) выполняемых команд; - ввод данных (считывание) из памяти или девайсы ввода-вывода; - Вывод (запись) в память или девайсы ввода-вывода; - обработка данных (операнд), включая арифметические операции; - Адресация памяти, то есть адрес памяти, с которой осуществляется обмен данными; Упрощенная конструкция микропроцессора может быть представлена следующим образом. Ниже перечислены основные функции узлов ЦП. Схема управления выбором команд считывает команды из памяти и расшифровывает их. В ранних микропроцессорах было невозследует одновременно выполнить предыдущую и следующую команды, поскольку процессор не мог комбинировать эти операции. Современные Устройства используют конвейер команд( очередь), который позволяет выбирать несколько будущих команд при выполнении предыдущей. Конвейер представляет собой небольшую внутреннюю память процессора, в которую в наименьшем случае (при запуске внешней шины) записывается несколько команд после исполняемого файла. Эти процессы работают параллельно, что ускоряет работу процессоров. Однако, если вы запустите команду В интересах перехода в следующую ячейку памяти и на пульт дистанционного управления (с меньшим или большим адресом), конвейер не будет полезен и должен быть сброшен. Идея конвейера заключалась в том, с целью использовать внутренний кэш процессора, заполненный командами и данными В интересах обработки, пока процессор был занят выполнением предыдущих команд. Чем больше кэшпамять, тем меньше вероятность того, что ее содержимое будет очищено при выполнении команды перехода. Процессор может обрабатывать команды во внутренней памяти намного быстрее, чем во внешней памяти. Кэш-память также может хранить обрабатываемые данные, что также ускоряет процесс. Вычислительный блок (ALU или ALU) предназначен В интересах обработки информации на основе команды, полученной процессором. Примерами обработки могут быть логические операции (например, логические "и", "или", "эксклюзивные или" и т. д.), То есть операции битирования над операндом, а также арифметические операции (такие как сложение, вычитание, умножение, деление и т. д.). Производительность ALU в основном определяет производительность процессора. Кроме того, это зависит не только от тактовой частоты, с которой укладывается алюминий, но и от количества циклов, необходимых В интересах выполнения конкретной команды. С целью повысить производительность, разработчики пытаются перевести время работы команды в такт и обеспечить, с целью ALU работал с максимально возследуетй частотой. Один из способов решить эту проблему - уменьшить количество инструкций, выполняемых процессором ALU (называемым процессорами RISC). Еще один способ повысить производительность процессора - использовать несколько ALU, работающих параллельно. В интересах операций с числами с плавающей запятой и других специальных сложных операций используются специальные калькуляторыматематические соУстройства,входящие в состав структуры МП. Схема управления прерываниями обрабатывает запрос на прерывание, полученный процессором, определяет начальный адрес программы прерывания( векторный адрес прерывания), обеспечивает переход на эту программу после выполнения текущей команды и записывает текущее состояние журналов процессора в память (в стек). По завершении программы прерывания процессор возвращается в программу прерывания с восстановленными значениями регистров внутренней памяти (стека). Схема управления прямым доступом к памяти используется В интересах временного отключения процессора от внешних шин и В интересах отключения процессора при одновременном предоставлении прямого доступа к устройству, которое запрашивает его. Управляющая логика организует взаимодействие всех узлов ЦП, перенаправляет данные, синхронизирует работу ЦП с внешними сигналами и реализует процедуры ввода и вывода информации. Регистры ЦП - это, по сути, очень быстрые ячейки памяти, предназначенные В интересах временного хранения разных кодов: данных, адресов, служебных кодов. Операции с этими кодами выполняются чрезвычайно быстро, поэтому, как правило, чем больше внутренних регистров, тем лучше. На производительность процессора сильно влияет битовая глубина регистров. Это битность регистров и ALU, называемая внутренней битностью процессора, которая может не совпадать с внешней битностью. Существует два основных подхода к достижению цели внутренней регистрации. Например, за первым следует Intel, которая назначает каждому реестру четко определенную функцию. Это, с одной стороны, упрощает организацию процессора и сокращает время выполнения команды, но, с другой стороны, снижает гибкость и иногда замеВ интересахет работу программы. Например, некоторые арифметические операции и некоторые обмены с девайсыми ввода - вывода выполняются только на одном диске реестра, что может потребовать дополнительной передачи между реестрами при выполнении определенных процедур. Второй подход заключается в том, с целью сделать все (или почти все) регистры одинаковыми, например, на двух 16-разрядных процессорах t-11. в этом случае достигается большая гибкость, но необходимо усложнить структуру процессора. Существуют также промежуточные решения, особенно на процессоре Motorola mc68000, половина регистров использовалась В интересах данных, и они были взаимозаменяемыми, другая половина-В интересах адресов, и они также взаимозаменяемы. Внутренние регистры микропроцессора обязательно выполняют две служебные функции: - определите адрес в памяти, где находится выполняемая команда (счетчик команд или функция указателя команды); - определите текущий адрес стека (функция указателя стека). В разных процессорах каждой из этих функций может быть назначен один или два внутренних регистра. Эти два показателя отличаются от других не только своей конкретной целью,полезностью, системой, но и особым способом изменения содержания. Содержимое программы может быть изменено только в случае чрезвычайной ситуации, поскольку любая ошибка может помешать работе компьютера, засорить и повредить содержимое памяти. Содержимое индикатора управления (счетчика) изменяется следующим образом. При запуске системы (при включении) установленное значение сохраняется раз и навсегда. Это первый адрес передатчика. После того, как все остальные команды будут введены в память, значение указателя команды автоматически увеличивается (увеличивается) на один (или два, в зависимости от формата команды и типа процессора). То есть следующая команда выбирается в следующем порядке адреса памяти. Если вы передаете-выполняете команды, которые предотвращают повторение адресов памяти в дальнейшем, в командный указатель будет записано новое значение-новый адрес в памяти, с которого команды будут передаваться снова одна за другой. Такое же изменение содержимого командного указателя происходит при вызове и возврате процедуры или при запуске и прерывании обработки прерываний. Журнал состояния содержит слово В интересах состояния процессора (PSEMOUTH, PSONLINE-это слово В интересах состояния процессора). Каждый бит этого слова (флага) содержит информацию о результатах предыдущей команды. Эти фрагменты (флаги) используются командами условного перехода. Один и тот же регистр иногда содержит контрольные индикаторы, которые определяют выполнение определенных команд. Следовательно, во время работы процессора модель образца команды последовательно выбирает команды из памяти, затем эти команды выполняются, и при необходимости обработка данных подключается к ALU. Входы ALU могут питаться либо из памяти, либо из внутренних регистров. Внутренние регистры также хранят в памяти коды адресов обрабатываемых данных. Результат обработки ALU изменяет статус регистра маркировки и записывается во внутренний регистр или в память (источник данных и получатель указаны в номере заказа). При необходимости материал может быть записана из памяти (или девайсы ввода-вывода) во внутренний реестр или из внутреннего реестра в память (или устройство ввода-вывода). Список использованных источников 1) https://ru.wikipedia.org/wiki/%D0%97%D0%B0%D0%B3%D0%BB%D0%B0%D0 %B2%D0%BD%D0%B0%D1%8F_%D1%81%D1%82%D1%80%D0%B0%D0%B D%D0%B8%D1%86%D0%B0 2) https://ru.wikipedia.org/wiki/%D0%92%D1%8B%D1%87%D0%B8%D1%81%D0% BB%D0%B8%D1%82%D0%B5%D0%BB%D1%8C%D0%BD%D0%B0%D1%8F_ %D0%BC%D0%B0%D1%88%D0%B8%D0%BD%D0%B0 3) https://library.bsuir.by/ 4) https://libeldoc.bsuir.by/handle/123456789/27728 5) http://techn.sstu.ru/kafedri/%D0%BF%D0%BE%D0%B4%D1%80%D0%B0%D0% B7%D0%B4%D0%B5%D0%BB%D0%B5%D0%BD%D0%B8%D1%8F/1/MetMat/ shaturn/inform/%D0%9B%D0%B5%D0%BA%D1%86%D0%B8%D1%8F%206%5 C%D0%9B%D0%B5%D0%BA%D1%86%D0%B8%D1%8F%206.htm 6) https://tproger.ru/explain/how-cpu-works/ 7) http://www.morepc.ru/processor/articles.html