Ю.В. КАТУНИН Научный руководитель – В.Я. СТЕНИН, д.т.н

advertisement

Ю.В. КАТУНИН

Научный руководитель – В.Я. СТЕНИН, д.т.н., профессор

Национальный исследовательский ядерный университет «МИФИ»

КОМБИНИРОВАНИЕ ДВУХФАЗНЫХ ЭЛЕМЕНТОВ И

ДУБЛИРОВАННОЙ ТРАДИЦИОННОЙ ЛОГИКИ В СХЕМАХ

УПРАВЛЕНИЯ ДВУХФАЗНЫМ ТРИГГЕРОМ-ЗАЩЕЛКОЙ

DICE

Обоснована возможность частичной замены двухфазных комбинационных

элементов, характеризующихся повышенной помехоустойчивостью, дублированной обычной логикой при условии наличия хотя бы одного двухфазного элемента

перед входом D триггера

Неизменным для всех проектным норм остается требование, предъявляемое к двухфазным элементам в части пространственного разнесения

их дифференциальных частей на расстояние не менее 1.5…2.0 мкм. Постоянная времени переходного процесса в линии межсоединений постоянной длины обратно пропорциональна произведению значений толщины

линии металлизации и толщины межслойного диэлектрика [1]. Поэтому

при проектных нормах 28 нм ожидается существенное ухудшение быстродействия схем на двухфазной логике.

UИ.П

UИ.П

B

UИ.П

A

0.8

K1

K5 QB1

K3

K7

UИ.П

UИ.П

UИ.П

K2

K4

K6

QB2

K8

UВХ.D2, В

0.6

2.0

0.4

CВЫХ/CДИФ = 0.5

GP/GN

Перезапись "0" ■ 2.0

▲ 1.0

♦ 0.5

0.2

0.0

0.0

CLK2

CLK1

D2

D1

Q2

Q1

а)

Запись "1"

1.0

0.2

0.4 0.6

UВХ.D1, В

0.8

б)

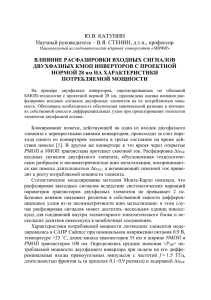

Рис. 1. Двухфазный триггер-защелка DICE: а) схема; б) переключательная характеристика в исходном состоянии “0”

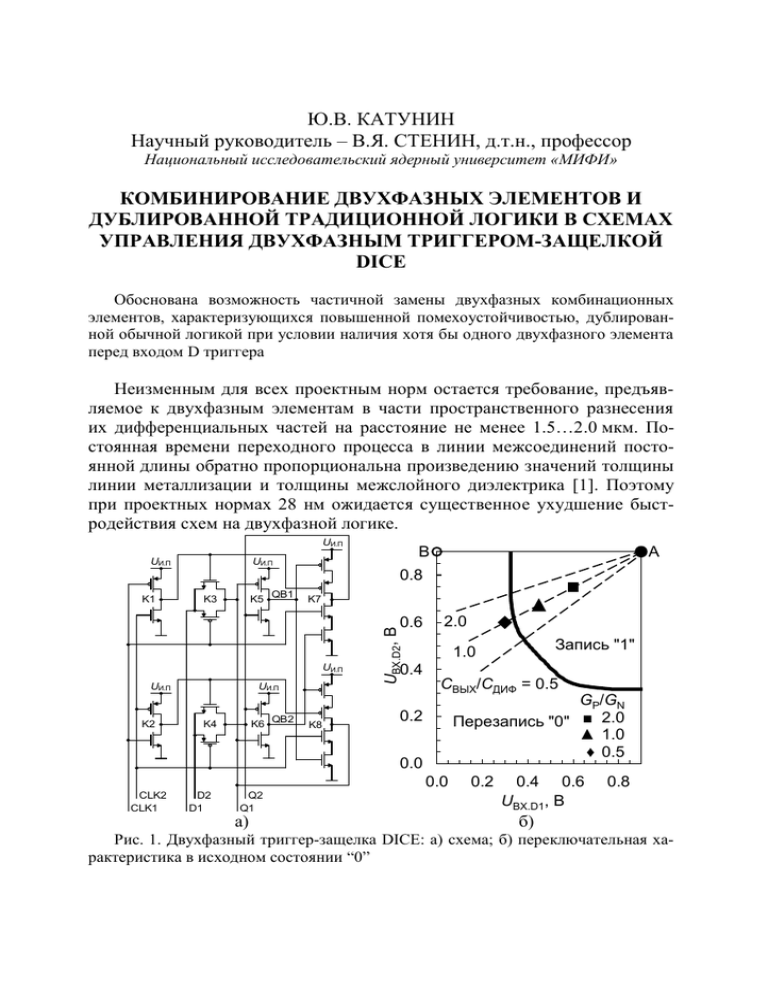

Решение указанной проблемы предполагается заменой части двухфазных элементов комбинационной схемы их однофазными дублируемыми

аналогами. На рис. 1а представлена схема распространенного двухфазного триггера-защелки DICE, а на рис. 1б – его переключательная характеристика в исходном состоянии “0”, представляющая две области точек

(UВХ.D1; UВХ.D2), в одной из которых происходит перезапись исходного

состояния (“0”), а другой – запись нового состояния (“1”), и полученная с

использованием svt-моделей транзисторов объемной КМОП-технологии с

длиной канала 30 нм в угле tt при температуре 25 °С.

Если данные подаются на входы триггера с продублированной цепочки однофазных комбинационных элементов, то распространяющаяся в

одной из цепочек помеха, дойдя до входа триггера-защелки, вызовет сбой

записи данных (смещение из точки A в точку B). Наличие же двухфазного

элемента перед входами данных триггера в случае импульса помехи на

одном из его входов приводит к смещению точки входных сигналов триггера из точки А по одной из семейства прямых, определяемого системой

уравнений, полученной на основе выражений, представленных в [2]:

𝑈ВХ.D1 = 𝑈И.П (1 –

1

(1 +

),

(1)

1

𝑈ВХ.D2 = 𝑈И.П (1 –

{

𝐺P

)

𝐺N

(1 +

),

𝐺P

𝐶

) (1 + ВЫХ )

𝐺N

𝐶ДИФ

где CВЫХ – собственная емкость выходного узла двухфазного элемента,

CДИФ – емкость связи дифференциальных выходов двухфазного элемента,

а GP и GN – соответственно, проводимости плеча PМОП и плеча NМОП

транзисторов, которые оказываются открытыми при воздействии помехи

на один из входов двухфазного элемента.

При замене двухфазной логики дублированной однофазной следует

использовать в качестве фильтра импульсов помехи (SET) хотя бы один

двухфазный элемент перед входом данных триггера-защелки DICE.

Работа проводилась в рамках гранта РФФИ № 14-29-09284.

Список литературы

1.

Meindl J.D. Beyond Moore's Law: the interconnect era // Computing in Science & Engineering. 2003. Vol. 5. № 1. P. 20–24.

2.

Катунин Ю.В., Стенин В.Я. Двухфазный 28 нм КМОП инвертор как элемент повышенной помехоустойчивости к эффектам воздействия одиночных ядерных частиц // Вестник

Национального исследовательского ядерного университета «МИФИ». 2014. Т.2. — №5. C.

363–370.