Теория сигналов и систем Алгоритм уменьшения тока утечки КМОП интегральных схем

advertisement

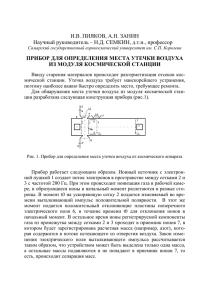

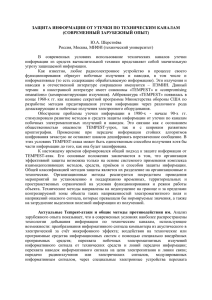

Теория сигналов и систем 89 Теория сигналов и систем УДК 621.3.049.771 А.В. Матевосян Алгоритм уменьшения тока утечки КМОП интегральных схем управлением входного вектора Масштабирование КМОП интегральных схем привело к резкому росту тока утечки. Одним из способов уменьшения тока утечки схемы в режиме ожидания является метод управления входным вектором. Сущность которого заключается в поиске вектора минимальной утечки (ВМУ), подающейся на вход схемы в режиме ожидания. Предлагается алгоритм поиска вектора минимальной утечки, который выполняется приблизительно в 5 раз быстрее, чем классический алгоритм поиска ВМУ. With leakage power being no longer negligible, it becomes a critical problem for low power design. Input vector control is an effective method to reduce leakage power when a circuit enters sleep mode. It seeks to find a vector that minimizes leakage power (minimum leakage vector) to be statically applied to the primary inputs of a circuit. Algorithm of searching minimum leakage vector which can accelerate calculation about 5 times comparing with conventional algorithm is presented in this paper. Введение Растущий спрос на мобильные вычислительные приборы и беспроводные системы связи привели к тому, что снижение мощности рассеяния стало главным требованием при разработке интегральных схем(ИС) [1]. В КМОП ИС потребляемая мощность состоит из двух компонент: динамической и утечки. В схемах с высоким напряжением питания можно использовать транзисторы с относительно большими пороговыми напряжениями с тем, чтобы уменьшить подпороговый ток утечки. Однако, приложения с низким энергопотреблением постоянно требуют понижения напряжения питания. Масштабирование порогового напряжения приводит к значительному увеличению мощности утечки из-за экспоненциального роста подпорогового тока утечки. Показано, что при 90нм-овых размерах мощность утечки может занимать до 40%-ов от общей мощности [2]. Одним из способов уменьшения тока утечки схемы в режиме ожидания(отключения) является так называемый метод управления входным вектором(УВВ). Сущность метода УВВ заключается в поиске вектора минимальной утечки(ВМУ), подающейся на вход схемы в режиме ожидания. Из-за экспоненциального характера поиска ВМУ[4] для больших схем найти глобальный минимум невозможно. Однако, можно найти вектор близкий к ВМУ. Состояние вопроса Предложенный в [3] метод УВВ легко реализуемый и более эффективен с точки зрения уменьшения тока утечки по сравнению с другими методами: отключением питания или увеличения порогового напряжения [10]. Метод УВВ можно ипользовать совместно с методом отключения синхросигнала в режиме ожидания [10]. В этом режиме значения регистров меняются на ВМУ и комбинационные схемы, связанные с этими регистрами, будут находиться в состоянии низкого энергопотребления. Из-за эффекта взаимодействия транзисторов [4], ток утечки схемы находится в зависимости от входной комбинации сигналов [5]. Например, КМОП логические элементы проявляют изменение тока утечки в зависимости от входного сигнала. Как показано в табл. 1 [9], соотношение значений мощности утечки при разных входных комбинациях может достигнуть до 6-и. Таблица 1. Мощность утечки для элемента И-НЕ2 Входной вектор Мощность утечки(пВт) 00 390 01 2300 10 1850 10 480 Выполнение исчерпывающего моделирования всех входных векторов для поиска ВМУ в случае больших схем непрактично. Альтернативным решением может стать поиск ВМУ моделированием не всех векторов, а подмножества предварительно выбранных векторов. Экспериментальные результаты показывают, что большинство гистограмм распределения мощности утечки соответствуют нормальному закону распределения. Например, гистограммы для схем C2670 и C5315 из ряда ISCAS85 приведены на рис.1, для результатов моделирования на 10000 векторах. 90 Электроника и связь. Тематический выпуск «Электроника и нанотехнологии», ч.1, 2009 Рис. 1. Гистограммы мощности утечки схем C2670 и C5315 Минимальная мощность утечки (при ВМУ) равняется 681725пВт, а максимальная 788393пВт для C2670. Для C5315 максимальная мощность больше минимальной в 1,13 раз. Эти распределения очень близки к нормальному закону распределения. Известны многие методы [6, 7, 8] уменьшения числа векторов моделирования подбором правильного множества векторов. Экспериментальные данные показывают, что эти методы могут значительно уменьшить мощность утечки. Однако, они пока еще очень медленны, особенно для схем с большим числом элементов. Предлагаемый метод Как уже было изложено, алгоритмы поиска ВМУ достаточно медленны. Улучшение метода можно достигнуть уменьшением размера схемы. Схема разбивается на подсхемы. В алгоритме поиска вектора одна из подсхем выбирается для оценки мощности утечки всей схемы. Ключевой частью предлагаемого метода является правило разделения схемы на подсхемы. Входные векторы могут легко контролировать узлы, близкие к основным входам. Более глубокие узлы контролировать труднее. Элементы с легко контролируемыми входами могут сформировать подсхему. Можно предположить, что вектор, минимизирующий утечку этой подсхемы, уменьшит этот же показатель всей схемы. Основываясь на этом предположении, для поиска ВМУ моножество векторов может быть промоделировано на подсхеме с меньшим временем моделирования. Для разбиения схемы на подсхемы определяется номер уровня схемы (НУ). НУ эелементов, связанных с первичными входами, равня- ется 1. НУ элемента равняется x+1, если данный элемент связан с элементом, НУ которого равен x. Если элемент связан с несколькими элеметами с разными значениями x, то из них выбирается максимальный. Как видно из рис.2, вся схема разбита на две части: передняя черная и задняя белая части. Передняя часть (Спод) может быть выбрана для представления всей схемы с целью уменьшения вычислений. Для формирования Спод предлагается следующий алгоритм: Быстрый алгоритм поиска ВМУ, основанный на НУ Входные переменные: Схема С и множество векторов МВ. Выходные переменные: ВМУ Шаг 1: Моделирование С случайным подмножеством МВсл_под из множества МВ для получения ВМУсл_под для МВсл_под. Шаг 2: Определение НУ каждого элемента схемы С по его связям. Шаг 3: Установление i=1. Шаг 4: Формирование подсхемы Спод элементами, НУ которых не больше i. Шаг 5: Моделирование подсхемы Спод случайным подмножеством МВсл_под для получения тока утечки подсхемы Спод. Шаг 6: Моделирование подсхемы Спод вектором ВМУсл_под (полученном на шаге 1) для получения мощности Мпсевд. Если Мпсевд не меньше, чем большинство значений, полученных другими векторами множества МВсл_под, то увеличение i=i+1 и переход к шагу 4. Шаг 7: Моделировние подсхемы Спод множеством МВ с целью получения мощности Теория сигналов и систем 91 Рис. 2. Разбиение схемы на подсхемы, основываясь на НУ утечки. Формирование подмножества векторов МВпод из векторов, при которых мощность утечки минимальная, до заполнени МВпод (размер МВпод выбирается во много раз меньше размера МВ). Шаг 8: Моделирование схемы С подмножеством МВпод с целью получения минимальной мощности утечки и ВМУ. Шаг 9: Конец. Экспериментальные результаты Для оценки производительности алгоритма проведены эксперименты на вычислительной системе - Intel Core Duo 1.7GHz, 1Gb с операционной системой Widnows XP. Экспериментальные результаты получены на 7-и схемах серии ISCAS85. Каждый из этих комбинационных схем был просинтезирован при помощи программного инструмента автоматического синтеза цифровых схем Design Compiler[11] компании Synopsys, с использованием библотеки стандартных цифровых ячеек SAED90nm_CORE[9]. С целью получения объективной картины, для всех 7-и схем было сгенерировано случайное множество МВ из 10000 векторов. Размеры МВсл_под и МВпод выбраны соответственно 1000 и 100. Результаты моделирования приведены в табл. 2. Таблица 2. Результаты моделирования Схема C432 C1355 C2670 C3540 C5315 C6288 C7552 Количество элеЧисло ментов первичных Подвходов Всего схемы 36 41 233 50 178 32 207 216 590 1400 1983 1379 2416 3557 45 40 651 177 180 256 795 НУ Время выполнения Всего Подсхемы Класический алгоритм 29 27 38 52 31 124 42 2 1 8 2 1 1 5 13 53 174 310 270 418 1092 Предложенный алгоритм 2,4 8,8 95,1 46,1 48,7 84,98 135,1 Ускорение 5,3 6,0 1,8 6,7 5,5 4,9 8,1 92 Электроника и связь. Тематический выпуск «Электроника и нанотехнологии», ч.1, 2009 Из-за незначительности коэффициента ошибки между классическим и предложенным алгоритмами он не приведен в таблице 2. Как видно из таблицы 2, с целью поиска ВМУ, незначительная часть схемы может представлять всю схему. Ускорение выполнения алгоритма в среднем равна 5,5, т.е. с точки зрения времени выполнения предложенный алгоритм эфективнее, по сравнению с классическим алгоритмом поиска ВМУ. Литература 1. K. Roy and S. C. Prasad. Low-Power CMOS VLSI Circuit Design. // New York: Wiley, 2000. – P. 1–35 2. J. Kao, S. Narendra, A. Chandrakasan. Subthreshold leakage modeling and reduction techniques // ICCAD, 2002. – P. 141–148. 3. J.P. Halter, F. Najm. A gate-level leakage power reduction method for ultra low-power CMOS circuits. // Custom Integrated Circuits Conference, 1997. – P. 475–478. 4. M.C. Johnson, D. Somasekhar, K. Roy. Leakage control with efficient use of transistor stacks in single threshold CMOS. // Proceedings of the 36th DAC, 1999. – P. 442–445. 5. S. Bobba, I.N. Hajj.; Maximum leakage power estimation for CMOS circuits // Low-Power Design, 1999. – P. 116–124. 6. E. Jeffrey, J. Joshua. Fast Algorithms for Leakage Reduction Using Input Vector Control // Energy-Aware Computing, 2003. – P. 14–18. 7. F. A. Aloul, S. Hassoun, K. A. Sakallah, D. Blaauw, Robust SAT-Based Search Algorithm for Leakage Power Reduction // Proceedings of the 12th International Workshop on Integrated Circuit Design. 2002. – P. 167–177. 8. Z. Chen, M. Johnson, L. Wei; W. Roy ; Estimation of standby leakage power in CMOS circuit considering accurate modeling of transistor stacks. // Low Power Electronics and Design, 1998. – P. 239–244. 9. SAED90nm Standard Cell Library Databook. 10. S. Henzler, Power management of digital circuits in deep sub-micron technologies. // Munich: Springer, 2007. – P. 49–82 11. Synopsys Inc. Design Compiler Reference Manual. Version 2007.