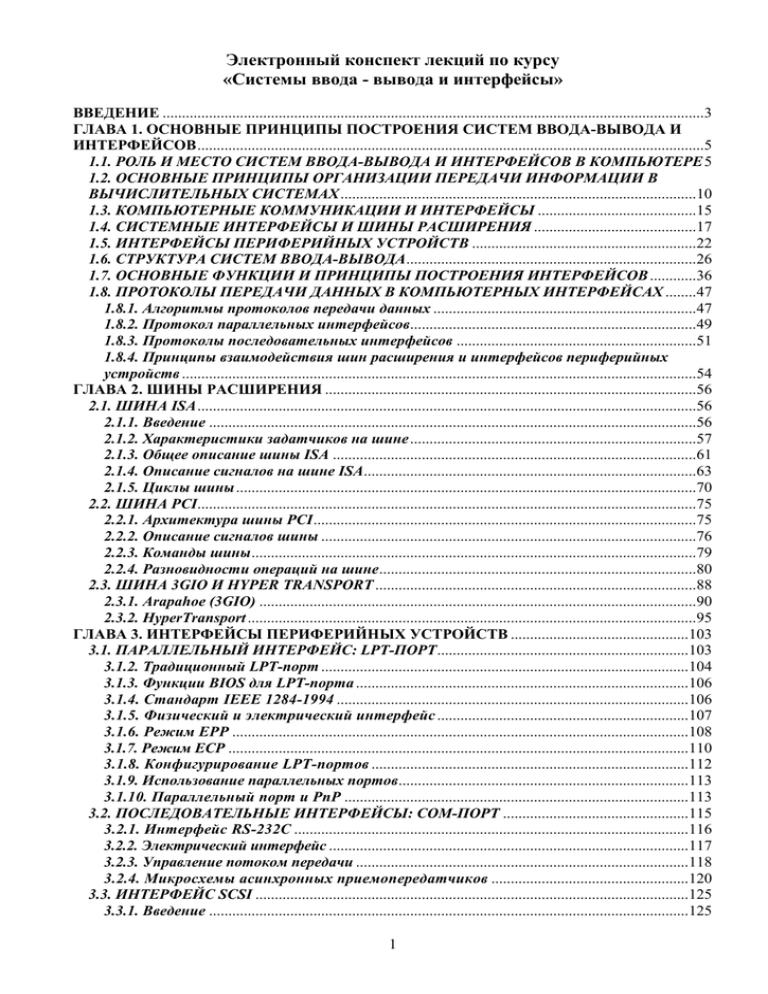

Электронный конспект лекций по курсу

advertisement