Шпоры_4_с_оглавлением

advertisement

Оглавление

1.Классификация параллельных КС по структурно-функциональным признакам. ...............3

2.Классификация параллельных КС по функциональным возможностям КС с точки зрения

пользователя...................................................................................................................................5

3.Проведите сравнительный анализ классификаций компьютерных систем. .........................5

4.Мультикомпьютеры, кластеры и симметричные мультипроцессоры общая

характеристика, схемы построения, особенности каждой из систем, области применения. 6

5.Системы с распределенной и разделяемой памятью, массово-параллельные системы

общая характеристика, схема построения, особенности каждой из систем, области

применения.....................................................................................................................................8

6. Структура, достоинства и недостатки UMA-, NUMA- и ccNUMA-систем ........................9

6.1.Масштабируемая архитектура. Что понимается под словами «масштабируемость

кластера»? .....................................................................................................................................11

6.2.Архитектуры S2MP и NUMA-flex как развитие архитектуры ccNUMA ...........................12

7.Основные понятия теории моделирования параллельных КС. Методы моделирования

параллельных КС. ........................................................................................................................13

8.Задачи моделирования параллельных КС. .............................................................................13

9.Приведите основные принципы моделирования...................................................................13

10.Моделирование параллельных процессов. Применение аппарата сетей Петри.

Подклассы и расширение сетей Петри. .....................................................................................14

?11.Применение сетей Петри для синтеза дискретных управляющих устройств. ...............15

12.Оценочные или Е-сети как расширение сетей Петри .........................................................18

12.1.Моделирование конвейерной обработки информации ....................................................19

13.Свойства-Задачи сохранения и активности сети Петри .....................................................20

13.1.Моделирование сетями Петри вычислительных процессов в КС, использующих

кратные функциональные блоки. ...............................................................................................23

14.Задачи достижимости и покрываемости сети Петри. .........................................................25

15.Свойства-Задача безопасности и ограниченности сети Петри. .........................................26

15.1Моделирование сетями Петри задач синхронизации при взаимодействии процессов в

КС ..................................................................................................................................................27

18.Анализ сетей Петри матричным методом ............................................................................30

19.Матричный метод анализа сетей Петри достоинства и недостатки метода .....................30

Границы возможности моделирования с помощью сетей Петри ...........................................31

23.Сети Петри и их особенности ...............................................................................................32

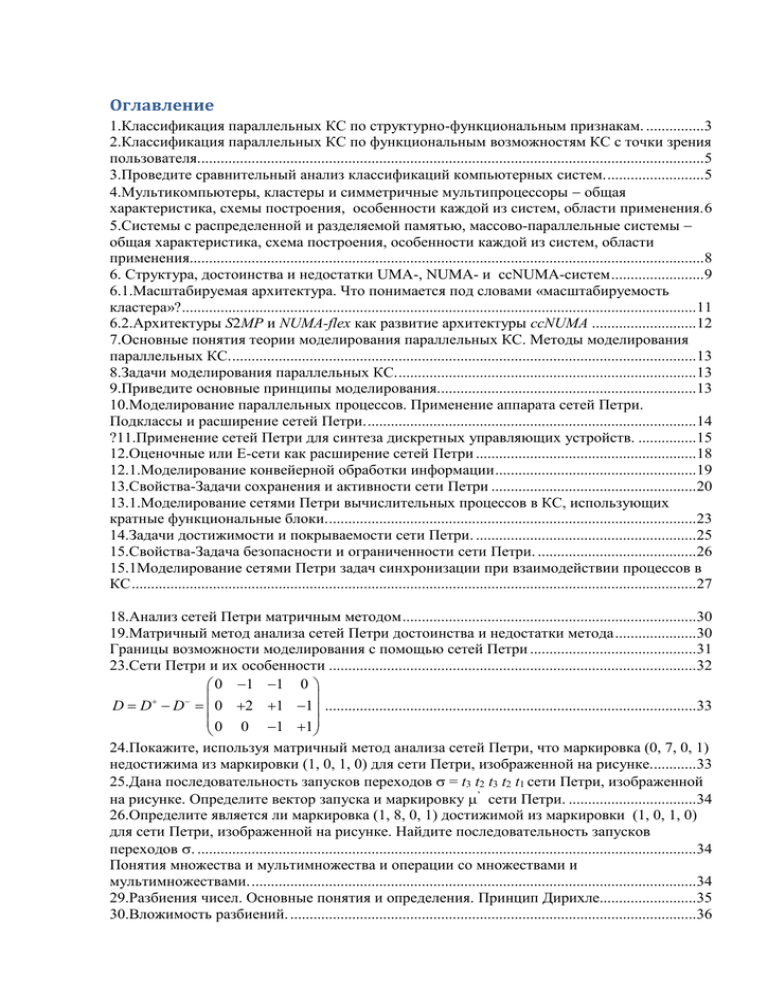

0 1 1 0

D D D 0 2 1 1 ................................................................................................33

0 0 1 1

24.Покажите, используя матричный метод анализа сетей Петри, что маркировка (0, 7, 0, 1)

недостижима из маркировки (1, 0, 1, 0) для сети Петри, изображенной на рисунке............33

25.Дана последовательность запусков переходов = t3 t2 t3 t2 t1 сети Петри, изображенной

на рисунке. Определите вектор запуска и маркировку ’ сети Петри. .................................34

26.Определите является ли маркировка (1, 8, 0, 1) достижимой из маркировки (1, 0, 1, 0)

для сети Петри, изображенной на рисунке. Найдите последовательность запусков

переходов . .................................................................................................................................34

Понятия множества и мультимножества и операции со множествами и

мультимножествами. ...................................................................................................................34

29.Разбиения чисел. Основные понятия и определения. Принцип Дирихле.........................35

30.Вложимость разбиений. .........................................................................................................36

31.Ранговое условие вложимости; пример использования. ...................................................37

32.Принцип полного размещения; пример использования. ....................................................37

33.Вложимость с ограничениями; пример использования. .....................................................37

Особенностью распределения памяти в КС с сегментной организацией программ и данных

(модель 2).

Приведите пример. ............................................................................................38

34.Комбинаторная модель для оценки необходимого размера памяти КС (модель 4).

Приведите пример. ......................................................................................................................38

Комбинаторная модель, позволяющая произвести расчет оценки сверху необходимого

размера оперативной памяти КС. ..............................................................................................39

Совместное исследование параллельных КС и алгоритмов. ..................................................39

39.Классы характеристик КС. ....................................................................................................40

Абсолютно однородная сеть (определение, примеры). ...........................................................40

Проблемы адаптации структуры КС к алгоритмам решаемых задач в терминах теории

графов. ..........................................................................................................................................41

Определите d в узле КС и в КС (структура КС условно изображена на рис). .....................41

Понятие о сложности сети КС. (?) .............................................................................................41

40.Проблемы адаптации структуры КС к алгоритмам решаемых задач в терминах теории

графов. (Адаптация КС к алгоритму ← так в лекциях называется). ......................................42

51. Построить коммутатор по схеме сети косвенного двоичного n-куба (сеть Клоса). ......43

Построить двухкаскадный коммутатор компьютерной сети. .................................................43

49. Приведите общее выражение для переключающей матрицы. ..........................................44

Надежность кольцевой структуры КС (для сети [n,2]). ...........................................................45

42.Отказоустойчивость (живучесть) топологической структуры КС. ...................................45

Связь стоимостных характеристик и топологии КС. ...............................................................46

1.Классификация параллельных КС по структурнофункциональным признакам.

По-видимому, самой ранней и наиболее известной является классификация

архитектур вычислительных систем, предложенная в 1966 году М.Флинном.

Классификация базируется на понятии потока.

Классификация по Флинну:

Вычислительная система с одним потоком команд и данных (однопроцессорная

ЭВМ — SISD, Single Instruction stream over a Single Data stream).

Вычислительная система с общим потоком команд (SIMD, Single Instruction,

Multiple Data — одиночный поток команд и множественный поток данных).

Вычислительная система со множественным потоком команд и одиночным

потоком данных (MISD, Multiple Instruction Single Data — конвейерная ЭВМ).

Вычислительная система со множественным потоком команд и данных (MIMD,

Multiple Instruction Multiple Data)

К минусам можно отнести, что слишком много ВС попадает в класс MIMD.

Пытаясь систематизировать машины внутри класса MIMD Р. Хокли получил

иерархическую структуру.

Основная идея: Множественный поток команд может быть обработан 2 способами:

1. Одним конвейерным устройством, работающем в режиме разделения времени.

2. Каждый поток обрабатывается собственным устройством.

Классификация по Р. Хокли:

1. MIMD

2. Конвейерные устройства

3. С собственным устройством для каждого

потока

4. MIMD компьютеры в которых в которых

возможна связь каждого вычислителя с

каждым (с переключателями)

5. MIMD компьютеры у которых возможна

связь только с ближайшими.

6. С общей памятью

7. с распределенной памятью

8. регулярные решетки

9. гиперкубы

10. иерархические структуры

11. изменяющиеся конфигурации

Среди MIMD-компьютеров с переключателями выделяются те, в которых вся память

распределена между процессорами.

Если память – разделяемый ресурс, доступный для всех процессоров через

переключатели, то MIMD-машина является системой с общей памятью. В соответствии с

конфигурацией переключателя различают:

простой переключатель

многокаскадный переключатель

общая шина

Многие современные компьютерные системы имеют как общую разделяемую

память, так и распределенную, такие системы Хокли рассматривал как гибридные MIMDсистемы с переключателями.

Если рассматривать MIMD-системы с сетевой структурой (8, 9, 10, 11), то все они

имеют распределенную память, а дальнейшая классификация может проводиться в

соответствии с топологией сети.

Классификация Шнайдера

В 1988 году Л.Шнайдер (L.Snyder) предложил новый подход к описанию архитектур

параллельных вычислительных систем, попадающих в класс SIMD систематики Флинна.

Основная идея заключается в выделении этапов выборки и непосредственно исполнения в

потоках команд и данных. Именно разделение потоков на адреса и их содержимое

позволяет описать такие ранее "неудобные" для классификации архитектуры, как

компьютеры с длинным командным словом, систолические массивы и целый ряд других.

Классификация Скилликорна

Классификация Скилликорна (1989) была очередным расширением классификации

Флинна. Архитектура любого компьютера в классификации Скилликорна

рассматривается в виде комбинации четырёх абстрактных компонентов:

процессоров команд (Instruction Processor — интерпретатор команд, может

отсутствовать в системе),

процессоров данных (Data Processor — преобразователь данных),

иерархии памяти (Instruction Memory, Data Memory — память программ и данных),

переключателей (связывающих процессоры и память).

Переключатели бывают четырёх типов — «1-1» (связывают пару устройств), «n-n»

(связывает каждое устройство из одного множества устройств с соответствующим ему

устройством из другого множества, то есть фиксирует попарную связь), «n x n» (связь

любого устройства одного множества с любым устройством другого множества).

Классификация Скилликорна основывается на следующих восьми характеристиках:

Количество процессоров команд IP

Число ЗУ команд IM

Тип переключателя между IP и IM

Количество процессоров данных DP

Число ЗУ данных DM

Тип переключателя между DP и DM

Тип переключателя между IP и DP

Тип переключателя между DP и DP

Классификация Фенга

В 1972 году Фенг предложил классифицировать вычислительные систем на основе

двух простых характеристик. Первая — число n бит в машинном слове, обрабатываемых

параллельно при выполнении машинных инструкций. Практически во всех современных

компьютерах это число совпадает с длиной машинного слова. Вторая характеристика

равна числу слов m, обрабатываемых одновременно данной ВС. Немного изменив

терминологию, функционирование ВС можно представить как параллельную обработку m

битовых слоёв, на каждом из которых независимо преобразуются n бит. Каждую

вычислительную систему можно описать парой чисел (n, m). Произведение P = n x m

определяет интегральную характеристику потенциала параллельности архитектуры,

которую Фенг назвал максимальной степенью параллелизма ВС.

Таким образом все КС MIMD можно разделить на 4 класса:

Разрядно-последовательные, пословно-последовательные n=m=1, т.е. в каждый

момент времени такая система обрабатывает только 1 двоичный разряд.

Разрядно-параллельные последовательно-последовательные n>1, m=1.

Разрядно-последовательные, пословно-параллельные n=1, m>1 (обычно КС этого

класса состоят из большого числа одноразрядных процессоров, причем каждый

процессор может независимо от остальных обрабатывать свои данные).

Разрядно-параллельные, пословно параллельные n>1, m>1.

Плюс: введен единый числовой метрик для различных типов КС, с помощью

которого можно сравнивать разные КС.

Минус: опираясь на данную классификацию сложно представить себе специфику той

или иной КС (Не учитываются конструкторские особенности)

Классификация Хендлера

В основу классификации В.Хендлер закладывает явное описание возможностей

параллельной и конвейерной обработки информации вычислительной системой. При этом

он намеренно не рассматривает различные способы связи между процессорами и блоками

памяти и считает, что коммуникационная сеть может быть нужным образом

сконфигурирована и будет способна выдержать предполагаемую нагрузку.

Предложенная классификация базируется на различии между тремя уровнями

обработки данных в процессе выполнения программ:

уровень выполнения программы - опираясь на счетчик команд и некоторые другие

регистры, устройство управления (УУ) производит выборку и дешифрацию команд

программы;

уровень выполнения команд - арифметико-логическое устройство компьютера

(АЛУ) исполняет команду, выданную ему устройством управления;

уровень битовой обработки - все элементарные логические схемы процессора

(ЭЛС) разбиваются на группы, необходимые для выполнения операций над одним

двоичным разрядом.

Таким образом, подобная схема выделения уровней предполагает, что

вычислительная система включает какое-то число процессоров каждый со своим

устройством управления. Каждое устройство управления связано с несколькими

арифметико-логическими устройствами, исполняющими одну и ту же операцию в каждый

конкретный момент времени. Наконец, каждое АЛУ объединяет несколько элементарных

логических схем, ассоциированных с обработкой одного двоичного разряда (число ЭЛС

есть ничто иное, как длина машинного слова).

Если на какое-то время не рассматривать возможность конвейеризации, то число

устройств управления k , число арифметико-логических устройств d в каждом устройстве

управления и число элементарных логических схем w в каждом АЛУ составят тройку для

описания данной вычислительной системы C: t(C)= (k, d, w)

2.Классификация параллельных КС по функциональным

возможностям КС с точки зрения пользователя.

Здесь про мультикомпьютеры и прочую Лабуду (см ниже)

3.Проведите сравнительный анализ классификаций

компьютерных систем.

Имеется множество различных классификаций параллельных КС.

В качестве основных признаков классификаций, характеризующих структуру и

функционирование ВС с точки зрения параллельности работы системы, чаще всего

используют следующие характеристики:

тип потока команд

тип потока данных

способ обработки данных

тип коммуникационной среды

степень однородности компонент системы

степень согласованности режима работы устройств

По способу обработки данных ВС делятся на системы с пословной и поразрядной

обработкой.

В системах с пословной обработкой все разряды каждого слова

обрабатываются процессором последовательно (слово за словом). В системах с

поразрядной обработкой одноименные разряды большого числа слов обрабатываются

одним процессором, но параллельно (Ассоциативные системы).

Примерами возможных классификаций являются классификации по Флину, Хокли,

Шнайдеру, Скилликорну, Фенгу, Хендлеру и множество других. Нельзя выделить какуюто одну систему классификаций потому, что они подразделяют ВС, основываясь на

разных принципах.

4.Мультикомпьютеры, кластеры и симметричные

мультипроцессоры общая характеристика, схемы построения,

особенности каждой из систем, области применения.

Мультикомпьютеры.

Мультикомпьютеры

–

совокупность

объединенных

сетью

отдельных

вычислительных модулей, каждый из которых управляется своей ОС (например, серии

SP1I6M). Узлы мультикомпьютеров обычно не имеют общих структур и связаны лишь

сетью. Узлы обладают высокой степенью автономности и могут состоять из отдельных

компонентов, в том числе и кластеров, SMP-, SPM-, DSM-, MPP–систем.

Для распределенной ОС мультикомпьютер выглядит как виртуальный

однопроцессорный ресурс. Взаимодействие процессоров реализуется с помощью явно

заданных операций связи между вычислителями. Обычно в мультикомпьютере

реализуется согласованный сетевой протокол, и не существует единой очереди

выполняющихся процессов, хотя известны и другие примеры.

Кластеры.

Кластер – набор компонентов, рассматриваемый операционной системой, системным

ПО, приложениями и пользователями как единая система.

Кластеры получили широкое распространение из-за высокого уровня

производительности при относительно низких затратах. Высокая производительность

объясняется отсутствием совместно используемой оперативной памяти и наличием в

каждом узле копии общей ОС или собственной ОС для неоднородных кластеров.

Специализированное ПО производит контроль правильности работы узлов кластера. При

отказе узла кластера его ресурсы (дисковое пространство, задание и т.д.) переназначаются

другим узлам.

По сути, кластер образуется из отдельных полноценных узлов, включающих

процессоры, память, подсистему ввода-вывода, ОС и т.д. При объединении компьютеров в

кластер чаще всего поддерживается прямая связь между узлами посредством

коммуникационной сети. Технология такой сети может варьироваться от простейшей

(Ethernet) до сложных специализированных вариантов, обеспечивающих высокую

скорость обмена. Возможно параллельное использование нескольких независимых сетей в

рамках одного кластера.

На рисунке изображены 2 типичные структуры кластеров: архитектура с

разделяемыми дисками (слева) и архитектура без разделения дисков.

В архитектуре с разделением дисков все узлы кластера имеют доступ ко всем

дискам. В архитектуре без разделения дисков, несмотря на то, что поддерживается

целостный образ ресурса, каждый узел имеет собственную оперативную память и диски; в

таких системах общей является только коммуникационная сеть.

С точки зрения повышения производительности кластер является хорошо

масштабируемой ВС. Однако отсутствие общей разделяемой памяти (а иногда и единого

адресного пространства) обуславливает большие накладные расходы, связанные с

обменом сообщениями между узлами.

Наибольший эффект кластеры дают при вычислениях в рамках хорошо

структурированных научных приложениях. С точки зрения удобства масштабирования

кластерные архитектуры допускают практически неограниченное наращивание числа

узлов. Для управления кластером используются специальные инструменты для

поддержания единого образа ресурса, в частности, система пакетной обработки.

Симметричные мультипроцессоры.

Симметричный мультипроцессор (относится к классу SMP-систем) состоит из

нескольких десятков процессоров, причем все процессоры разделяют общую память и

объединены коммуникационной системой.

Существуют варианты SMP-архитектур с одной или несколькими системными

шинами (например, Cray 6400 имел 4 системные шины). Также существуют SMPархитектуры со специальными коммутаторами для связи процессоров, памяти и

подсистемы ввода-вывода. Пропускная способность коммуникационной системы

достаточна для поддержания быстрого доступа к памяти. У отдельных процессоров

имеются свои уровни кеш-памяти. Достаточный объем кеша и сравнительно небольшое

количество процессоров позволяет удовлетворять обращения к основной памяти. Это

легло в основу названия таких архитектур - UMA-архитектуры.

UMA (Uniform Memory Access, однородный доступ к памяти).

В UMA-архитектурах имеется единственная ОС, а ПО работает с единым адресным

пространством. При этом возникает сложная проблема сохранения когерентности данных

(согласованного извлечения содержимого кешей и основной памяти). Если

модифицируется одна из копий данных, остальные копии должны либо также

модифицироваться, било объявляться недостоверными. Отсюда – 2 альтернативных

подхода к поддержанию когерентности разделяемых данных:

1) запись с обновлением данных

2) запись с аннулированием данных

В SMP-системах обычно реализуется шинный протокол наблюдения. Происходит

прослушивание шины всеми процессорами с целью обнаружения операций записи в те

ячейки памяти, копии содержимого которых содержатся в кеше данного процессора.

Производительность систем с общей памятью, в т.ч. SMP, зависит от принятой модели

согласованности памяти, определяющей, в каком порядке процессоры наблюдают

последовательность операций записи-чтения.

Передача данных между кешами различных процессоров в SMP-системах

выполняется значительно быстрее, чем обмен данными между узлами кластера или

мультикомпьютера. Поэтому SMP-система хорошо масштабируется с ростом

производительности при обработке большого числа коротких транзакций (например,

банковские операции).

Сохранение когерентности требует специальных аппаратных средств быстрой

модификации копий данных. Однако, если следовать строгой модели согласованности,

когда каждая операция записи возвращает последнее записанное значение, то происходит

неизбежное падение производительности. Главная сложность построения SMP-систем сильная связанность процессоров и наличие единой ОС, разделяемой всеми

процессорами.

5.Системы с распределенной и разделяемой памятью, массовопараллельные системы общая характеристика, схема

построения, особенности каждой из систем, области применения.

DSM-системы (Distributed Shared Memory) – системы с распределенной и

разделяемой памятью; память таких узлов разделена физически, но адресуется в рамках

единого адресного пространства. DSM-системы могут быть реализованы различными

способами. Общим для разных реализаций является тот факт, что узел может состоять из

нескольких процессоров и иметь SMP-архитектуру. Также в DSM-системах

поддерживается общее адресное пространство, но при этом память является

распределенной по узлам и время доступа к памяти зависит от месторасположения

данных, поэтому некоторые DSM-системы получили название NUMA.

NUMA – Non-Uniform memory Acess (Architecture) – Неоднородный доступ

(архитектура) к памяти.

Частный случай NUMA–архитектуры - cc-NUMA.

cc-NUMA – Cache Coherent NUMA, архитектура NUMA с кеш-когерентным

доступом.

Архитектура cc-NUMA:

Механизм работы кеша каждого узла увязан с доступом к локальной памяти каждого

удаленного узла.

Существует справочная память, в которой содержится информация о том, в каких

именно кешах находится нужный блок данных; например, узел 1 обращается к ячейке

памяти с адресом А основной памяти, не являющейся локальным адресом узла 1. Тогда

справочник узла 1 анализирует информацию (адрес А) и определяет, что данные по

адресу А находятся в узле N. В этом случае этот справочник отправляет адрес А в

справочник узла N. Узел N выбирает информацию оп адресу А.

В отличие от шинного протокола наблюдения, где при записи нового значения в кеш

сообщение о модификации передается во все узлы, справочник распознает адрес и

обращается только к тому узлу, где содержится данный адрес.

Преимущество архитектуры: простота.

Недостаток архитектуры: объем аппаратной реализации (пропорционален основной

памяти системы).

Иерархичность доступа к памяти в NUMA-архитектурах сдерживает рост количества

процессоров. Как правило, в современных NUMA-системах количество процессорных

узлов не превышает 64, а число процессоров – 128.

Массово-параллельные системы (МПС).

Отличительной особенностью массово-параллельных систем является большое

число процессорных узлов. Узлы обычно состоят из 1 или нескольких процессоров,

локальной памяти и нескольких устройство ввода-вывода.

В массово-параллельных системах реализуется архитектура без разделения ресурсов.

В каждом узле работает своя копия ОС, а узлы объединяются коммуникационной

системой.

Если узел управляется своей собственной ОС и имеет уникальное адресное

пространство памяти, то не потребуется никаких аппаратных средств для обеспечения

когерентности (согласованности).

Когерентность в случае МПС обеспечивается программными средствами на основе

техники обмена сообщениями. Также МПС можно отнести к мультикомпьютерам.

В МПС с разделяемой распределенной памятью возможна как аппаратная, так и

программная поддержка (???). Такую разновидность МПС можно отнести к классу

NUMA.

6. Структура, достоинства и недостатки UMA-, NUMA- и ccNUMAсистем

UMA (заход на UMA через SMP)

Симметричный мультипроцессор (SMP-система) состоит из нескольких десятков

процессоров, причем все процессоры разделяют общую память и объединены

коммуникационной системой.

Существуют варианты SMP-архитектур с одной или несколькими системными

шинами (например, Cray 6400 имел 4 системные шины). Также существуют SMPархитектуры со специальными коммутаторами для связи процессоров, памяти и

подсистемы ввода-вывода. Пропускная способность коммуникационной системы

достаточна для поддержания быстрого доступа к памяти. У отдельных процессоров

имеются свои уровни кеш-памяти. Достаточный объем кеша и сравнительно небольшое

количество процессоров позволяет удовлетворять обращения к основной памяти. Это

легло в основу названия таких архитектура: UMA-архитектуры.

UMA (Uniform Memory Access, однородный доступ к памяти).

В UMA-архитектурах имеется единственная ОС, а ПО работает с единым адресным

пространством. При этом возникает сложная проблема сохранения когерентности данных

(согласованного извлечения содержимого кешей и основной памяти). Если

модифицируется одна из копий данных, остальные копии должны либо также

модифицироваться, било объявляться недостоверными. Отсюда – 2 альтернативных

подхода к поддержанию когерентности разделяемых данных:

1) запись с обновлением данных

2) запись с аннулированием данных

В SMP-системах обычно реализуется шинный протокол наблюдения. Происходит

прослушивание шины всеми процессорами с целью обнаружения операций записи в те

ячейки памяти, копии содержимого которых содержатся в кеше данного процессора.

Производительность систем с общей памятью, в т.ч. SMP, зависит от принятой модели

согласованности памяти, определяющей, в каком порядке процессоры наблюдают

последовательность операций записи-чтения.

Передача данных между кешами различных процессоров в SMP-системах

выполняется значительно быстрее, чем обмен данными между узлами кластера или

мультикомпьютера. Поэтому SMP-система хорошо масштабируется с ростом

производительности при обработке большого числа коротких транзакций (например,

банковские операции).

Сохранение когерентности требует специальных аппаратных средств быстрой

модификации копий данных. Однако, если следовать строгой модели согласованности,

когда каждая операция записи возвращает последнее записанное значение, то происходит

неизбежное падение производительности. Главная сложность построения SMP-систем сильная связанность процессоров и наличие единой ОС, разделяемой всеми

процессорами.

NUMA (заход через DSM-системы)

DSM-системы (Distributed Shared Memory) – системы с распределенной и

разделяемой памятью; память таких узлов разделена физически, но адресуется в рамках

единого адресного пространства. DSM-системы могут быть реализованы различными

способами. Общим для разных реализаций является тот факт, что узел может состоять из

нескольких процессоров и иметь SMP-архитектуру. Также в DSM-системах

поддерживается общее адресное пространство, но при этом память является

распределенной по узлам и время доступа к памяти зависит от месторасположения

данных, поэтому некоторые DSM-системы получили название NUMA.

NUMA – Non-Uniform memory Acess (Architecture) – Неоднородный доступ

(архитектура) к памяти.

cc-NUMA

Частным случаем NUMA–архитектуры является cc-NUMA

cc-NUMA – Cache Coherent NUMA, архитектура NUMA с кеш-когерентным

доступом.

Архитектура cc-NUMA:

Механизм работы кеша каждого узла увязан с доступом к локальной памяти каждого

удаленного узла.

Существует справочная память, в которой содержится информация о том, в каких

именно кешах находится нужный блок данных; например, узел 1 обращается к ячейке

памяти с адресом А основной памяти, не являющейся локальным адресом узла 1. Тогда

справочник узла 1 анализирует информацию (адрес А) и определяет, что данные по

адресу А находятся в узле N. В этом случае этот справочник отправляет адрес А в

справочник узла N. Узел N выбирает информацию оп адресу А.

В отличие от шинного протокола наблюдения, где при записи нового значения в кеш

сообщение о модификации передается во все узлы, справочник распознает адрес и

обращается только к тому узлу, где содержится данный адрес.

Преимущество архитектуры: простота.

Недостаток архитектуры: объем аппаратной реализации (пропорционален основной

памяти системы).

Иерархичность доступа к памяти в NUMA-архитектурах сдерживает рост количества

процессоров. Как правило, в современных NUMA-системах количество процессорных

узлов не превышает 64, а число процессоров – 128.

6.1.Масштабируемая архитектура. Что понимается под словами

«масштабируемость кластера»?

Масштабируемая архитектура вычислительной сети – архитектура, позволяющая

наращивать количество вычислителей без коренной перестройки топологии или замены

имеющегося оборудования. При этом производительность сети должна расти с

увеличением количества вычислителей.

Все существующие многопроцессорные архитектуры являются в некотором смысле

масштабируемыми. При этом чем выше степень связности модулей многопроцессорной

ВС, тем сложнее выполняется масштабирование, но тем быстрее осуществляется обмен

данными между узлами.

Широчайшее распространение кластерных многопроцессорных систем в первую

очередь объясняется слабой связностью его вычислительных узлов и унифицированной

технологией коммутационной сети, эту связь обеспечивающей (Ethernet и т.д.). Кластер

является наиболее масштабируемой многопроцессорной системой на сегодняшний день

(если не считать вычислений, распределенных по территориальной или глобальной сети),

обеспечивая при этом высочайшую производительность для задач, допускающих

крупноблочное распараллеливание (научные вычислительные задачу, задачи трехмерной

визуализации и др.). При этом кластер показывает сравнительно слабую

производительность при мелкоблочном распараллеливании задач.

6.2.Архитектуры S2MP и NUMA-flex как развитие архитектуры

ccNUMA

S2MP - системы.

Дальнейшее развитие архитектуры cc-NUMA, преодолевающее ограничение на

масштабируемость, получило название S2MP.

Одним из узких мест, сдерживающих число процессорных узлов, является

пропускная способность шин оперативной памяти.

В архитектуре S2MP процессорные узлы объединены сетью, образуемой средой

межсоединений и маршрутизаторами.

Для поддержания когерентности кешей в S2MP-архитектуре используется протокол

справочника (как в cc-NUMA).

Использование в этих системах программируемых маршрутизаторов позволяет

реализовывать системы с различной топологией (и, естественно, различным числом

процессорных узлов).

В S2MP Origin 2000, например, топологией является гиперкуб с числом

процессорных элементов, равным 512.

Архитектура NUMA-flex.

Архитектура NUMA-flex во многом является наследницей S2MP.

Более высокая степень готовности обеспечивается технологией так называемого

разделения, которая позаимствована у кластеров.

Каждый узел архитектуры NUMA-flex представляет собой независимый сервер и для

связи с другими узлами использует инфраструктуру архитектуры S2MP.

В каждом узле может работать своя версия ОС (например, в Origin 2000 это Irix).

Специальные аппаратные средства осуществляют контроль и изолирование ошибок,

возникающих в одном из узлов, и не дают ошибке распространиться на другие узлы.

7.Основные понятия теории моделирования параллельных КС.

Методы моделирования параллельных КС.

Моделирование – замена исходного объекта образом или другим объектом (

моделью ) и изучение свойств оригинала путем исследования свойств модели.

Условия для существования пользы от моделирования:

1. Модель обеспечивает оригинальное отображение свойств оригинала,

существенных с точки зрения исследуемых операций.

2. Модель позволяет устранить проблемы присущие проведению испытаний на

реальных объектах

В зависимости от способа модели делятся:

1. Физические – реальное воплощение( макет )

2. Математические – формализованное описание на некотором язык.

8.Задачи моделирования параллельных КС.

1.

2.

3.

4.

5.

6.

7.

Определение цели моделирования.

Разработка концептуальной модели.

Формализация модели.

Программная реализация

Планирование проведения эксперимента

Реализация плана эксперимента

Анализ результатов моделирования

9.Приведите основные принципы моделирования.

Принципы моделирования:

1. Принцип информационной достаточности. ( при полном недостатке информации о

модели ее моделирование не имеет смысла, есть некоторые пороговый уровень

информации, при котором моделирование возможно ).

2. Принцип осуществимости( модель должна обеспечивать адекватные результаты )

3. Принцип множественности модели. ( Создаваемая модель должна отражать те

свойства реальных объектов, которые влияют на выбранный показатель

эффективности, каждая модель отражает лишь некоторые, выбранные стороны

реального объекта, для составления полной картины необходимо использовать

несколько моделей )

4. Принцип агрегирования. ( сложную систему можно представить как совокупность

простых )

5. Принцип параметризации. ( В ряде случаев моделируемая система имеет

подсистемы, характеризуемые определенным параметром )

10.Моделирование параллельных процессов. Применение

аппарата сетей Петри. Подклассы и расширение сетей Петри.

Почти любая КС имеет в своём составе параллельно работающие элементы, такие

элементы могут взаимодействовать, либо работать независимо. Способы взаимодействия

подсистем определяет вид параллельных процессов в системе. Вид процесса влияет на

способ моделирования.

1. Асинхронный процесс – его состояние не зависит от состояния других процессов.

2. Синхронный процесс – его состояние зависит от состояния взаимодействующих

процессов. Один и тот же процесс может быть синхронен к одному процессу и

асинхронен к другому.

3. Подчиненный процесс – создается и управляется другим процессом более

высокого уровня.

4. Независимый процесс – процесс, который не является подчиненным.

Реализация параллельных процессов в КС

1. Процессы могут быть истинно параллельны только в многопроцессорных ВС

2. Многие процессы используют одни и те же ресурсы

3. В КС существует 2 вида процессов – родительский и дочерний.

4. 3 подхода:

На основе взаимного исключения (монопольный захват ресурса одним

процессом )

На основе синхронизации по сигналам (обмен сигналами между процессами

обозначающими события )

На основе синхронизации по сообщениям (обмен информацией между

процессами )

Средство моделирования изначально ориетировано на параллельную работу

процессов.

Сети Петри – инструмент исследования систем, теория сетей Петри делает

возможным моделирование системы – представление её виде сетей Петри. Применяемость

сетей Петри исключительно для моделирования.

Модель представляется в математических терминах того, что считают корректным

описанием системы. Как правило модель имеет математическую основу. Возможно

несколько путей практического применения сетей Петри при проектировании и анализе. В

одном из подходов сети Петри – вспомогательный инструмент для анализа. В результате

анализа модели проявляются изъяны и ошибки. Можно предложить более радикальный

подход, в котором весь процесс проектирования и определения характеристик проводится

с помощью сетей Петри.

Подклассы сетей Петри:

Простой сетью Петри называется набор

1.

2.

3.

, где

- множество мест;

- множество переходов таких, что

.

- отношение инцидентности такое, что:

a.

b.

Регулярные сети (вводится алгебра регулярных сетей, строятся операции над

сетями и классы элементарных сетей).

Чистые сети (переход не может иметь позицию Pi в качестве входной и

выходной).

Сети свободного выбора (этот подкласс допускает и конфликты автоматных сетей

Петри, и параллельность маркированных графов, но в более ограниченном виде,

чем в обычных сетях Петри. Сеть Петри со свободным выбором есть сеть Петри С

= (Р, Т, I, О) — такая, что для всех

t j T , pi I (t j ), либо.I (t j ) { pi }, либо.O( pi ) {t j } Важность этого определения

заключается в том способе, которым оно допускает управляемые конфликты.

Конфликт появляется только тогда, когда одна позиция является входом

нескольких переходов. По определению сетей Петри со свободным выбором, если

позиция является входом для нескольких переходов (потенциальный конфликт), то

она является единственным входом всех этих переходов. Следовательно, либо все

эти конфликтующие переходы одновременно являются разрешенными, либо ни

один из них. Это позволяет свободно осуществлять выбор (разрешение конфликта)

запускаемого перехода, присутствие фишек в других позициях не влияет на выбор

запускаемого перехода.

Сети, свободные от конфликтов, если Pi принадлежит I( tj), то Pi принадлежит О(

tj), иначе Pi должна иметь <= 1 выходной переход.

Устойчивые сети ( для такой сети маркировка принадлежит множеству

допустимых маркировок, если 2 любых перехода оказываются в возбужденном

состоянии, то срабатывает один из них не исключая возможности срабатывания

другого )

Автоматные графы ( каждый переход может иметь точно один выход и один вход)

Маркированный граф – сеть Петри

C ( P, T , I , O) : pi P " выполняется "

I ( pi ) {t j | pi O(t j ) 1

&&

O( pi ) {t j | pi I (t j ) 1

Расширение сетей Петри.

Е-сети

Сети Мерлина

Временные сети

Раскрашенные сети

Приоритеные сети

Сети с проверкой на ноль

Обобщенные сети.

?11.Применение сетей Петри для синтеза дискретных

управляющих устройств.

Простое представление системы сетью Петри основано на двух основополагающих

понятиях: событиях и условиях. События - это действия, имеющие место в системе.

Возникновением событий управляет состояние системы Состояние системы может быть

описано множеством условий Условие — есть предикат или логическое описание

состояния системы. Условие может принимать либо значение «истина», либо значение

«ложь». Так как события являются действиями, то они могут происходить. Для того чтобы

событие произошло, необходимо выполнение соответствующих условий. Эти условия

называются предусловиями события. Возникновение события может вызвать нарушение

предусловий и может привести к выполнению других условий, постусловий.

В качестве примера рассмотрим задачу моделирования простого автомата-продавца.

Автомат-продавец находится в состоянии ожидания до тех пор, пока не появится заказ,

который он выполняет и посылает на доставку. Условиями для такой системы являются:

а) автомат-продавец ждет;

б) заказ прибыл и ждет;

в) автомат-продавец выполняет заказ;

г) заказ выполнен.

Событиями будут:

1. Заказ поступил.

2. Автомат-продавец начинает выполнение заказа.

3. Автомат-продавец заканчивает выполнение заказа.

4. Заказ посылается на доставку.

Предусловия события 2 (автомат-продавец начинает выполнение заказа) очевидны:

(а) автомат-продавец ждет; (б) заказ прибыл и ждет.

Постусловие для события 2:

(в) автомат-продавец выполняет заказ.

Аналогично мы можем определить предусловия и постусловия для других событий и

составить следующую таблицу событий и их пред- и постусловий:

Событие

1

2

3

4

Предусловие

нет

а,б

в

г

Постусловие

б

в

г,а

нет

Такое представление системы легко моделировать сетью Петри.

В сети Петри условия моделируются позициями, события - переходами. При этом

входы перехода являются предусловиями соответствующего события; выходы постусловиями. Возникновение события равносильно запуску соответствующего

перехода. Выполнение условия представляется фишкой в позиции, соответствующей

этому условию. Запуск перехода удаляет разрешающие фишки, представляющие

выполнение предусловий и образует новые фишки, которые представляют выполнение

постусловий. Сеть Петри на рис. 3.1 иллюстрирует модель приведенного выше автоматапродавца. Мы указали каждому переходу и позиции соответствующие событие и условие.

Можно моделировать и более сложную систему. Система автомат-продавец состоит

из трех различных автоматов M1 , М2 и М3 и двух операторов Fx и F2. Оператор F1

воздействует на автоматы М1 и М2, а оператор F2 — на М1 и М3. Заказы требуют двух

стадий обработки. Сначала они должны быть обработаны автоматом М1 затем либо

автоматом М2 либо М3. Эта более сложная система будет иметь следующие условия:

а) заказ прибыл и ждет обработки автоматом М1

б) заказ обработан автоматом М1 и ждет обработки либо автоматом М2, либо М3;

в) заказ выполнен;

г) автомат M1 незанят;

д) автомат М2 незанят;

е) автомат М3 незанят;

ж) оператор F1незанят;

з) оператор F2 незанят;

и) автомат М{ находится под воздействием оператора F1

к) автомат М1{ находится под воздействием оператора F2,

л) автомат М2 находится под воздействием оператора F1,

м) автомат М3 находится под воздействием оператора F2.

При этом могут происходить следующие события:

1. Поступление заказа.

2. Оператор F1 начинает выполнение заказа на автомате M1

3. Оператор F1 закончил выполнение заказа на автомате М1.

4. Оператор F2 начинает выполнение заказа на автомате М1.

5. Оператор F2 закончил выполнение заказа на автомате М1.

6. Оператор F1 начинает выполнение заказа на М2.

7. Оператор F1 закончил выполнение заказа на М2.

8. Оператор F2 начинает выполнение заказа на М3.

9. Оператор F2 закончил выполнение заказа на М3.

10. Заказ посылается на доставку.

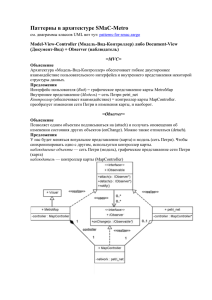

12.Оценочные или Е-сети как расширение сетей Петри

Е-сети ( CE ( P, Pp , PR , T , M 0 )

P – множество позиций,

Pp множество периеритных позиций

PR множество решающих позиций

T – множество переходов причем ti = ( ρS, t(ti) )

S – тип перехода ( 1- 5 ), t(ti) время перехода, ρ(ti) – функция перехода, функция

преобразования атрибута меток.

В Е-сетях метки интерпретируются, как транзакты, распространяющиеся по сети, а

вершины и переходы трактуются как устройства обработки транзактов. Требование – ни

одна вершина не может иметь более 1 метки (т.е. сеть изначально безопасна).

Типы переходов:

1. простой переход, срабатывает при наличии фишки в P1 и отсутсвии в P2,

моделирование некоторого устройства обработки инф.

Te

P1

P2

2. разветвление потока транзактов в ВС.

Fe

P1

P2

P3

3. объединение наличие фишек P2, P3 и отстутсвие в P1

je

P1

P2

P3

4. управляющие разветвление изменяет направление потока транзактов.

Xe

P1

P1

5. приоритетность одних потоков к другим

P2

P3

Xe

P1

P2

P3

P1

12.1.Моделирование конвейерной обработки информации

На протяжении последних лет было предпринято множество шагов направленных на

увеличение производительности ВС. Результатом одного из таких шагов было появление

ВС с конвейерной обработкой информации. Конвейер состоит из набора операций

которые могут выполняться параллельно. Когда операция k завершена, она передает свой

результат (k+1)-й операции и ждет данных от (k-1)-й.

В качестве примера рассмотрим сложение 2 чисел с плавающей точкой. Основные

шаги этой операции предполагают:

1. Выделить экспоненты этих 2 чисел

2. Сравнить эти экспоненты, и если необходимо изменить их должным образом

3. Сдвинуть точку в числе с меньшей экспонентой для их уравнения

4. Сложить дроби

5. Нормализовать результат

6. Проверить экспоненту на переполнение и сформировать экспоненту и дробь

результата

Конвейеры (по способу управления) можно разделить на 2 группы: синхронные и

асинхронные. Синхронные конвейеры каждый такт передают данные на следующий шаг

обработки. Но это не эффективно, т.к. действие, выполняемое на данном шаге, может

занимать времени больше/меньше чем 1 такт. Рассмотрим k-й блок конвейера. Для

управления им нужно знать когда выполняются следующие условия:

Входной регистр

заполнен

Входной регистр пуст

Выходной регистр

заполнен

Выходной регистр

пуст

Блок занят

Блок свободен

Пересылка

осуществлена

13.Свойства-Задачи сохранения и активности сети Петри

Сохранение

Сети Петри можно использовать для моделировании систем распределения ресурсов.

Например, сеть Петри может моделировать запросы, распределения и освобождения

устройств ввода-вывода в вычислительной системе. В этих системах некоторые фишки

могут представлять ресурсы. Группа из трех построчно печатающих устройств

представляется позицией, имеющей в начальной маркировке три фишки. Запрос

построчно-печатающего устройства – это переход, для которого данная позиция является

входной; затем устройство освобождается переходом, для которого позиция построчно

печатающих устройств является выходной.

Для сетей Петри такого типа помимо прочих важным свойством является

сохранение. Нам бы хотелось показать, что фишки, представляющие ресурсы, никогда не

создаются и не уничтожаются. Простейший способ это сделать – это потребовать, чтобы

общее число фишек в сети оставалось постоянным.

Def. Сеть Петри C=(P,T,I,O) с начальной маркировкой называется строго

сохраняющей, если для всех ' R(C , ) имеет место '( pi ) ( pi ) .

pi P

pi P

Строгое сохранение – это очень сильное ограничение. Например, из него немедленно

следует, что число входов в каждый переход должно равняться числу выходов

I (t j ) O (t j ) . Если бы это было не так, запуск перехода изменил бы число фишек в сети.

Фишка определяется ее позицией в сети, все фишки в позиции неразличимы. Фишка

может представлять разное количество ресурсов. В общем случае необходимо определить

веса фишек. Т.к. фишки в позиции не различимы, веса связываются с каждой позицией

сети. Вектор взвешивания (1 , 2 ,..., n ) определяет вес i для каждой позиции

pi P .

Def. Сеть Петри C=(P,T,I,O) с начальной маркировкой называется сохраняющей

по отношению к вектору взвешивания (1 , 2 ,..., n ) , n P , i 0 если для всех

' R(C , ) имеет место

* '( p ) * ( p )

i

i

i

i

Строго сохраняющая сеть Петри является сохраняющей по отношению в вектору

взвешивания (1, 1, … ,1).

Все сети Петри являются сохраняющими по отношения к вектору взвешивания

(0,0,…, 0). Поэтому сеть Петри называют сохраняющей, если она сохраняющая по

отношению к каком-нибудь положительному не нулевому вектору .

Активность

Причиной рассмотрения сохранения в сети Петри было распределение ресурсов в

операционной системе ЭВМ. Другая задача. Которая может возникнуть при

распределении ресурсов вычислительной системы – тупики.

Рассмотрим простой пример.

Система включает 2 различных ресурса q и r и два процесса a и b. Если оба процесса

нуждаются в обоих ресурсах, им необходимо будет совместно использовать ресурсы. Для

выполнения этого потребуем чтобы каждый процесс запрашивал ресурс, а затем

освобождал его. Теперь предположим, что процесс a сначала запрашивает ресурс q, а

затем ресурс r и наконец освобождает и q и r. Процесс b работает аналогично, но сначала

запрашивает ресурс r, а потом q.

Начальная маркировка помечает ресурсы q( p4 ) и r ( p5 ) доступными и указывает на

готовность процессов a и b. Одним выполнением этой сети является t1t2t3t4t5t6 ; другим t4t5t6t1t2t3 . Ни одно из этих выполнений не приводит к тупику. Однако рассмотрим

последовательность, которая начинается переходами t1 , t4 : процесс a обладает ресурсом q

и хочет получить ресурс r, а процесс b обладает ресурсом r и хочет получить ресурс q.

Система заблокирована; никакой процесс продолжаться не может.

Тупик в сети Петри – переход (или множество переходов), которые не могут быть

запущены. В сети Петри на рисунке 4,6 тупик возникает если нельзя запустить переходы

t 2 и t5 . Переход называется активным, если он не заблокирован (нетупиковый).

Переход t j в сети Петри С называется потенциально запустимым в маркировке ,

если существует маркировка ' R(C , ) , в которой t j разрешен. Переход активен в

маркировке , если потенциально запустим во всякой маркировке из R (C , ) .

Следовательно, если переход активен, то всегда возможно перевести сеть Петри из ее

текущей маркировки, в маркировку в которой запуск перехода станет разрешенным.

Другие понятия, связанные с изучением тупиков, можно разбить на категории по

уровню активности и определить для сетей Петри С с маркировкой следующим

образом:

Уровень 0: Переход t j обладает активностью уровня 0, если он никогда не

может быть запущен.

Уровень 1: Переход t j обладает активностью уровня 1, если он потенциально

запустим, т.е. если существует такая ' R(C , ) , что t j разрешен в ' .

Уровень 2: Переход t j обладает активностью уровня 2, если для всякого целого

n существует последовательность запусков, в которой t j присутствует неограниченно

часто.

Уровень 3: Переход t j обладает активностью уровня 3, если существует

бесконечная последовательность запусков, в которой t j присутствует неограниченное

число раз.

Уровень 4: Переход t j обладает активностью уровня 4, если для всякой

' R(C , ) существует такая последовательность запусков , что t j разрешены в

( ', )

Переход, обладающий уровнем активности 0, называется пассивным; активностью 4,

называется активным. Сеть Петри обладает активностью уровня i, если каждый ее переход

обладает активностью уровня i.

Переход t 0 не может быть запущен никогда, он пассивен. Переход t1 может быть

запущен ровно 1 раз, он обладает активностью уровня 1. Переход t 2 может быть запущен

произвольное число раз, но это число зависит от числа запусков перехода t3 . Если мы

хоти запустить t 2 5 раз, то мы запускаем 5 раз t3 , затем t1 и после этого 5 раз t 2 . Однако,

как только запустится t1 число запусков t 2 станет фиксированным. Следовательно t 2

обладает активностью уровня 2. Переход t3 может быть запущен неограниченное число

раз, и поэтому обладает активностью уровня 3, но не уровня 4, поскольку, как только

запустится t1 , t3 больше запустить будет нельзя.

13.1.Моделирование сетями Петри вычислительных процессов в

КС, использующих кратные функциональные блоки.

Наряду с конвейерной структурой управления, которая предполагает разбиение

операции на микрооперации и параллельное их выполнение, широкое распространение

получил подход, использующий кратные функциональные блоки. В общем случае

структура

определяется

мультимножеством

функциональных

блоков

(ФБ)

U {mi ui }, i 1...n

X {xi }, i 1...m .

и

множеством

буферных

регистров

Функциональные блоки объединены в мультимножество, так как зачастую ФБ

дублируются, т.е. имеют кратность больше 1. Регистры используются для хранения

входных и выходных данных значений функциональных блоков. При отсутствии

противоположного любой ФБ может брать данные и записывать результат в любой

регистр.

Пример:

2 блока умножения 2 u1 , блок сложения u 2 и блок деления u3 .

Регистры с x 0 по x 6 .

Проследим выполнение на такой системе следующих операций:

1. умножить x1 на x1 , результат поместить в x 0 .

2. умножить x1 на x3 , результат поместить в x3 .

3. сложить x 2 с x 4 , результат поместить в x 4 .

4. сложить x 0 с x3 , результат поместить в x3 .

5. разделить x 0 на x 4 , результат поместить в x 6 .

В начальный момент времени из регистра x1 данные посылаются в первый

функциональный блок умножения u1 . По окончании операции результат записывается в

x 0 . Так как система содержит второй блок умножения, который в данный момент

свободен, то вторую операцию (умножение x1 на x3 ) выполним на нем. Результат будет

записан в x3 .

Операция сложения x 2 с x 4 требует свободный блок сложения, исходные данные из

регистров x 2 и x 4 . Все необходимые ресурсы имеются в наличии, поэтому операция

может быть выполнена и результат помещен в регистр x 4 .

Вторая операция сложения требует наличия свободного блока сложения, исходных

данных из x 0 и x3 . Ни один из ресурсов не получен, поэтому необходимо ожидать

выполнения операции 3 для освобождения блока сложения, операции 2 для получения

корректных данных из x3 и операции 1 для получения корректных данных из x 0 .

Последняя операция (деление) может быть выполнена только при свободном блоке

деления (выполнено), корректных данных в x 0 (необходимо ждать выполнения операции

1), корректных данных в x 4 (необходимо ждать выполнения операции 3) и свободного

регистра x 6 (выполнено).

На этом примере видно, что для распараллеливания операций на системе,

построенной на базе кратных функциональных блоков, необходимо наличие свободных

ресурсов (использующиеся функциональные блоки и регистры для вывода результата) и

отсутствие зависимости по данным между операциями.

Система, которая реализует параллелизм последовательной программы таким

образом

для

получения

правильных

результатов

обладает

свойством

детерминированности. Условие поддержания детерминированности: для двух операций

a и b ( a предшествует b на линейном участке программы) b может начать выполняться

прежде чем a тогда и только тогда, когда входные данные b не требуют результата a и

результат b не изменит ни входных данных, ни результата a .

Один из методов, реализующий описанные ограничения и обладающий свойством

детерминированности, основан на таблицах резервирования. В этой таблице хранятся

текущие состояния всех узлов вычислительной системы (свободен или зарезервирован).

При поступлении новой инструкции в таблице просматриваются соответствующие

элементы. Если ни один из узлов не зарезервирован, то инструкция передается на

выполнение и все использующиеся узлы помечаются как зарезервированные. Если же

хотя бы один из регистров или функциональный блок заняты, то выполнение

приостанавливается до освобождения всех ресурсов.

Проведем моделирование работы части системы с помощью сети Петри. Пусть дан

функциональный блок u и регистры i, j , k . Поставим функциональному блоку и каждому

из регистров позицию, указывающую на занятость ресурса (данные позиции дублируют

элементы таблицы резервирования). Если в позиции есть фишка, то ресурс свободен,

иначе – занят. Для обеспечения связи с внешними воздействиями (декодирована очередная

инструкция, которая будет выполнена на блоке u и использующая регистры i, j , k ;

инструкция поступила на выполнение и необходимо декодировать следующую

инструкцию) введем две дополнительные позиции.

В результате получим следующее множество позиций:

p1 - декодирована инструкция, использующая блок u и регистры i, j , k .

p2 - блок u свободен.

p3 - регистр i свободен.

p4 - регистр j свободен.

p5 - регистр k свободен.

p 6 - инструкция поступила на выполнение, готовность декодировать

следующую инструкцию.

p 7 - инструкция поступила на выполнение, функциональный блок u работает

с регистрами i, j , k .

События:

Выдача очередной инструкции на выполнение. Происходит при выполнении

условий: есть инструкция, использующая i, j , k и u ; блок u свободен;

регистр i свободен; регистр j свободен; регистр k свободен. Результатом

события являются: выборка инструкции и готовность декодирования

следующей; поступление инструкции на выполнение, которое влечет

резервирование i, j , k и u .

Окончание выполнения инструкции. Естественно, для наступления данного

события необходимо поступление инструкции на выполнение в предыдущий

момент времени. Результатом события будет освобождение ранее

зарезервированных ресурсов.

Описанные события соответствуют переходам t1 и t 2 .

Опишем входные и выходные функции:

I (t1 ) { p1 , p2 , p3 , p4 , p5 }

O(t1 ) { p6 , p7 }

I (t 2 ) { p7 }

O(t 2 ) { p2 , p3 , p4 , p5 }

В начальный момент времени все ресурсы свободны, операции для выполнения еще

нет. Поэтому начальная маркировка будет следующая: 0 {0,1,1,1,1, 0, 0} . Граф

построенной сети Петри представлен ниже:

Данная схема проста и не учитывает таких факторов как:

Одновременное

использование кратными функциональными блоками

входных регистров. Первая же инструкция забирает маркер. Вторая ожидает

выполнения первой и возвращения маркера. В результате невозможно

параллельное выполнение инструкций.

Выбор ресурсов для выполнения инструкции может зависеть от значений в

других регистрах (например, регистр индексирования при операциях над

матрицами).

Эти проблемы приводят к появлению большого числа дополнительных состояний

(позиций) и событий (переходов). В результате сеть Петри для реального устройства

управления оказывается слишком большой и анализ ее становится затруднительным.

Практическое применение сетей Петри в области кратных функциональных блоков

заключается не только в анализе характеристик самой системы, но и в разработке

компилятора с оптимальной генерацией кода для конкретной вычислительной системы.

14.Задачи достижимости и покрываемости сети Петри.

Задача достижимости. Для заданной сети Петри C с маркировкой и маркировки

определить, верно ли, что R(C , ) .

Задача достижимости является одной из важнейших при анализе сетей Петри.

Многие другие задачи анализа можно сформулировать в ее терминах.

Для сети Петри с рис. 4.6 тупик может возникнуть, если достижимым является

состояние (0, 1, 0, 0, 0, 0, 1, 0).

Задача покрываемости. Для данной сети Петри C с начальной маркировкой и

маркировки определить, существует ли такая достижимая маркировка R(C , ) ,

что .

15.Свойства-Задача безопасности и ограниченности сети Петри.

Одно из важнейших свойств сети Петри, которая должна моделировать реальное

устройство, - безопасность. Позиция сети Петри является безопасной, если число фишек в

ней никогда не превышает 1.

pi P сети Петри C P, T , I , O с начальной

Определение:

Позиция

маркировкой ' pi 1 для любой ' R C, . Сеть Петри безопасна, если безопасна ее

каждая позиция.

Безопасность – очень важное свойство для устройств аппаратного обеспечения.

Если позиция безопасна, то число фишек в ней равно 0 или 1. Следовательно, позицию

можно реализовать одним триггером.

В первоначальном определении сети Петри были безопасны, поскольку переход не

мог быть запущен, если не все из выходных позиций были пусты (а кратные дуги не были

разрешены). Это объяснялось интерпретацией позиции как условия. Условие, будучи

логическим высказыванием либо истинно (представляется фишкой в позиции), либо

ложно (представляется отсутствием фишки); кратные фишки не имеют никакой

интерпретации. Таким образом, если интерпретировать сети как условия и события,

маркировка каждой позиции должна быть безопасной.

Если позиция не является кратной входной или кратной выходной для перехода, ее

можно сделать безопасной. К позиции pi , которую необходимо сделать безопасной,

добавляется новая позиция pi ' . Переходы, в которых pi используется в качестве входной

или выходной, модифицируются следующим образом:

Если pi I t j и pi O t j , тогда добавить pi ' к O t j .

Если pi O t j и pi I t j , тогда добавить pi ' к I t j .

Цель введения этой новой позиции pi ' - представить условие « pi пуста».

Следовательно, pi и pi ' дополнительны; pi имеет фишку, только если pi ' не имеет фишки

и наоборот.

Любой переход, удаляющий фишку из pi , должен помещать фишку в pi ' и наоборот.

Рис.1. Сеть Петри, не являющаяся безопасной

Рис.2. Безопасная сеть Петри, эквивалентная сети

на Рис.1.

Начальная маркировка так же должна быть модифицирована для обеспечения того,

чтобы точно одна фишка была либо в pi , либо в pi ' . (Мы допускаем, что начальная

маркировка безопасна.) Заметим, что такая принудительная безопасность возможна

только для позиций, которые в начальной маркировке являются безопасными и входная и

выходная кратность которых равно 0 или 1 для всех переходов. Позиция, имеющая для

некоторого перехода выходную кратность 2, будет получать при его запуске 2 фишки и,

следовательно, не может быть безопасной.

Безопасность – частный случай ограниченности.

Некоторые соображения относительно реального ограничения на аппаратную

реализацию позиций позволяют прийти к заключению, что безопасность –

необязательное требование. Безопасность позволяет реализовать позицию триггером,

но в более общем случае можно использовать счетчик. Однако любой аппаратнореализованный счетчик ограничен по максимальному числу, которое он может

представить.

Позиция является k-безопасной или k-ограниченной, если количество фишек в ней не

может превышать целое число k.

Определение: Позиция pi P сети Петри C P, T , I , O с начальной маркировкой

является k-ограниченной, если ' pi k для всех ' R C, .

Граница k’ по числу фишек, которые могут находиться в позиции, может быть

функцией от позиции (например, позиция p1 может быть 3-ораниченной, тогда как

позиция p2 - 8-ограниченной). Однако, если позиция p1 k-ограничена, то она так же и k’ограничена для всех k’ >k.

15.1Моделирование сетями Петри задач синхронизации при

взаимодействии процессов в КС

Синхронизация.

Взаимосисключение – это метод создания таких программ, что одновременно не

более чем 1 ресурс имеет доступ к разделяемому объекту.

Для предотвращения проблем такого рода необходимо обеспечить механизм

взаимного исключения. Взаимное исключение это метод создания таких программ, что

одновременно не более чем один процесс имеет доступ к разделяемому объекту данных.

Участок кода, в котором осуществляется доступ к разделяемому объекту и который

требует защиты от вмешательства других процессов, называется критической секцией.

Идея состоит в том, что когда процесс готов выполнить свою критическую секцию, он

сначала ждет, пока другой процесс не выполнит свою собственную критическую секцию.

Затем он «блокирует» доступ к критической секции, не давая возможности никакому

другому процессу войти в свою критическую секцию. Он входит в критическую секцию,

выполняет ее и, выйдя из нее, освобождает ее для доступа со стороны других процессов.

Эта задача может быть решена сетью Петри, как показано на рис. 3.28. Позиция т

представляет собой разрешение для входа в критическую секцию. Для того чтобы какойлибо процесс вошел в критическую секцию, он должен иметь фишку в р1 или в р2

соответственно, свидетельствующую о желании попасть в критическую секцию, а также

должна существовать фишка в m, дающая раз- разрешение на вход. Если оба процесса

пытаются войти в критическую секцию одновременно, то переходы t1 и t2 вступят в

конфликт, и только один из них сможет запуститься. Запуск t1 запретит переход t2,

вынуждая процесс 2 ждать, пока первый процесс выйдет из своей критической секции и

возвратит фишку обратно в позицию m

.

В задаче о производителе/потребителе также присутствует совместно используемый

объект, но в этом случае разделяемый объект точно определен и является буфером.

Процесс-производитель cоздает объекты, которые помещаются в буфер. Потребитель

ждет, пока объект не будет помещен в буфер, удаляет его оттуда и использует. Такая

ситуация может быть промоделирована сетью Петри так, как показано на рис. 3.29.

Позиция В представляет буфер, каждая фишка соответствует элементу данных, который

произведен, но еще не использован. Один из вариантов этой задачи — это задача о

нескольких производителях/нескольких потребителях. В этом случае несколько

производителей порождают элементы данных, помещаемые в общий буфер, для

нескольких потребителей. На рис. 3.30 представлено решение этой задачи в виде сети

Петри. Эта сеть совпадает с сетью на рис. 3.29, Существует несколько вариантов задачи о

чтении/записи, однако основная структура их остается неизменной. Имеются процессы

двух типов: процессы чтения и процессы записи. Все процессы совместно используют

общий файл или переменную или элемент данных. Процессы чтения не изменяют объект

в отличие от процессов записи. Таким образом, процессы записи должны взаимно

исключать все другие процессы чтения и записи, в то время как несколько процессов

чтения могут иметь доступ к разделяемым данным одновременно. Задача состоит в

определении структуры управления, которая не приведет к тупику и не допустит

нарушения критерия взаимного исключения.

На рис. 3.33 иллюстрируется решение задачи в том случае, когда количество

процессов чтения ограничено величиной п. Если в системе количество процессов чтения

не ограничено, то только процессов могут выполняться в одно и то же время. Проблема

возникает в том случае, если количество процессов чтения не ограничено и мы хотим

предоставить возможность ограниченному количеству процессов читать одновременно. В

этом случае можно утверждать, что возникает необходимость хранения количества

читающих процессов. При инициализации каждого процесса чтения в счетчик

добавляется единица, а по окончании процесса единица вычитается. Это легко

моделируется позицией, в которой количество фишек равно количеству процессов чтения.

Однако, для того, чтобы предоставить процессу записи возможность приступить к записи,

необходимо, чтобы счетчик был нулевым, т. е. соответствующая позиция была бы пустой.

В сетях Петри нет механизма, который бы осуществлял проверку на нуль неограниченной

позиции1'. Таким образом, оказывается, что задача о чтении/записи с неограниченным

числом процессов чтения не может быть решена с помощью сетей Петри. Это первый

случай, когда мы столкнулись с тем, что сети Петри не способны моделировать все

системы.

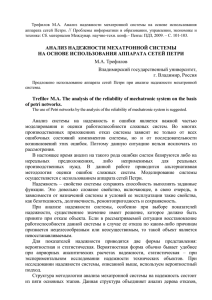

18.Анализ сетей Петри матричным методом

Второй подход к анализу сетей Петри основан на матричном представлении сетей

Петри. Альтернативным по отношению к определению сети Петри в виде (Р, T, I, O)

является определение двух матриц D+ и D-, представляющих входную и выходную

функции. (Они эквивалентны функциям F и В определения Хэка сетей Пет- Петри, см.

разд. 2.6.) Каждая матрица имеет m строк (по одной на переход) и n столбцов (по одному

на позицию). Определим D-[j,i]= D [ j, i] #( pi , I (t j )) , a D [ j, i] #( pi , O(t j )) , Dопределяет входы в переходы, D+ — выходы.

Матричная форма определения сети Петри (Р, T, D- , D+) эквивалентна стандартной

форме, используемой нами, но позволяет дать определения в терминах векторов и матриц.

Пусть e[j] — m-вектор, содержащий нули везде, за исключением j-й компоненты. Переход

tj представляется m-вектором e[j]2). Теперь переход tj в маркировке μ разрешен, если μ >

e[j] • D-, а результат запуска перехода tj в маркировке μ записывается как

( , t j ) e[ j ] D e[ j ] D

e[ j ]( D D ) e[ j ] D

D- составная матрица измененй, тогда для последовательности запусков t j1 t j2 ...t jk

имеем

( , ) ( , t j1 t j2 ...t jk ) e[ j1 ] D e[ j2 ] D ....

e[ jk ] D (e[ j1 ] e[ j2 ] ... e[ jk ]) D f ( ) D

f ( ) (e[ j1 ] e[ j2 ] ... e[ jk ]) называется вектором за- запусков

Вектор

последовательности t j1 t j2 ...t jk i-и элемент вектора f ( ) , f ( )i — это число запусков

перехода ti в последовательности t j1 t j2 ...t jk . Вектор запусков, следовательно, является

вектором с неотрицательными целыми компонентами.

19.Матричный метод анализа сетей Петри достоинства и

недостатки метода

Для того чтобы показать полезность такого матричного подхода к сетям Петри,

рассмотрим, например, задачу сохранения: является ли данная маркированная сеть Петри

сохраняющей? Для того чтобы показать сохранение, необходимо найти (ненулевой)

вектор взвешивания, для которого взвешенная сумма по всем достижимым маркировкам

постоянна. Пусть w n 1 — вектор-столбец. Тогда, если — начальная маркировка, а '

— произвольная достижимая маркировка, необходимо, чтобы w ' w . Теперь,

поскольку ' достижима, существует последовательность запусков переходов а,

которая переводит сеть из в '. Поэтому ' ( , ) f ( ) D Следовательно,

w ' w ( f ( ) D) w w f ( ) D w , поэтому f ( ) D w 0 .

Поскольку это должно быть верно для всех f ( ) , имеем D w 0 . Таким образом,

сеть Петри является сохраняющей тогда и только тогда, когда существует такой

положительный вектор w, что D • w = 0. Это обеспечивает простой алгоритм проверки

сохранения, а также позволяет получать вектор взвешивания w. Развитая матричная

теория сетей Петри является инструментом для решения проблемы достижимости.

Предположим, что маркировка ' достижима из маркировки . Тогда существует

последовательность (возможно, пустая) запусков переходов а, которая приводит из к

'. Это означает, что f ( ) является неотрицательным целым решением следующего

матричного уравнения для х: ' x D . Следовательно, если ' достижима из

тогда уравнение ' x D имеет решение в неотрицательных целых; если уравнение

' x D ) не имеет решения, тогда ' недостижима из .

Границы возможности моделирования с помощью сетей Петри

Дейкстра определил свои Р- и V-операции над семафорами для обеспечения

инхронизации и связи в системах взаимодействующих процессов [78]. Семафор может

рассматриваться как целочисленная переменная, которая принимает только

нтрицательные значения.

V-операция над семафором S увеличивает значение семафора на единицу: S = S + 1.

Р-операция, наоборот, уменьшает S на едиединицу до тех пор, пока результат не

становится равным нулю; при S = 0 процесс, прежде чем продолжать свою работу, должен

ждать

момента, когда S можно будет уменьшить. Связь между семафорами и сетями Петри

была выявлена в разд. 3.4.8.

Поскольку Р- и V-операции были предложены как механизм для решения всех задач

синхронизации программ, то естественно возникает вопрос о полноте, т. е. об их

способности к решению всех задач координации. Патил в 1971 г. [233] предложил

доказательство того, что Р- и V-операции недостаточно мощное средство для решения

всех задач координации. Его подход был весьма прост: он сформулировал задачу

синхронизации, которая не может быть решена с помощью Р- и V-операций, — это задача

о курильщиках сигарет.

Задача о курильщиках сигарет включает (по меньшей мере) четыре процесса,

которые моделируют агента и трех курильщиков. Каждый курильщик непрерывно

изготавливает сигарету и курит ее. Чтобы сделать сигарету, необходимы три составные

части: татабак, бумага и спички. Один из курильщиков всегда имеет бумагу, другой —

табак, а третий — спички. Агент обладает бесконечными запасами всех трех составных

частей. Агент кладет две составные части на стол. Курильщик, имеющий третий

недостающий, может сделать и закурить сигарету, сигнализируя об этом агенту. Тогда

агент помещает другие два из трех инградиентов, и цикл повторяется.

Если семафор поставить в соответствие каждой составной части, задача о

курильщиках формулируется в терминах семафоров. Семафоры первоначально равны

нулю. Агент увеличит два из трех семафоров с помощью V-операций, а затем ждет

семафора «сделано».

Соответствующий процесс курильщика уменьшает два семафора (с помощью Ропераций), а затем, произведя действия «сделать сигарету» и «закурить сигарету»,

увеличивает семафор, указывая «сделано». Задача заключается в том, чтобы разработать

программу процессов курильщиков для того, чтобы определить, какой из трех процессов

должен действовать в очередной момент. Действия агента фиксированны и не могут быть

изменены.

Рис. 7.3 иллюстрирует очевидное «решение». Предположим, агент кладет табак и

бумагу [V(t), V(p)]. Тогда курильщик с бумагой может взять табак [P(t)], а курильщик с

табаком может взять бумагу [Р(р)], что в результате приводит к тупику. Патил доказал,

что никакая последовательность Р- и V-операций не может корректно решить эту задачу.

Это было показано с помощью доказательства того, что все Р- и V-«peшeния» могут быть

промоделированы сетями Петри определенного вида (каждый переход имеет не более

двух входов), но что решением является сеть Петри другого вида, и нет способа

преобразовать сеть одного вида в сеть другого вида, не допуская возможности

возникновения тупика.

Более конкретно ограничение на моделирование с помощью сетей Петри состоит в

неспособности проверить на наличие точно определенной маркировки в некоторой

неограниченной позиции и осуществить действие в зависимости от результатов проверки.

Это ограничение общеизвестно как неспособность к проверке на нулевую маркировку в

некоторой позиции, и поэтому это свойство известно как проверка на нуль [150]. Сети

Петри не могут проверить неограниченную позицию на нуль. [Если позиция ограниченна,

то нуль может быть выявлен. Для ограниченной позиции pi с границей k мы можем

создать дополнительную позицию рi — такую, что сумма ( pi ) ( pi ') является

константой, равной k для всех достижимых маркировок. Это позволяет нам проверить,

равняется ли ( pi ) нулю, проверяя, равно ли ( pi ') k (см. разд. 5.6).]

23.Сети Петри и их особенности

Def.Сеть Петри – четверка С=(P,T,I,O), где P – множество позиций, T –

множество переходов, I – является входной функцией (отображением из переходов в

комплекты позиций), O – выходная функция (отображения из переходов в позиции).

Сети Петри – инструмент исследования систем. Теория сетей Петри делает

возможным моделирование системы математическим представлением ее в виде сети

Петри. Предполагается, что анализ сети Петри поможет получить важную информацию о

структуре и динамическом поведении моделируемой системы.

Возможно несколько подходов к использованию сетей Петри при проектировании и

анализе ВС:

1. Сеть Петри можно рассматривать как вспомогательный инструмент, т.е. для

построения ВС используются общие принципы проектирования, затем построенная

система моделируется сетью Петри и производится анализ полученных

результатов. Любые нестыковки, встречающиеся при анализе сети Петри,

указывают на недоработки при проектировании. Для их исправления необходимо

модифицировать проект.

2. Весь процесс проектирования и определения параметров ВС проводится в

терминах сетей Петри. Задача сводится к представлению сетью Петри реальной

рабочей системы.

Ответы на вопросы №31,32,33 (для всех один и тот же рисунок)

Матрицы, представляющие входную и выходную функцию:

1 1 1 0

1 0 0 0