Пролзователь Каналы Блоки оперативной памяти

advertisement

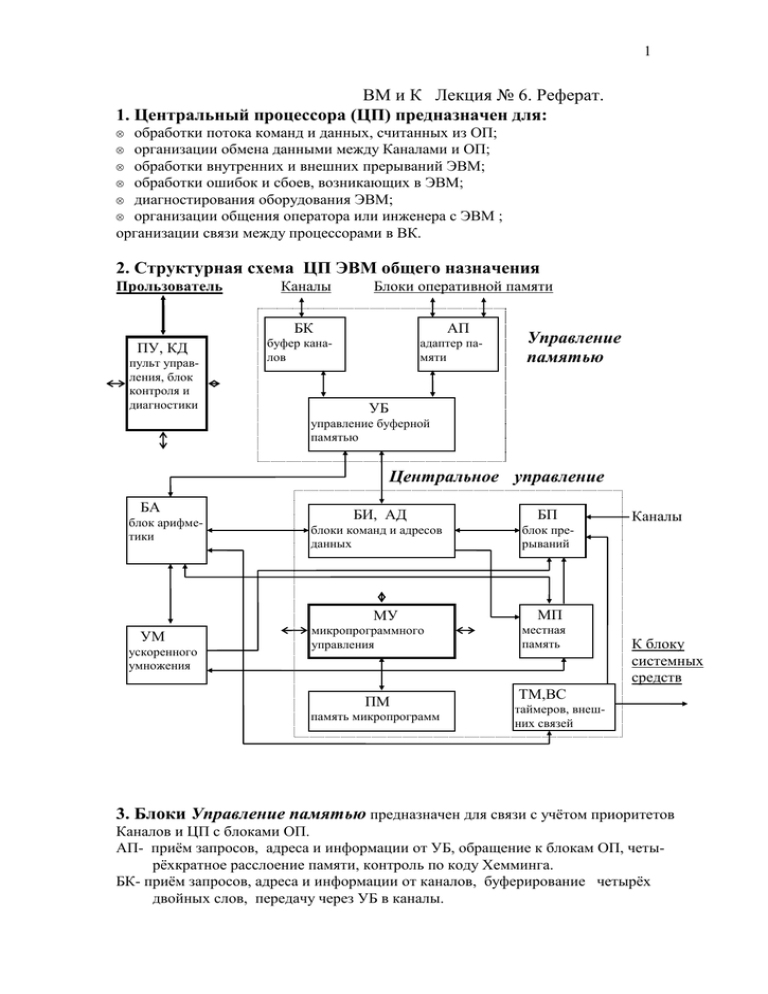

1 ВМ и К Лекция № 6. Реферат. 1. Центральный процессора (ЦП) предназначен для: обработки потока команд и данных, считанных из ОП; организации обмена данными между Каналами и ОП; обработки внутренних и внешних прерываний ЭВМ; обработки ошибок и сбоев, возникающих в ЭВМ; диагностирования оборудования ЭВМ; организации общения оператора или инженера с ЭВМ ; организации связи между процессорами в ВК. 2. Структурная схема ЦП ЭВМ общего назначения Прользователь Каналы Блоки оперативной памяти БК ПУ, КД пульт управления, блок контроля и диагностики АП буфер каналов адаптер памяти Управление памятью УБ управление буферной памятью Центральное управление БА блок арифметики БИ, АД БП блоки команд и адресов данных блок прерываний МУ УМ ускоренного умножения микропрограммного управления ПМ память микропрограмм Каналы МП местная память К блоку системных средств ТМ,ВС таймеров, внешних связей 3. Блоки Управление памятью предназначен для связи с учётом приоритетов Каналов и ЦП с блоками ОП. АП- приём запросов, адреса и информации от УБ, обращение к блокам ОП, четырёхкратное расслоение памяти, контроль по коду Хемминга. БК- приём запросов, адреса и информации от каналов, буферирование четырёх двойных слов, передачу через УБ в каналы. 2 УБ- основной в группе Управление памятью, включает: буферную память 8К байт; матрицу адресов; преобразование логических адресов в физические; память ключей защиты. 4. Группа блоков Центральное управление обрабатывает поток команд, адреса операндов, обращение в основную и местную память, прерываний, формирование сигналов управления, отсчёт реального и относительных интервалов времени, организацию мультипроцессорной системы. БИ,АД- основные, включают: регистр ССП; счётчик команд; буфер команд; регистры прохождения команд по уровням обработки; регистры адресов обращения в память. Этапы: распаковка из буфера; считывание операндов; выполнение и запись. Параллельное формирование адреса следующего участка программы. МП- 16 регистров общего назначения (РОН)и 4 регистра с плавающей запятой (РПЗ). Считывание по адресу из БИ. БП- прерывания внутренние, от Каналов, внешних.. Приоритеты. Формирование адреса записи/ считывания ССП. ПМ- память микропрограмм включает 4096 слов по 144 разряда. МУ- формирует с учётом схемных условий адрес микрокоманд, дешифрирует поля микрокоманд. Микропрограммное управление охватывает все блоки ЦП. ТМ- счётчик времени дня, таймер, интервальный таймер, компаратор. Использует для обновления БА. 5. ПУ,КД- связаны со всеми блоками ЦП. 6. Структурная схема ПЭВМ. 32 Интерфейс магистрали 64- разрядная шина внутреннего обмена 32 ALU ________ Регистры общего назначения Сдвигатель Ин Блок дек сегментации Регистры с дескриптоБа- ров________ за ПЛМ границ и атрибутов 32 Шина Линейного адреса Физический адрес Блок управления страницами __________ TLB 32 Блок обработки данных с плавающей точкой ___________ Регистры FPU Устройство управления ___________ Управление защитой __________ 8 Кбайт матрица памяти 32 Дешифратор команд Декодированная команда 32 Блок кэш-памяти Строка Кода 24 Управление предвыборкой __________ Очередь кодов 32 байта 32 Драйвер шины адреса ______________ Драйвер шины данных ______________ Арбитр запросов______ Управление пакетным обменом__ Управление разрядностью шины данных Управление кэш-памятью Контроль чётности 3 Ниже приводятся рисунок и таблица состава и назначения сигналов интерфейса магистрали (ВМК. Лек. № 6. PS-1999г.) Список выводов i486 по функциональным группам1 Адреса Данные Управление Назначение А2 Q14 D0 P1 А20М # D15 Маска лин. 20.Эмул. Реал. Реж A3 R15 D1 N2 ADS # S17 Подт. код. цикла магистрали А4 S16 D2 N1 AHQLD A17 Запрос захв. шины адр. (Кеш) A5 Q12 D3 Н2 BEO # K15 Адреса байтов А6 S15 04 M3 BE1 # J16 А7 Q13 D5 J2 BE2 # J15 А8 R13 D6 L2 BE3 # F17 А9 Q11 D7 L3 BLAST # R16 Упр. пер. пак. с Кеш. А10 S13 D8 F2 BOFF # D17 Немедленный захват маг. ВУ А11 R12 D9 D1 BRDY # H15 Упр. пер. пак. с КЕШ. А12 S7 D10 E3 BREQ # Q15 Внутр.зап. цик. магистали МП A13 Q10 D11 С1 BS8# 016 Упр. разрядностью ШД. 32 -разряда 1 В. Б. Бородин, И.И. Шагурин Микроцессор i486. Стр. 234 4 A14 A15 А16 A17 A18 A19 A20 A21 A22 A23 A24 A25 A26 А27 А28 А29 А30 А31 S5 R7 Q9 Q3 R5 04 Q8 Q5 Q7 S3 Q6 R2 S2 S1 R1 Р2 РЗ Q1 D12 D13 D14 D15 D16 D17 D18 D19 D20 D21 D22 D23 D24 D25 D26 D27 D28 D29 D30 D31 G3 D2 КЗ F3 J3 D3 С2 B1 А1 В2 А2 А4 А6 В6 С7 С6 С8 А8 С9 В8 BS16 # CLK D/C # DPO DP1 DP2 DP3 EADS # FERR # FLUSH # HLDA HOLD IGNNE # INTR KEN # LOCK # M/IO # NMI PCD PCHK # PWT PLOCK # RDY # RESET C17 СЗ М15 N3 F1 НЗ A5 В17 С14 С15 Р15 Е15 А15 А16 F15 N15 N16 В15 J17 (W L15 Q16 F16 С16 при отсутствии сигн. Синхросигнал Дан./Упр. Чётность по адресу на байты W/R # N17 Запись/чтение Подтвержд. Внешн. адр.Кеш Обработка ошибок ? Упр. внутренней КЕШ Подтв. Захв. Магист., пер. ВУ Зап. Захв. Магист. от ВУ Обработка ошибок ? Прерыван Упр. внутренней Кеш Блокированные цик. Маг. Обращен. пам./вв-выв Прерывания Упр. внутренней Кеш Результат конт. чет. при чен. Упр. внутренней Кеш Чт./зап. Операндов > 32 бит Конец цикла магистрали завершён Прерыван 7. На эффективность ЦП влияют следующие особенности структуры: разрядность трактов передачи и обработки данных; число уровней совмещения обработки команд; структура и алгоритмы работы исполнительных блоков; организация выполнения команд передачи управления; организация внутренней памяти процессора; степень совмещения использования оборудования процессора и каналов. 8. Программно-адресуемые регистры ПЭВМ. Процессор 80486 содержит 34 программно-адресуемых регистра. с точки зрения программиста 24 из них являются 32-разрядными, а 10 регистров 16- разрядные. Регистры принято объединять в семь групп: регистры общего назначения ( или регистры данных ), регистры-указатели, сегментные регистры, управляющие регистры, регистры системных адресов, отладочные регистры и тестовые регистры. Кроме того, в отдельную группу выделяют счётчик команд и регистр флагов. 5 Регистры общего назначения Биты 31 16 15 8 7 EAX AH AL 0 Аккумулятор EBX BH BL Базовый регистр ECX CH CL Счётчик EDX DH DL Регистр данных Регистры-указатели Биты 31 16 15 ESI SI 0 Индекс источника EDI DI Индекс приёмника EBP BP Указатель базы ESP SP Указатель стека Сегментные регистры 15 0 Регистр сегмента команд CS DS Регистр сегмента данных SS Регистр сегмента стека ES Регистр дополнительного сегмента данных FS Регистр дополнительного сегмента данных GS Регистр дополнительного сегмента данных Указатель команд и регистр флагов Биты 31 EIP IP EFLAGS Регистры системных адресов 0 Указатель команд Регистр флагов 6 Биты 15 GDTR 0 Регистр таблицы глобальных дескрипторов IDTR Регистр таблицы дескрипторов прерываний LDTR Регистр таблицы локальных дескрипторов TR Регистр состояния задачи Управляющие регистры Биты 31 CR0 0 Слово состояния CR1 Зарезервирован CR2 Регистр линейного адреса ошибки обращения к странице CR3 Регистр базы каталога страниц Тестовые регистры Биты 31 TR6 0 Регистр упр. тестированием Регистр состояния тестирования TR7 Отладочные регистры Биты 31 DR0 DR1 DR2 DR3 DR4 DR5 DR6 DR7 0 Регистры линейного адреса точки останова Зарезервирован Зарезервирован Регистр сост. точки останова Регистр управления отладкой В группу регистров общего назначения включаются регистры АХ, ВХ СХ и DX. Программист может использовать их по своему усмотрению для временного хранения любых объектов (Данных или адресов) и выполнения над ними требуемых операций При этом регистры допускают независимое обращение к старшим (АН, ВН, СН и DH) и младшим (AL, BL, CL и DL) половинам. Так, командапересылает старший байт регистра АХ в младший байт регистра ВХ, не затрагивая при этом вторых байтов этих регистров 7 Еще раз отметим, что сначала указывается операнд-приемник, а после запятой операнд-источник, т.е. команда выполняется как бы справа налево. Во многих случаях регистры общего назначения вполне эквивалентны, однако предпочтительнее в первую очередь использовать регистр АХ, поскольку многие команды занимают в памяти меньше места и выполняются быстрее, если их операндом является регистр АХ (или его половины AL или АН). Индексные регистры SI и DI так же, как и регистры данных, могут использоваться произвольным образом. Однако их основное назначение - хранить индексы (смещения) относительно некоторой базы (т.е. начала массива) при выборке oперандов из памяти. Адрес базы при этом обычно находится в одном из базовых регистров (ВХ или ВР). В дальнейшем такие примеры будут приведены в изобилии. Регистр ВР служит указателем базы при работе с данными в стековых структурах, о чем будет речь впереди, но может использоваться и произвольным образом в большинстве арифметических и логических операций или просто для временного хранения каких-либо данных. Последний из группы регистров-указателей, указатель стека SP, стоит особняком от других в том отношении, что используется исключительно как указатель вершины стека - специальной структуры, которая будет рассмотрена позже. Регистры SI, DI, ВР и SP, в отличие от регистров данных, не допускают побайтовую адресацию. Четыре сегментных регистра CS, DS, ES и SS хранят начальные адреса сегментов программы и, тем самым, обеспечивают возможность обращаться к этим сегментам. Регистр CS обеспечивает адресацию к сегменту, в котором находятся программные коды, регистры DS и ES - к сегментам с данными (таким образом, в любой момент времени программа может иметь доступ к двум сегментам данных, основному и дополнительному), а регистр SS - к сегменту стека. Сегментные регистры, естественно, не могут выступать в качестве регистров общего назначения. Регистр команд IP следит за ходом выполнения программы, указывая относительный адрес команды, следующей за исполняемой. IP - программно недоступен. Микропроцессор наращивает текущий адрес, учитывая длину текущей команды. Регистр флагов, эквивалентный регистру состояния процессора других вычислительных систем, содержит информацию о текущем состоянии процессора (рис. 3.2). Он включает 6 флагов состояния и 3 бита управления состоянием процессора, которые, впрочем. Тоже обычно называются флагами. Флаг переноса CF (Carry Flag) индицирует перенос или заём при выполнении арифметических операций, а также служит индикатором ошибки при обращении к системным функциям. 8 Флаг паритета PF (Parity Flag) устанавливается в 1, если младшие 8 бит результата операции содержат четное число двоичных единиц. Флаг вспомогательного переноса AF (Auxiliary Flag) используется в операциях над упакованными двоично-десятичными числами. Он индицирует перенос или заем из старшей тетрады (бита 3). Флаг нуля ZF (Zero Flag) устанавливается в 1, если резуьтат операции равен 0. Флаг знака SF (Sign Flag) показывает знак результата операции, устанавливаясь в 1 при отрицательном результате. Флаг переполнения OF (Overflow Flag) фиксирует переполнение, т.е. выход результата операции за пределы допустимого для данного процессора диапазона значений. Флаги состояния автоматически устанавливаются процессором после выполнения каждой команды. Так, если в регистре AX держится число 1, то после выполнения команды декремента (уменьшения содержимого АХ на 1) dec AX содержимое АХ станет равно 0, и процессор сразу отметит этот факт, установив в регистре флагов бит ZF (флаг нуля) Если попытаться сложить два больших числа (например, 50000 и 60000), то установится флаг переноса CF, так как число 110000, получающееся в результате сложения, должно занять больше двоичных разрядов, чем помещается в регистрах или ячейках памяти, и возникает "перенос" старшего бита этого числа в бит CF регистра флагов. Индицирующие флаги процессора дают возможность проанализировать, если это нужно, результат последней операции и осуществить "разветвление" программы.