Методика тестирования функциональных

advertisement

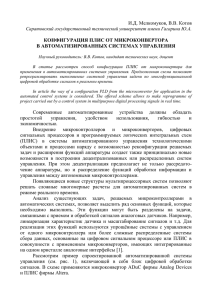

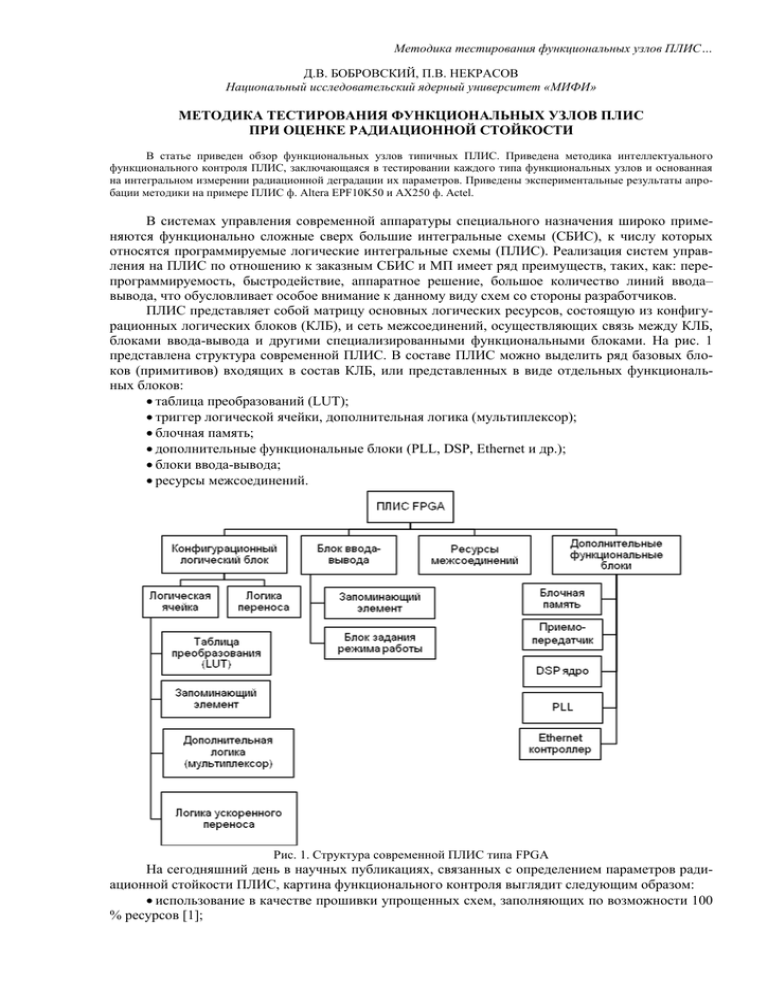

Методика тестирования функциональных узлов ПЛИС… Д.В. БОБРОВСКИЙ, П.В. НЕКРАСОВ Национальный исследовательский ядерный университет «МИФИ» МЕТОДИКА ТЕСТИРОВАНИЯ ФУНКЦИОНАЛЬНЫХ УЗЛОВ ПЛИС ПРИ ОЦЕНКЕ РАДИАЦИОННОЙ СТОЙКОСТИ В статье приведен обзор функциональных узлов типичных ПЛИС. Приведена методика интеллектуального функционального контроля ПЛИС, заключающаяся в тестировании каждого типа функциональных узлов и основанная на интегральном измерении радиационной деградации их параметров. Приведены экспериментальные результаты апробации методики на примере ПЛИС ф. Altera EPF10K50 и AX250 ф. Actel. В системах управления современной аппаратуры специального назначения широко применяются функционально сложные сверх большие интегральные схемы (СБИС), к числу которых относятся программируемые логические интегральные схемы (ПЛИС). Реализация систем управления на ПЛИС по отношению к заказным СБИС и МП имеет ряд преимуществ, таких, как: перепрограммируемость, быстродействие, аппаратное решение, большое количество линий ввода– вывода, что обусловливает особое внимание к данному виду схем со стороны разработчиков. ПЛИС представляет собой матрицу основных логических ресурсов, состоящую из конфигурационных логических блоков (КЛБ), и сеть межсоединений, осуществляющих связь между КЛБ, блоками ввода-вывода и другими специализированными функциональными блоками. На рис. 1 представлена структура современной ПЛИС. В составе ПЛИС можно выделить ряд базовых блоков (примитивов) входящих в состав КЛБ, или представленных в виде отдельных функциональных блоков: таблица преобразований (LUT); триггер логической ячейки, дополнительная логика (мультиплексор); блочная память; дополнительные функциональные блоки (PLL, DSP, Ethernet и др.); блоки ввода-вывода; ресурсы межсоединений. Рис. 1. Структура современной ПЛИС типа FPGA На сегодняшний день в научных публикациях, связанных с определением параметров радиационной стойкости ПЛИС, картина функционального контроля выглядит следующим образом: использование в качестве прошивки упрощенных схем, заполняющих по возможности 100 % ресурсов [1]; Методика тестирования функциональных узлов ПЛИС… использование прошивки выполняющей функцию для реальных применений; информация о тестовых прошивках не доступна и является научным достоянием соответствующей научной группы [2]. Таким образом, в условиях радиационного эксперимента возможно применение следующих методик. Первая заключается в прошивке в ПЛИС схемы, заполняющей по возможности 100 % ресурсов, и контроле нескольких тестовых выходов. Такой схемой, как правило, служит многоразрядный счетчик или сдвиговый регистр. Наличие сигнала заданной частоты говорит о правильном функционировании ПЛИС. Вторая методика заключается в применении в качестве тестовой прошивки той, которая будет использоваться в реальных условиях работы. Такая схема как правило, использует все типы ресурсов ПЛИС и позволяет определить уровень радиационной стойкости, но не дает возможности выявить отказавшие блоки и оценить деградацию их характеристик. Третий вариант – использование интеллектуального теста и оригинальной прошивки, контролирующей все блоки ПЛИС, учитывающей специфику вида радиационного воздействия и соответствующих ему радиационных эффектов в микросхеме. Для этого необходимо разработать набор тестовых схем, позволяющих проводить функциональный контроль всех примитивов ПЛИС и оценивать деградацию характерных параметров каждого из них. Применение такой методики позволит, кроме уровня радиационной стойкости, определить блок, являющийся причиной отказа, и выявить наиболее критичные узлы. При разработке интеллектуального теста необходимо учитывать следующие требования: универсальность – возможность быстрого переноса на ПЛИС различных производителей и типов; полнота тестирования – достоверное определение момента функционального отказа и отказавшего блока; скорость проведения теста – время функционального контроля не должно превышать 1 с; учет вида радиационного воздействия и характерных эффектов. Этим требованиям удовлетворяет предложенная методика функционального контроля каждого типа примитивов ПЛИС независимо друг от друга. Для реализации методики создана библиотека тестовых блоков функционального контроля примитивов ПЛИС. Создание такой библиотеки на языке VHDL позволяет легко переходить между ПЛИС различных производителей. Раздельное тестирование обеспечивает достоверное определение отказавшего блока за счет набора статистики по большому количеству (сотни, тысячи) элементов каждого вида примитивов, а также гибкость при формировании состава и объема функционального контроля в зависимости от доступных ресурсов ПЛИС. Деградацию временных характеристик, например, времени переключения триггера, измерить прямым способом затруднительно, так как она составляет десятки пикосекунд. Для решения этой задачи используется методика, основанная на оценке интегрального вклада деградации параметра от нескольких однотипных примитивов, таким образом увеличивается точность оценки и уменьшаются требования к измерительной аппаратуре. Для определения оптимальной прошивки ПЛИС при проведении радиационных исследований было проведено сравнение двух методик: функциональный контроль с прошивкой, использующей по возможности 100 % ресурсов ПЛИС, например многоразрядный счетчик; интеллектуальный функциональный контроль ПЛИС. Прошивка реального устройства в ПЛИС не рассматривается из-за недостатка, связанного с невозможностью определить отказавший блок. Рассмотрим примеры реализации тестовых блоков некоторых примитивов ПЛИС. Для контроля функционирования запоминающих элементов логических ячеек, предлагается схема кольцевого генератора, приведенная на рис. 2. Применение такой схемы позволяет интегрально оценить деградацию времени переключения триггера. По количеству триггеров в цепочке и частоте генерации определяется время переключения одного триггера. Для контроля функционирования мультиплексоров применяется схема, в которой только при одном наборе управляющих сигналов на выходе присутствует низкий логический уровень, при всех остальных наборах на выходе – высокий логический уровень. Подача соответствующих управляющих сигналов, приводящих к переключению выхода, позволяет контролировать переключение всех мультиплексоров цепочки. Методика тестирования функциональных узлов ПЛИС… Vcc ОС_вход Старт D D D D D CLK Q CLK Q CLK Q CLK Q CLK Q R R R R R ОС_выход Рис. 2. Схема для контроля функционирования триггеров логических ячеек При проведении функционального контроля блочной памяти и LUT, сконфигурированной в режиме блока памяти, формируется блок памяти максимально доступного объема, в который последовательно записывается тестовый код (AA/55), считывается, сравнивается с эталонным и фиксируются возникающие сбои. При тестировании дополнительных функциональных блоков реализуется типовая схема включения соответствующего узла, позволяющая сконфигурировать его и обеспечить доступ к интерфейсу через внешние порты. Например, при тестирования PLL на тестовых выводах ПЛИС контролируется наличие увеличенной и уменьшенной относительно опорной частот. Функциональный контроль межсоединений проводится по косвенным признакам: функционирование прошивки и возможность реконфигурирования ПЛИС. Аппаратная часть эксперимента построена на базе оборудования National Instruments. И включает в себя PXI шасси с установленными платами цифро-аналогового ввода-вывода и управляемым источником питания, а также универсальной платы коммутации, служащей для сопряжения микросхемы непосредственно с платами ввода-вывода. Программное обеспечение реализовано в оболочке LabView 8.6 и представляет собой виртуальный прибор, осуществляющий полное управление ходом эксперимента, включающее, кроме функционального контроля, управление источником радиационного воздействия и проведение параметрического контроля ПЛИС. Параметрический контроль заключается в измерении тока потребления схемы, напряжения высокого и низкого логических уровней. Программное обеспечение позволяет наглядно наблюдать ход тестирования, возникающие ошибки и вести протокол результатов эксперимента. В качестве объектов исследований при апробации методики были: EPF10K50 – ПЛИС ф. Altera, содержащая 360 КЛБ, 20480 бит блочной памяти; AX250 – однократно программируемая ПЛИС ф. Actel, выполненная по Antifuse технологии, содержащая 250000 логических вентилей, 55296 бит встроенной блочной памяти и 8 блоков PLL. В ПЛИС AX250 наиболее критичным к воздействию стационарного ионизационного излучения был блок PLL. На рис. 3 показан график зависимости выходной частоты PLL от накопленной дозы. Уровень отказа составил 200 условных единиц, при этом многоразрядный счетчик продолжал функционировать вплоть до предельного уровня 300 условных единиц. В результате исследований ПЛИС EPF10K50 была зафиксирована деградация частоты генерации кольцевого генератора. На рис. 4 представлена зависимость времени переключения от накопленной дозы. Отказ определялся изменением времени переключения более чем на 10 %. Кроме деградации триггеров, наблюдались сбои в блочной памяти. Методика тестирования функциональных узлов ПЛИС… fPLL, кГц 30 20 10 Доза, усл. Доза, усл. Рис. 3. График зависимости выходной частоты PLL Рис. 4. График зависимости времени переключения ед. ед. от накопленной дозы ПЛИС AX250 триггера от накопленной дозы ПЛИС EPF10K50 В таблице представлено сравнение двух вариантов функционального контроля ПЛИС при проведении радиационных исследований, из которого видно, что тестирование ПЛИС с прошивками типа "счетчик", "сдвиговый регистр" дает завышенный уровень стойкости по сравнению с тестированием каждого примитива в отдельности. Триггер Мультиплексор Блочная память Доза, ед. Счетчик Блочная память PLL Триггер 20 + + + + + 180 + + + + 24 + + + + + 200 + + + + 28 + + + + ─ 220 + + ─ + 32 + + + + ─ 240 + + ─ + 36 + + ─ + ─ 260 + + ─ + 40 + + ─ + ─ 300 + + ─ + Сдвиговый регистр Счетчик AX250 Доза, ед. EPF10K50 СПИСОК ЛИТЕРАТУРЫ 1. MacQueen D. M., Gingrich D. M., Buchanan N. J. et al. Total Ionizing Dose Effects in a SRAM-Based FPGA // Radiation Effects Data Workshop, 1999. P. 24. 2. AT40KEL040 Reprogrammable SRAM based FPGA Total Dose (TID) and Single Event Effects (SEE) http://www.klabs.org/richcontent/fpga_content/atmel/at40kel_tid_see_summary.pdf