Тема 8 Последовательностные цифровые устройства (ПЦУ)

advertisement

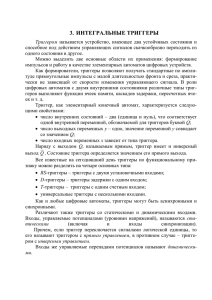

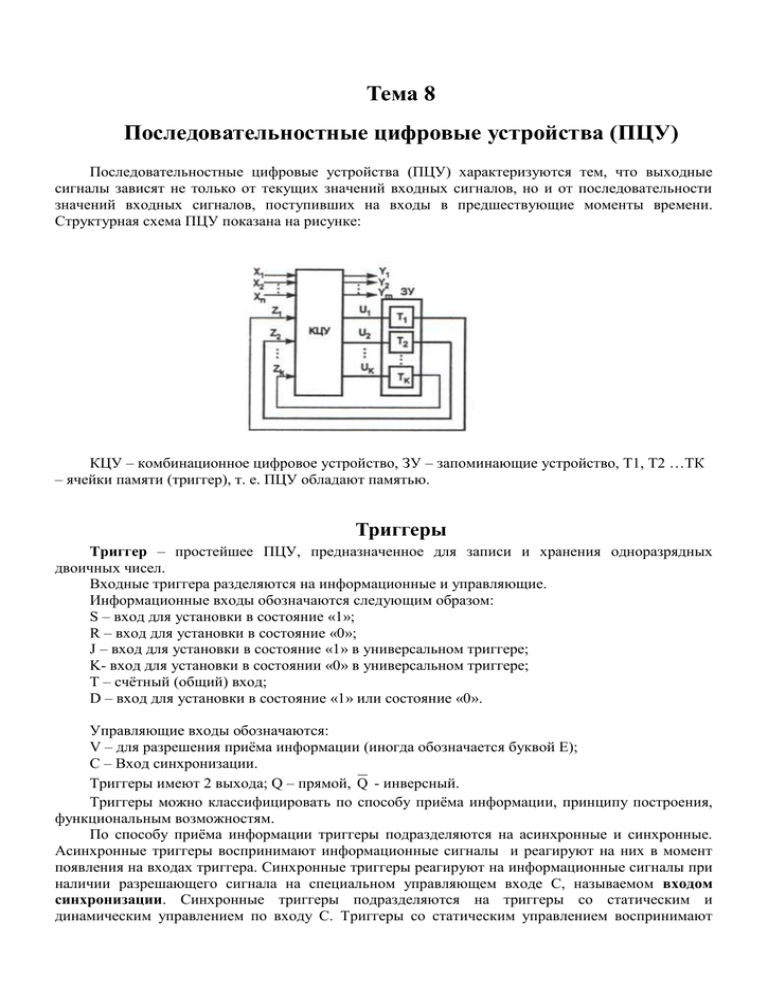

Тема 8 Последовательностные цифровые устройства (ПЦУ) Последовательностные цифровые устройства (ПЦУ) характеризуются тем, что выходные сигналы зависят не только от текущих значений входных сигналов, но и от последовательности значений входных сигналов, поступивших на входы в предшествующие моменты времени. Структурная схема ПЦУ показана на рисунке: КЦУ – комбинационное цифровое устройство, ЗУ – запоминающие устройство, Т1, T2 …ТК – ячейки памяти (триггер), т. е. ПЦУ обладают памятью. Триггеры Триггер – простейшее ПЦУ, предназначенное для записи и хранения одноразрядных двоичных чисел. Входные триггера разделяются на информационные и управляющие. Информационные входы обозначаются следующим образом: S – вход для установки в состояние «1»; R – вход для установки в состояние «0»; J – вход для установки в состояние «1» в универсальном триггере; K- вход для установки в состоянии «0» в универсальном триггере; Т – счётный (общий) вход; D – вход для установки в состояние «1» или состояние «0». Управляющие входы обозначаются: V – для разрешения приёма информации (иногда обозначается буквой Е); С – Вход синхронизации. Триггеры имеют 2 выхода; Q – прямой, Q - инверсный. Триггеры можно классифицировать по способу приёма информации, принципу построения, функциональным возможностям. По способу приёма информации триггеры подразделяются на асинхронные и синхронные. Асинхронные триггеры воспринимают информационные сигналы и реагируют на них в момент появления на входах триггера. Синхронные триггеры реагируют на информационные сигналы при наличии разрешающего сигнала на специальном управляющем входе С, называемом входом синхронизации. Синхронные триггеры подразделяются на триггеры со статическим и динамическим управлением по входу С. Триггеры со статическим управлением воспринимают информационные сигналы при подаче на С – вход уровня 1 (прямой С – вход). Триггеры с динамическим управлением воспринимают формационные сигналы при изменении сигнала на С входе от 0 к 1(прямой динамический С – вход) или от 1 к 0 (инверсный динамический С – вход). По принципу построения триггеры со статическим управлением делятся на одноступенчатые и двух ступенчатые. Одноступенчатые триггеры характеризуются наличием одной ступени запоминания информации, двухступенчатые триггеры имеют две ступени запоминания информации. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе. Двухступенчатый триггер обозначают через ТТ. По функциональным возможностям триггеры разделяются на следующие классы: с раздельной установкой состояния 0 и 1 (RS – триггеры); универсальные (JK – триггеры) с приемом информации по одному входу D (D-триггеры) со счётным входом Т (Т – триггеры). Независимо от вида, если Q = 1 и Q = 0, то триггер находится в единичном состоянии. При Q = 0, Q = 1 состояние триггеры называется нулевым. Ниже приведены графические обозначения (УГО) триггеров, принятые в системе ЕСКД: А) асинхронный RS – синхронный триггер; Б) синхронизируемый RS – триггер. Синхронизация производится логическим 0; В) D – триггер, срабатывающий на передний фронт 0,1; Г) JK – триггер, срабатывающий по фронту 1, 0; Д) Т – триггер, срабатывающий по фронту 1, 0; Е) двухступенчатый JK – триггер со входами разделённой установки в нулевое (R) и единичное (S) состояние. Функционирование триггеров описывается таблицами переходов (истинности): «ИСХ» - означает режим хранения (исходное состояние или без изменения). «НЕОПР» - означает, что состояние выходов неопределённое, т. е. комбинация сигналов R = S = 1 является запрещённой. Вт – триггере при Т = 1 триггер переходит в инверсивное состояние n – 1 (счётный режим). В JK – триггере при J = K = 1 триггер переходит в инверсное состояние n – 1 (счётный режим). Qn – 1 – состояние выхода, предшествующее появлению информационных сигналов. Регистры Регистр – это последовательное логическое устройство, используемое для хранения n – разрядных двоичных чисел и выполнения преобразований над ними. Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове (обычно от 4 до 16). На схемах регистры обозначаются буквами RG. Регистр обеспечивает выполнение следующих типичных операций: - приём слова в регистр; - передача слова из регистра; - поразрядные логические операции; - сдвиг слова влево или вправо на заданное число разрядов; - преобразование последовательного кода слова в параллельный и обратно; - установка регистра в начальное состояние (сброс). Регистры классифицируются по следующим видам: накопительные (регистры памяти, хранения); сдвигающие в свою очередь сдвигающие регистры делятся: по способу ввода-вывода информации на - параллельные, - последовательные, - комбинированные; по направлению передачи информации на - однонаправленные, - реверсивные. Структура параллельного регистра показана на рисунке: Основой его являются D – триггеры. Каждый из триггеров имеет свой независимый информационный вход (D) и свой независимый информационный выход. Тактовые входы (С) всех триггеров соединены между собой. В результате параллельный регистр представляет собой многоразрядный, многовходовый триггер. D – триггеры на своих выходах повторяют значения сигналов на входах D0 – Dn (информационные входы) при действии управляющего сигнала С, т. е. осуществляется параллельный ввод входной информации в регистр. В стандартные серии входит несколько типов параллельных регистров, срабатывающих по фронту: Различаются регистры количеством разрядов, наличием или отсутствием входа сброса (-R) или разрешения записи (-WE), а также типом выходных каскадов (2С или 3С) и соответственно наличием или отсутствием входа разрешения –EZ. Иногда на схемах тактовый вход С обозначается WR – сигнал записи в регистр. Представление цифровых данных, каждому биту которых выделена отдельная линия шины, называется параллельным кодом. На рисунке показаны параллельные входной и выходной коды, передача которых осуществляется одновременно по всем выделенным линиям. Структура сдвигового регистра показана на рисунке: В сдвиговых регистрах все триггеры соединены в последовательною цепочку (выход каждого предыдущего триггера соединён со входом D следующего триггера). Тактовые входы всех триггеров (С) объединены между собой. В результате такой триггер может рассматриваться как линия задержки, входной сигнал которой последовательно перезаписывается из триггера в триггер по фронту тактового сигнала С. В сдвиговом регистре цифровой код представляется временным рядом логических уровней, соответствующих значениям разрядов. Такой код называется последовательным. Каждый бит этого кода передаётся по одной и той же линии. В качестве примера приведем микросхему сдвигающего регистра и его таблицу состояний: Микросхема К155ИР13 является универсальным восьмиразрядным реверсивным сдвигающим регистром и может работать в режимах последовательного ввода информации со сдвигом вправо или в лево, параллельного ввода информации, хранения информации, сброса (установки нулей). Микросхема имеет следующий вход: D1 – D8 – для параллельного ввода информации, DR и DL – информационные входы для последовательного ввода информации при сдвиге соответственно вправо или влево, входы S1 и S0 – для выбора режима работы, R – вход сброса триггеров регистра в нулевое состояние и С – вход синхронизации. Сброс триггеров осуществляется при подаче логического 0 на вход R. При S1 = 0 и S0 = 1 осуществляется последовательный ввод информации со входа DR в первый разряд регистра со сдвигом вправо. При S1 = 1, S0 = 0 осуществляется последовательный ввод информации со входа DL в восьмой разряд регистра со сдвигом влево. При S1 = S0 = 1 осуществляется параллельная запись информации со входов D1 – D8 при воздействии положительного перепада на входе синхронизации С. При S1 = S0 = 0 осуществляется режим хранения информации. Счётчики Счётчики представляют более высокий, чем регистры, уровень сложности цифровых микросхем, имеющих внутреннюю память. Хотя в основе любого счётчика лежат те же самые триггеры, которые образуют и регистры, но в счётчиках триггеры соединены более сложными связями, в результате чего их функции сложнее, и на их основе можно строить более сложные устройства, чем на регистрах. Точно так же, как и в случае регистров, внутренняя память счётчиков – оперативная, то есть её с одержимое сохраняется только до тех пор, пока включено питание схемы. Как следует из самого названия счётчик импульсов – это последовательностное цифровое устройство, обеспечивающее хранение слова информации и выполняющего над ним микрооперации счёта, заключающейся в изменении значения числа в счетчике на 1. Основной параметр счётчика – модуль счёта. Это максимальное число единичных сигналов, которое может быть сосчитано счётчиком. Счётчики обозначаются через СТ (от англ. Counter). Счетчики классифицируют: По модулю счёта: двоично – десятичные; двоичные; с произвольным постоянным модулем счёта; по направлению счёта: суммирующие; вычитающие; реверсивные; Рассмотрим работу 4 – разрядного двоичного счётчика: Счётчик обычно реализуется на Т – триггерах, но могут быть использованы и Д -, JK – триггеры. Выходы счётчика (вых. 1 - вых. 4) представляют собой выходы 4 – х триггеров (разряды двоичного кода). 4 – х разрядный счётчик в режиме прямого счёта будет считать от 0 (0000) до 15 (код 1111). После кода 1111 по следующему входному импульсу переключается опять в 0 (код 0000), т. е. работает по кругу. Структурная схема временные диаграммы графическое обозначение 3 – х разрядного суммирующего счётчика показаны на рисунке: В этой схеме исходное состояние счётчика устанавливается подачей сигнала по шине Уст. 0. Триггеры Т изменяют своё состояние с окончанием входного сигнала, т. е. после перехода от уровня 1 к 0. Входной сигнал по шине C0 подаётся на счётный вход триггера 1. Работа счётчика может быть описана с помощью временной диаграммы, иллюстрирующей состояние каждого триггера. Общее число возможных состояний (модуль Кси) определяется числом триггеров n: Кси = 2 n . В нашем случае n = 3, Кси = 8. Обозначение СT2 означает двоичный счётчик, выходы 1, 2, 4, (Q1, Q2, Q3) – обозначение двоичных разрядов ( 2 0 = 1, 21 = 2, 2 2 = 4 ). Для получения вычитающего счётчика необходимо вход каждого последующего триггера соединить с инверсным выходом предыдущего: Вычитающий счётчик реализует микрооперацию изменения числа в счётчике на «-1», т. е. с приходом очередного счётного сигнала результат уменьшается на единицу. Он будет считаться от кода 111 до кода 000. В реверсивном счётчике счётные сигналы поступают через логические элементы, управляющие направлением счёта (суммирование или вычитание). Графическое обозначение реверсивного счётчика показано на рисунке: Если счётчик работает как суммирующий, то сигналы счёта подают на вход + 1; если он работает как вычитающий, то сигнал счёта подают на вход -1. На выходе счётчика, обозначенном > 15, сигнал появляется при переходе счётчика в состояние с номером 15, в котором все триггеры установлены в состояние 1. На этом выходе формируется сигнал переноса в следующий счётчик. На выходе < 0 сигнал появляется при заполнении счётчика нулями: это сигнал займа в следующий счётчик в схеме вычитающего счётчика. Для получения счётчика, работающего в другом коде, например десятичном, применяют обратные связи: Обозначение СТ10 означает десятичный счётчик импульсов на 4 – х триггерах. С выхода триггера Т4 сигналы обратной связи поступают на входы триггеров Т2, Т3. Благодаря этому после поступления на вход счётчика восьмого импульса на выходе триггера Т4 появляется сигнал «1», который переводит триггеры Т3, Т2 из состояния «0» в состояние «1». Девятый импульс переводит триггер Т1 в состояние «1», и все триггеры оказываются в состояние «1». Десятый импульс переводит все триггеры в состояние «0», и счёт начинается снова. Работа десятичного счётчика может быть проиллюстрирован таблицей переходов: Используя обратные связи, можно построить счётчик, работающий в системе счисления с любым основанием, с произвольным постоянным модулем счёта, с переменным модулем счёта, кольцевые. Цифровые запоминающие устройства (ЗУ) Цифровые запоминающими называют устройства, предназначены для записи, хранения и считывания информации, представленной в цифровом коде. Они представляют собой более сложные цифровые устройства по сравнению с рассмотренным ранее. Каждый код хранится в отдельном элементе, называемом ячейкой памяти. К основным параметром запоминающих устройств (ЗУ) относятся информационная ёмкость, потребляемая мощность, время хранения кодов, быстродействие. Информационная ёмкость – это объём памяти, т. е. количество кодов (m) которые могут в ней храниться, и разрядность этих кодов (n). Информационная ёмкость N определяется выражением: N = n ∙ m. Для обозначения количества ячеек памяти используется следующие специальные единицы измерения: 1К – это 1024, то есть 1М – это 1048576, то есть (читается «кило-» или «ка-»), при мерно равно одной тысяче; (читается «мега-»), примерно равно одному миллиону; 1Г – это 1073741824, то есть (читается «гига-»), примерно равно одному миллиарду. Принцип организации памяти записывается следующим образом: сначала пишется количество ячеек, а затем через знак умножения (косой крест) пишется разрядность кода, хранящегося в одной ячейке. Например, организация памяти 64К х 8 означает, что память имеет 64К (то есть 65536) ячеек и каждая ячейка – восьмиразрядная. Информационная ёмкость N = 65536 ∙ 8 = 524288 бит. Потребляемая мощность – мощность, потребляемая ЗУ в установившемся режиме работы. Время хранения информации – интервал времени, в течение которого ЗУ сохраняет информацию в заданном режиме. Быстродействие – промежуток времени, необходимый для записи или считывания информации. В зависимости от способа занесения (записи) информации и от способа хранения информации микросхемы памяти разделяются на следующие три основные типы: Постоянная память (ПЗУ – постоянное запоминающее устройство, ROM – Read Only Memory - память только для чтения), в которую информация заносится один раз на этапе изготовления микросхемы. Такая память называется ещё масочным ПЗУ. Информация в памяти не пропадает при выключении её питания, поэтому её ещё называются энергонезависимой памятью. Программируемая постоянная память (ППЗУ – программируемое ПЗУ, PROM – Programmable ROM), в которую информация может заносится пользователем с помощью специальных методов (ограниченное число раз). Информация в ППЗУ тоже не пропадает при включении её питания, то есть она также энергозависимая. Оперативная память (ОЗУ – оперативное запоминающие устройство, RAM – Random Access Memory – память с произвольном доступом), запись информацию в которую наиболее проста и может производится пользователем сколько угодно раз на протяжении срока службы микросхемы. Информация в памяти пропадает при выключении её питания. Существует множество промежуточных типов памяти, а также множество подтипов, но указанные типы самые главные, принципиально отличающиеся друг от друга. Хотя разница между ПЗУ и ППЗУ с точки зрения разработчика цифровых устройств, как правило, не так уж велика, но в отдельных случаях, например, при использовании так называемой флеш – памяти (flashmemory), представляющей собой ППЗУ с многократным электрическим стиранием и перезаписью информации, эта разница действительно чрезвычайно важна. Можно считать, что флеш – память занимает промежуточное положение между ОЗУ и ПЗУ. В общем случае любая микросхема памяти имеет следующие информационные выводы: а – ПЗУ, б – ОЗУ с двунаправленной шиной данных, в – ОЗУ с раздельными шинами входных и выходных данных. Адресные выводы (входные), образующие шину адреса памяти. Код на адресных линиях представляет собой двоичный номер ячейки памяти, к которой происходит обращение в данный момент. Количество адресных разрядов определяет количество ячеек памяти: при количестве адресных разрядов n количество ячеек памяти равно 2 n Вывод данных (выходные), образующие шину данных памяти. Код на линиях данных представляет собой содержимое той ячейки памяти, к которой производится обращение в данный момент. Количество разрядов данных определяет количество разрядов всех ячеек памяти (обычно оно бывает равным 1, 4, 8, 16). Как правило, выходы данных имеют тип выходного каскада ОК или 3С. В случае оперативной памяти помимо выходной шины данных может быть ещё и отдельная входная шина данных, на которую подаётся код, записываемый в выбранную ячейку памяти. Другой возможный вариант – совершение входной и выходной шин данных, то есть двунаправленная шина данных, направление передачи информации по которой определяется управляющими сигналами СS, WR. Управляющие выводы (входные), которые определяют режим работы микросхемы. В большинстве случаев у памяти имеется вход выбора микросхемы CS (их может быть несколько, объединенных по функции И). У оперативной памяти также обязательно есть вход записи WR, активный уровень сигнала на котором переводит микросхему в режиме записи. Оперативные запоминающие устройства ОЗУ (RAM) подразделяются на статически и динамические. Каждая ячейка оперативной (статической) памяти представляет собой, по сути, регистр из триггерных ячеек, в который может быть записана информация и из которой можно информацию читать. Выбор того или иного регистра (той или иной ячейки памяти) производится с помощью кода адреса памяти. Поэтому при выключении питания вся информация из оперативной памяти пропадает (стирается). Рассмотрим в качестве примера микросхему К537РУ8: Микросхема К537РУ8 – это статическое ОЗУ объёмом 2 Кбайта, выполнена на основе структур КМОП, по входу и выходу совместима с ТТЛ – структурами. Имеет двунаправленную 8 – разрядную шину данных, которая используется для записи, и для считывания информации. Тип выхода – ЗС. Управляющие сигналы имеют следующие назначения: CS – выбор микросхемы; А – адресные входы; Д – информационные входы/выходы, W/R – разрешение записи / считывания, СЕ – сигнал разрешения. В динамических ОЗУ элементом памяти является ёмкость (например, входная ёмкость полевого транзистора), что требует периодического восстановления (регенерации) записанной информации в процессе её хранения. ОЗУ динамического типа позволяют реализовать большой объём памяти, но они сложнее в использовании, так как необходимо наличие специальной схемы управления режимами работы. В современных динамических ОЗУ имеются встроенные системы регенерации и синхронизации. Такие ОЗУ по внешнему сигналу управления не отличаются от статических ОЗУ: Микросхем К565РУ5 – это динамическое ОЗУ на основе n – МОП – структур, по входам и выходам совместима с ТТЛ – структурами, имеет организацию 64К х 1. Шина адреса работает в мультиплексорном режиме. Вначале на ней выставляются адреса строк, которые запоминаются во внутреннем регистре по спаду сигнала RAS. Затем выставляются адреса столбцов, которые запоминаются по спаду сигнала CAS. DI – информационные входы, D0 – информационные выходы. Тип выхода – 3С. Микросхема отличается низкой стоимостью, меньшим быстродействием, необходимостью регулярной регенерации информации (т.к. конденсаторы со временем разряжаются). Имеет ограниченное применение. Главное применение микросхем оперативной памяти, непосредственно следующие из её названия, - это временное хранение цифровой информации, всевозможных массивов кодов, таблиц данных, одиночных чисел и т. д. Цель такого хранения информации состоит в том, чтобы в любой момент иметь возможность быстро её прочитать для дальнейшей обработки, записи в энергонезависимую память (в ПЗУ, на магнитные носители) или для другого исполнения. Постоянные запоминающие устройства В ПЗУ информация заносится раз и навсегда. ПЗУ можно разделить на следующие группы: Программируемые при изготовление (обозначают как ПЗУ или ROM); С однократным программированием, позволяющим пользователю однократно изменить состояние матрицы памяти электрическим путём по заданной программе (обозначают как ППЗУ или PROM); Перепрограммируемые (репрограммируемые), с возможностью многократного электрического перепрограммирования, с ультрафиолетовым (обозначают как РПЗУУФ или EPROM) или электрическим (обозначают как РПЗУЭС или EEPROM, или E 2 PROM ) cтиранием информации. Рассмотрим в качестве примера микросхему ПЗУ К155РЕ3: Микросхема К155РЕ3 представляет собой однократно программируемое ППЗУ с организацией 32 х 8. Исходное состояние (до программирования) – все биты всех ячеек нулевые. Для программирования (записи информации) используется специальный программатор, подающий на разряды данных импульсы высокого напряжения. Тип выходных каскадов – открытый коллектор, то есть обязательно надо включать на выходах резисторы, подсоединенные к шине питания. Имеется один управляющий вход –CS.