литература - MES conference

advertisement

ПРИНЦИПЫ ПОСТРОЕНИЯ СПЕЦИАЛИЗИРОВАННЫХ

ВЫЧИСЛИТЕЛЕЙ С ПРИМЕНЕНИЕМ МОДУЛЯРНОЙ

АРИФМЕТИКИ

А.И. Корнилов, М.Ю. Семенов, О.В. Ласточкин, В.С. Калашников

Институт проблем проектирования в микроэлектронике РАН, kvs@ici.ru

Существуют различные методы повышения быстродействия арифметических устройств. Так,

например, уменьшение проектных норм технологии приводит к повышению степени интеграции схем

и, соответственно, увеличению тактовых частот. Применение специализированных алгоритмов также

позволяет значительно улучшить производительность как отдельных блоков, так и устройства в

целом.

Один из возможных методов увеличения быстродействия систем связан с

распараллеливанием вычислительных операций. Модулярное представление (которое также

называют представлением в системе остаточных классов или системе классов вычетов) является

одним из возможных способов построения параллельных вычислительных архитектур. Для ряда

специализированных применений аппарат модулярной арифметики в совокупности с двоичной

арифметикой может быть использован с целью повышения эффективности таких устройств.

Как в нашей стране, так и за рубежом предпринимались довольно успешные попытки

построения вычислителей, функционирующих на основе аппарата модулярной арифметики. В 70-80-е

годы были проведены значительные теоретические исследования в этой области [1, 2, 3] и разработан

ряд высокоэффективных вычислительных систем на их основе. Однако это направление

сдерживалось несовершенством элементной базы, а также методологией проектирования устройств,

принципиально ориентированных в то время на двоичную систему счисления.

Современное развитие интегральной схемотехники позволяет по-новому взглянуть на

принципы построения устройств с применением модулярной арифметики и предоставляет широкие

возможности по использованию новых методов проектирования (например, методология

проектирования систем на кристалле – SoC) как при разработке отдельных вычислительных блоков,

так и систем в целом. Интегральная технология дает возможность более гибкого проектирования и

позволяет реализовывать устройства на основе модулярной арифметики столь же эффективно, как и

на основе двоичной системы счисления. Кроме того, в настоящее время широкое распространение

получили различного рода системы автоматизированного проектирования (САПР) для повышения

эффективности разработки устройств. В этом отношении, проектирование устройств на основе

модулярной арифметики также ничем не отличается от разработки с помощью данных САПР

двоичных блоков.

Следует заметить, что в предлагаемом подходе модулярная арифметика не

противопоставляется двоичной, а служит как бы ее расширением, позволяющим эффективно решать

определенный класс специализированных задач. Поэтому наиболее эффективным, в данном случае,

представляется подход, сочетающий в себе комбинированное применение модулярной арифметики и

двоичной системы счисления при построении управляющих систем. При этом, например, управление

всей системы может осуществляться обычными двоичными командами и блоками, а обработка

данных выполняется на основе модулярного представления. Таким образом, использование

достоинств и преимуществ модулярной арифметики, наряду с традиционными двоичными методами

построения управляющих систем, приводит к повышению производительности устройства в целом.

Перед тем, как определить класс задач, для которых применим данный математический

аппарат, необходимо проанализировать преимущества и недостатки использования модулярной

арифметики.

Рассмотрим принципы представления целых чисел в модулярной арифметике. При

организации вычислений с применением модулярной арифметики любое целое число представляется

как упорядоченный набор остатков в соответствующем базисе взаимно попарно простых чисел,

называемых модулями. Положим, положительное целое число А находится в диапазоне 0 А N и

пусть {m1, m2 ,, m p } является исходным базисом взаимно попарно простых модулей. При этом

произведение модулей M должно перекрывать диапазон представления числа А , т.е.

p

M i 1 m N - это область чисел, над которыми можно выполнять операции модулярной

i

арифметики. В этом случае, целое число А однозначно представляется соответствующим набором

вычетов в соответствии с формулой (1):

346

{m1, m2 ,..., m p }

A

{a1 , a2 ,..., a p }

где

(1)

ai A m для i 1,2,, p .

i

Отрицательные целые числа также имеют модулярное представление, но при этом диапазон

представления таких чисел соответствует интервалу, симметричному относительно нуля. Для

отрицательного числа вычисляется его дополнение до M , а затем это дополнение представляется в

модулярном виде согласно формуле (1).

Арифметические операции сложения, вычитания и умножения могут быть легко выполнены,

если их результаты заключены между 0 и произведением модулей M . В этом случае, для двух

операндов А и B , представленных соответствующими наборами вычетов {a1, a2 ,, a p } и

{b1, b2 ,, b p } и, обозначив символом "◊" любую из операций сложения, вычитания и умножения,

получим:

AB a1, a2 ,..., a p b1, b2 ,..., b p y1, y2 ,..., y p Y

(2)

где yi ai bi

.

mi

Как видно из формулы (2), арифметические операции сложения, вычитания и умножения

выполняются с вычетами существенно меньшей разрядности, по сравнению с исходными данными, и

независимо друг от друга.

Таким образом, можно выделить два основных "естественных" преимущества модулярного

представления:

- во-первых, арифметические операции сложения, вычитания и умножения выполняются без

переносов, в отличие от обычного позиционного представления чисел;

- во-вторых, для каждого значения модуля m i арифметические операции выполняются с

парой соответствующих вычетов малой разрядности параллельно и независимо друг от друга, а

процесс вычислений с данными малой разрядности естественным образом обеспечивает увеличение

быстродействия всего устройства.

Наряду с указанными основными достоинствами модулярной арифметики можно выделить

ряд преимуществ, относящихся к интегральному исполнению устройств, реализованных с

применением аппарата модулярной арифметики [4]:

- независимость каждого канала по отдельному модулю обеспечивает значительную гибкость

при топологическом проектировании и планировке кристалла;

- трассировочные межсоединения распространяются только внутри отдельного канала для

каждого модуля, что исключает наличие длинных трасс и, как следствие, обеспечивает некоторое

уменьшение потребляемой мощности и уменьшение задержек по критическим путям;

- улучшается трассировка цепей тактовых частот внутри каналов для каждого модуля, при

этом цепи тактовых частот имеют меньшую расфазировку. Это, в свою очередь, приводит к

уменьшению пиковых выбросов по цепям синхронизации;

- реализация таких устройств на основе ПЛИС, обладающими меньшими вентильными

ресурсами, может быть легко перепланирована и размещена в несколько кристаллов;

- при необходимости, введение дополнительных избыточных каналов обеспечивает

возможность построения отказоустойчивых систем без полного дублирования.

Приведенные особенности интегрального исполнения устройств на основе модулярного

представления означают, что при их анализе и сравнении с обычным позиционным, нельзя

ограничиваться обычным сопоставлением по быстродействию и занимаемой площади. Необходимо

также учитывать указанные факторы, так как они очень важны при разработке

высокопроизводительных систем, в том числе функционирующих в реальном времени.

Теперь проанализируем более подробно, какие же недостатки присущи модулярному

представлению.

Одной из основных проблем является сложность выполнения операции деления. Отношение

A / B может не быть целым числом, а если и является таковым, то в общем случае нельзя найти его

модульное представление, вычисляя ai / bi по модулю m i для каждого i .

Также затруднительно выполнять операции сравнения для различных модулярных

представлений {a1, a2 ,, a p } и {b1, b2 ,, b p } . Это приводит к проблеме контроля переполнений

(т.е. проверке выхода результатов за пределы интервала от 0 до M ).

Следует отметить, что для обеспечения совместимости с существующими двоичными

системами и двоичным представлением данных, модулярные вычислители должны иметь,

347

соответственно, прямой преобразователь в модулярное представление и обратный преобразователь в

двоичную систему счисления. Преобразователи также могут вносить значительный вклад как в

аппаратные затраты, так и быстродействие таких устройств. Кроме того, основные модулярные

операции являются более сложными в реализации и затратными с точки зрения занимаемой площади

и быстродействия чем аналогичные двоичные.

Указанные недостатки значительно ограничивают лишь области применения модулярной

арифметики и поэтому такие системы редко реализуются в машинных блоках общего назначения. Но

можно выделить целый ряд специализированных приложений, реализация которых с применением

модулярной арифметики представляется наиболее эффективной. К таким приложениям, в общем

случае, относятся либо устройства, где основная доля вычисления приходится на операции

умножения в сочетании со сложением и вычитанием, либо системы повышенной надежности.

Приведем возможные области применения, где модулярное представление может быть эффективно

использовано:

- системы цифровой обработки сигналов (ЦОС), цифровые фильтры;

- специализированные вычислители для решения задач линейной алгебры;

- построение отказоустойчивых компьютерных систем;

- аппаратная реализация специализированных криптографических алгоритмов и систем,

построение специализированных блоков шифрования.

В данной работе авторы использовали модулярное представление при построении

специализированного вычислителя скалярных произведений. Вычисление скалярных произведений в

соответствии с формулой (3) является одной из основных операций в цифровой обработке сигналов:

y

N

ai xi

(3)

i 1

Системы такого типа охватывают довольно широкий класс устройств, в который входят как

различного рода нерекурсивные цифровые фильтры, так и вычислители, позволяющие решать задачи

линейной алгебры [5, 6]. Эффективное использование модулярной арифметики в данном случае

обусловлено особенностями архитектуры подобных устройств, а именно, линейной конвейерной

структурой вычислителей.

Вычисления в формуле (3) включают операции умножения и сложения, поэтому любое

представление чисел, обеспечивающее их более быстродействующую реализацию, вызывает

повышенный интерес разработчиков.

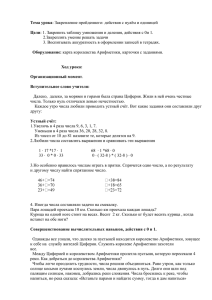

Рассмотрим обобщенную структуру устройства, реализующего формулу (3) и построенного с

применением аппарата модулярной арифметики (см. рис.1).

xi

Преобразователь в

модулярное представление

An

An-1

Z-1

A0

Z-1

Вычислитель по модулю m1

.

.

.

Z-1

Обратный преобразователь в

двоичную систему счисления

|Xi|m1

y

Вычислитель по модулю mp

Рис. 1. Обобщенная структура специализированного вычислителя с применением аппарата

модулярной арифметики

Общая структура модулярного вычислителя, включает следующие основные блоки:

- преобразователь из двоичного представления в модулярное представление;

- вычислители по каждому из модулей, выбранных для построения устройства;

348

- обратный преобразователь из модулярного представления в двоичную систему счисления.

Следует отметить, что в такой структуре прямое и обратное преобразование достаточно

выполнять только на входе и на выходе длинного конвейерного вычислительного блока, состоящего

из вычислителей, функционирующих параллельно. При этом основной объем вычислений

выполняется в модулярной арифметике и затраты на преобразование покрываются преимуществами,

предоставляемыми применением такого подхода.

Очевидно, что эффективность всего устройства во многом определяется характеристиками

отдельных его компонентов, а именно, методами реализации прямого и обратного преобразователей

из двоичного в модулярное представление и наоборот, а также основных вычислительных блоков модулярных сумматоров и умножителей. Поэтому при использовании предлагаемого подхода следует

уделять особое внимание выбору и реализации элементной базы для построения устройства, так как

неудачное исполнение его компонентов может свести на нет все преимущества, предоставляемые

модулярной арифметикой [7, 8].

Прямое преобразование из двоичного в модулярное представление может быть осуществлено

при помощи прямой перекодировки с использованием таблиц состояний (так называемых look-up

tables). Такой подход целесообразно применять при наличии ЗУ, а его использование для синтеза на

основе произвольной логики требует больших аппаратных затрат. Поэтому с целью уменьшения

занимаемой площади и минимизации таблиц, применяется комбинированный подход, основанный на

использовании таблиц состояний и модулярных сумматоров. Двоичное представление n-битного

числа X можно записать в соответствии с формулой (4):

X

n 1

bj 2 j

j 0

k

bj 2 j

j 0

n 1

b j 2 j

(4)

j k 1

где b j имеет значение 0 или 1 .

Для вычисления значения X по модулю m i формула (4) принимает вид:

Xm

i

n 1

b j 2

j 0

j

mi

k

mi b j 2

j 0

j

mi

mi

n 1

mi b j 2 j

j k 1

(5)

mi

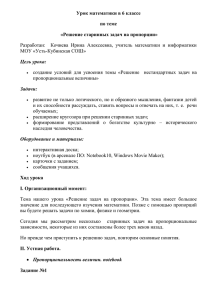

Структурная схема, соответствующая формуле (5) приведена на рис.2.

Look-up table 1

Двоичное

представление

Модулярное

представление

Look-up table 2

Рис. 2. Структурная схема преобразователя из двоичного в модулярное представление в

соответствии с формулой (5)

Приведенный алгоритм значительно уменьшает аппаратные затраты на реализацию таблиц

состояний, а модулярные сумматоры имеют значительно меньшую разрядность в соответствии с

выбранным базисом модулей по сравнению с разрядностью исходного числа X .

Кроме указанных существуют и другие методы построения блока прямого преобразования,

основанные на применении модулярных мультиоперандных сумматоров. При такой реализации в

зависимости от конкретного значения модуля таблицы состояний либо отсутствуют совсем, либо

используются только для финальной коррекции результата и имеют небольшой размер. В свою

очередь, модулярные мультиоперандные сумматоры строятся на основе известных принципов

построения аналогичных устройств в двоичной системе счисления, а именно с помощью сумматоров

с запоминанием переносов (carry-save adder) и компрессоров.

Обратное восстановление числа из модулярного представления в двоичную систему

счисления осуществляется по формуле (6), согласно следствию "Китайской теоремы об остатках":

349

X

p

xi ki1 M / mi

i 1

(6)

M

где ki1 определяется из условия ki1 M / mi

1.

mi

Математический алгоритм восстановления включает следующие стадии:

- вычисляется произведение модулей M ( M m1 m2 m p ) , при этом составной

модуль определяет динамический диапазон восстанавливаемых чисел;

- для набора модулей {m1, m2 ,, m p } вычисляется набор

структурных

чисел

{k1, k2 ,, k p } , где ki M / mi m ;

i

1

- для набора структурных чисел вычисляются числа, обратные им {k11, k21,..., k

p } , где

ki1 определяется из условия: ki1 ki

1.

mi

- число восстанавливается по формуле (6).

Для каждого модуля m i значение ( ki1 M / mi ) всегда фиксировано, поэтому при

построении обратного преобразователя также могут использоваться таблицы состояний. Выбор

реализации таблиц состояний для интегрального исполнения также может быть гибким, т.е. таблицы

состояний могут быть реализованы как на основе памяти, так и на основе произвольной логики.

Реализация процедур модулярного сложения и умножения зависит от значения модуля, но

важно еще раз подчеркнуть, что разрядность модулярных сумматоров и умножителей в такой системе

будет значительно меньше разрядности исходных данных, и эти операции будут выполняться

параллельно и независимо друг от друга для каждого значения модуля. Интегральное исполнение

модулярных вычислительных процедур также позволяет гибко подходить к их реализации.

Традиционно выделяют следующие подходы к построению модулярных сумматоров [9]:

- прямая логическая реализация с использованием двоичных блоков;

- реализация на основе таблиц состояний;

- гибридный или смешанный метод реализации (использование таблиц состояний наряду с

двоичными блоками);

Первый из методов предполагает реализацию модулярного сумматора на основе двоичных

функциональных блоков (сумматоров, вычитателей, мультиплексоров и т.п.) и вызывает наибольший

интерес, поскольку оставляет за собой широкий выбор в реализации внутренней структуры такого

сумматора. В случае прямой логической реализации суммирование по модулю m i для двух

операндов a и b , находящихся в диапазоне {0,1, , mi 1} , выполняется по следующей формуле:

a b mi , если a b mi ;

a bm

i

если a b mi .

a b,

(7)

Данный подход является наиболее развивающимся в настоящее время, поскольку, во-первых,

позволяет в полной мере использовать богатый опыт проектирования двоичных устройств, а вовторых, предоставляет большую гибкость при реализации каждого компонента в составе всей

системы в зависимости от конкретных условий (значения модуля, требований по занимаемой

площади и быстродействию и т.д.) Так, например, для младших значений модулей возможны методы

построения с минимизацией их площади. Для старших значений модулей, которые определяют

быстродействие системы, возможно применение методов логического синтеза быстрых сумматоров

на основе BDD-технологии [10].

Применение второго подхода оправдано при наличии ячеек памяти и небольших значениях

модулей, а также когда некоторые из операндов являются константами. В этом случае часть

вычислений можно произвести заранее и уже полученные промежуточные результаты хранить в

таблицах, уменьшая тем самым аппаратные затраты.

Гибридный или смешанный метод реализации модулярных сумматоров представляет собой

комбинацию первых двух и использует как обычные двоичные блоки (в частности сумматоры), так и

таблицы состояний, обеспечивая компромисс между быстродействием и аппаратными затратами для

некоторых значений модулей.

Аппаратная реализация модулярного умножения также определяется конкретными

условиями и требованиями при проектировании того или иного устройства. Для небольших значений

модулей (до 7-8 бит) целесообразно применять реализацию на основе индексного или дискретно-

350

логарифмического представления операндов, которое позволяет заменить операцию умножения по

модулю m i операцией сложения по модулю ( mi 1) согласно формуле:

q j qk

g

mi

i j ik

mi 1

(8)

где q j и q k операнды (представлены в модулярном виде), g – первообразный корень. Недостатками

данного метода модулярного умножения является то, что он применим только для модулей,

являющихся простыми числами, а также наличие прямого и обратного индексного преобразования,

реализация которых требует дополнительных аппаратных затрат. Кроме того, существуют методы

построения быстродействующих схем умножителей. Так, например, для модулей вида ( 2 n 1) и

( 2 n 1) целесообразно применение алгоритма Бута при построении модулярных умножителей.

Для оценки эффективности использования аппарата модулярной арифметики была

разработана синтезируемая Verilog-модель специализированного вычислителя скалярных

произведений, реализующего формулу (3). При построении преобразователей использовались

конвейерные методы реализации. Проведено сравнение характеристик данного устройства с

аналогичным, функционирующим в двоичной системе счисления. Сравнительный анализ устройств

проводился в базисе 0.6 мкм библиотеки стандартных ячеек с использованием систем синтеза

Synopsys. Как показывают результаты синтеза вычислитель, реализованный с применением аппарата

модулярной арифметики обладает более высоким быстродействием по сравнению с традиционным

вычислителем в двоичной системе счисления (почти в 2 раза для 30-битного динамического

диапазона).

В заключение обобщим основные результаты работы:

- аппарат модулярной арифметики в сочетании с обычной двоичной арифметикой может

быть использован при построении специализированных конвейерных вычислителей с целью

повышения производительности устройства в целом;

- для повышения быстродействия таких систем преобразователи целесообразно строить на

основе конвейерных методов реализации;

- интегральное исполнение устройств с применением аппарата модулярной арифметики

позволяет гибко подходить к реализации основных модулярных вычислительных процедур, применяя

специализированные методы уменьшения площади или увеличения быстродействия в зависимости от

требований, предъявляемых к ним.

ЛИТЕРАТУРА

Акушский И.Я., Юдицкий Д.И. Машинная арифметика в остаточных классах. – М.:Сов. радио,

1968. – 440 с.

2. Торгашев В.А. Система остаточных классов и надежность ЦВМ. - М.:Сов. радио, 1973. – 120 с.

3. Амербаев В.М. Теоретические основы машинной арифметики. – Алма-Ата: Наука, 1976. –324 с.

4. Стемпковский А.Л., Корнилов А.И., Семенов М.Ю. Особенности реализации устройств цифровой

обработки сигналов в интегральном исполнении с применением модулярной арифметики //

Информационные технологии. – 2004. - № 2. – С. 2-9.

5. Амербаев В.М., Стемпковский А.Л., Широ Г.Э. Быстродействующий согласованный фильтр,

построенный по модулярному принципу // Информационные технологии. – 2004. - № 9. – С. 5-12.

6. Семенов М.Ю., Калашников В.С., Ласточкин О.В. Применение аппарата модулярной арифметики

для построения фильтра с конечной импульсной характеристикой. // Изв. ВУЗов. Электроника. –

2005. - № 3. – С. 46-50.

7. Корнилов А.И., Семенов М.Ю., Калашников В.С. Методы аппаратной оптимизации сумматоров

для двух операндов в системе остаточных классов // Изв. ВУЗов. Электроника. – 2004. - №1. – С.

75-82.

8. Корнилов А.И., Семенов М.Ю., Ласточкин О.В. Принципы построения модулярных индексных

умножителей. // Изв. ВУЗов. Электроника. – 2004. - № 2. – С. 48-55.

9. Bayoumi M.A., Jullien G.A., Miller W.C. A VLSI Implementation of Residue Adders // IEEE Trans. on

Circuits and Systems. – 1987. – V. 34, № 3. – P. 284-288.

10. Корнилов А.И., Исаева Т.Ю., Семенов М.Ю. Методы логического синтеза сумматоров с

ускоренным переносом по модулю (2n-1) на основе BDD-технологии // Изв. ВУЗов. Электроника.

– 2004. - № 3. – С. 54-60.

1.

351