metodichka RGRx

advertisement

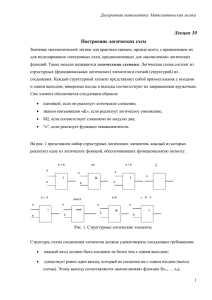

Федеральное казенное профессиональное образовательное учреждение Михайловский экономический колледж-интернат Министерства труда и социальной защиты РФ Отделение программирования в компьютерных системах Г.В. Марьина Методические рекомендации по выполнению расчетно-графической работы по дисциплине “Элементы математической логики” на тему “Синтез логических схем” для студентов второго курса специальности 09.02.03 Программирование в компьютерных системах (базовая подготовка) г. Михайлов, 2015 2 Марьина Г.В. Методические рекомендации по выполнению расчетно-графической работы по дисциплине «Элементы математической логики» на тему «Синтез логических схем» для студентов второго курса специальности 09.02.03 Программирование в компьютерных системах. Учебное пособие, Михайлов, МЭКИ, 2015. - 20 стр. Методические рекомендации содержат указания, варианты заданий и примеры выполнения расчетно-графической работы (РГР) по дисциплине «Элементы математической логики» на тему «Синтез логических схем» и предназначено для оказания практической помощи в выполнении РГР и оформления отчета по работе, а также формирования профессиональных компетенций у студентов 2 курса специальности 09.02.03 Программирование в компьютерных системах. Одобрено Цикловой комиссией циклов ЕН и профессионального цикла специальности «Программирование в компьютерных системах». Протокол №_________ от «____» _____________ 20 ____г. Председатель ______________ / ______________ Рецензент: Марьин И.А. преподаватель ФКПОУ МЭКИ © ФКПОУ «Михайловский экономический колледж-интернат», 2015 3 Содержание ОБЩИЕ ПОЛОЖЕНИЯ……………………………………….…………….….…..4 ПРАВИЛА ОФОРМЛЕНИЯ РАБОТЫ……………………………….……….…...4 ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ……………………….……………….…...5 ВАРИАНТЫ ЗАДАНИЙ…………………………………...………….….………...6 ПРИЛОЖЕНИЕ 1. Титульный лист отчета ……………..….………….….…. …..8 ПРИЛОЖЕНИЕ 2. Пример оформления отчета для ДНФ.………………..….…..9 ПРИЛОЖЕНИЕ 3. Пример оформления отчета для КНФ.………………..….…15 4 1. Общие положения 1. Расчетно-графическая работа (РГР) выполняется студентом во внеурочное время в течение недели, по окончании которого сдается на проверку. 2. Проверенная работа возвращается студенту с предварительной оценкой, которая выставляется по результатам проверки и подписью: “К защите” - если работа выполнена без ошибок; “К защите с доработкой” - если в работе были обнаружены незначительные ошибки (до защиты они должны быть исправлены); “Переделать” - если работа выполнена неверно. 3. После подготовки к защите, студент защищает работу в назначенный преподавателем день. На защите студент должен уметь пояснить, как он выполнял всю работу или указанный преподавателем пункт, ответить на вопросы преподавателя по теме «Синтез логических схем». 4. Оценка за работу ставится после ее защиты. 2. Правила оформления работы 1. Нельзя изменять порядок разделов РГР по своему усмотрению. 2. Текст РГР выполняется средствами редактора MS Word. Междустрочный интервал – 1,5 строки, шрифт – Times New Roman №14, выравнивание текста – по ширине. По всем сторонам листа следует оставлять поля следующих размеров: левое - 30 мм, правое - 10 мм, верхнее - 15 мм, нижнее 20 мм. Все листы отчета, кроме титульного, должны иметь сквозную нумерацию в правом верхнем углу страницы. Название раздела пишется заглавными буквами, подраздела – как обычное предложение. Точки в конце заголовков не ставятся, переносы в заголовках не допускаются. Каждый раздел должен начинаться с новой страницы. Таблицы нумеруются в пределах раздела. Надпись "Таблица" с указанием ее номера и названия помещают над шапкой таблицы. Все таблицы в отчете должны иметь одинаковый макет. 3. Схемы должны быть выполнены в MS Visio. В схемах должна прослеживаться структура (ряды элементов, линии, ведущие к элементам и от элементов должны быть одинаковой длины). Схемы обозначаются символом «Рис.» и нумеруются в пределах раздела отчета последовательно арабскими цифрами 5 и сопровождаются пояснительной информацией (каждая схема подписывается снизу). Номер рисунка состоит из номера раздела и порядкового номера схемы. 3. Порядок выполнения работы РГР должен включать в себя следующие разделы: 1. Титульный лист, на обороте которого указываются цель работы, номер варианта задания и исходные условия. 2. Раздел 1 – Минимизация функций. В данном разделе выполняются следующие этапы работы: С помощью карт Карно надо минимизировать функции F1 и F2 и получить минДНФ (для всех нечетных вариантов заданий) или минКНФ (для четных вариантов); Модифицировать полученные минимальные формы, если это необходимо, чтобы выявить одну или две общие импликанты. 3. Раздел 2 – Синтез логических схем в основном базисе. В данном разделе необходимо выполнить следующие этапы работы: Синтезировать 8-входовую схему на элементах основного базиса, предварительно рассчитав ее элементную базу; Синтезировать 4-входовую схему на элементах основного базиса. Рассчитать для этой схемы элементную базу и сделать выводы, сравнив ее с базой предыдущей схемы; Для 4-входовой схемы на элементах основного базиса определить теоретическим путем результат функций F1 и F2, который будет получен на выходах с учетом конкретного набора значений, поступающих на вход схемы (набор указан в варианте). Значения на выходах основных узлов схемы проставляются на самой схеме. 4. Раздел 3 - Синтез логических схем в базисе Шеффера (для ДНФ) или Вебба (для КНФ). В данном разделе необходимо выполнить следующие этапы работы: 6 Перевести минДНФ (минКНФ) из основного базиса в базис Шеффера (для ДНФ) или в базис Вебба (для КНФ). Синтезировать 4входовую схему, реализующую функции F1 и F2 в базисе Шеффера для ДНФ (Вебба для КНФ); Синтезировать 4-входовую схему, используя только 2-входовые элементы И-НЕ (ИЛИ-НЕ) - в зависимости от варианта, предварительно рассчитав для нее элементную базу. !!! Следует заметить, что последняя схема избыточна, т.е. содержит лишние элементы, которые можно убрать, при этом на ее работе это никак не скажется. Что это за лишние элементы – вопрос, на который должен знать ответ студент на защите своей РГР. Также при синтезе последней схемы студент должен учитывать, что одинаковые сочетания переменных, например, АС, нужно синтезировать один раз, а сигнал с выхода этого конъюнктора использовать столько раз, сколько это необходимо, т.е. «распараллелить» его. Также следует поступить с инверсиями, если они повторяются в нескольких импликантах, например, А используется в трех импликантах. Тогда инвертор по переменной А в схеме надо использовать один, а сигнал с его выхода распараллелить на три. В противном случае схемы будут избыточны, что скажется на итоговой оценке за работу. 4. Варианты заданий Значения входных переменных № 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 A 1 1 0 1 1 1 0 0 1 0 0 0 1 0 0 B 1 0 0 0 0 1 0 0 0 1 1 1 1 0 1 C 0 0 1 1 1 1 0 1 0 0 1 0 1 1 1 D 1 1 1 0 1 1 1 0 0 1 0 0 0 1 1 № 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 A 1 1 0 1 1 0 0 1 1 0 0 0 1 0 B 0 0 1 0 0 1 0 1 1 0 0 1 1 1 C 1 1 1 0 0 0 0 1 0 1 1 0 0 1 D 1 0 0 1 0 0 1 1 1 0 1 1 0 0 7 № 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Функции F1 = (0, 1, 2, 4, 5, 12, 13) F2 = (0, 1, 2, 6, 10, 14) F1 = (5, 7, 9, 11, 12, 14, 15) F2 = (5, 6, 7, 2, 10, 12, 14) F1 = (0, 2, 4, 6, 12, 13, 14) F2 = (1, 5, 9, 12, 13, 14) F1 = (2, 3, 10, 11, 13, 14, 15) F2 = (0, 4, 8, 11, 12, 13, 15) F1 = (2, 6, 10, 8, 11, 12, 14) F2 = (0, 1, 6, 8, 9, 10, 11, 14) F1 = (1, 5, 9, 12, 13, 14) F2 = (0, 2, 4, 6, 12, 13, 14) F1 = (2, 3, 10, 11, 13, 14, 15) F2 = (0, 4, 8, 11, 12, 13, 15) F1 = (0, 1, 6, 8, 9, 10, 11, 14) F2 = (2, 6, 8, 10, 11, 12, 14) F1 = (0, 1, 9, 10, 11, 15) F2 = (0, 1, 3, 5, 9, 11) F1 = (2, 6, 8, 9, 10, 14) F2 = (4, 5, 8, 9, 10, 12, 13) F1 = (1, 3, 5, 7, 9, 10, 11) F2 = (0, 3, 4, 8, 10, 11, 12) F1 = (0, 1, 2, 3, 4, 6, 9, 13) F2 = (0, 1, 3, 5, 8, 9, 13) F1 = (4, 5, 8, 9, 10, 12, 13) F2 = (2, 6, 8, 9, 10, 14) F1 = (0, 1, 3, 5, 9, 11) F2 = (0, 1, 9, 10, 11, 15) F1 = (1, 2, 3, 4, 6, 11) F2 = (2, 3, 4, 6, 7, 14) № 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 Функции F1 = (0, 2, 4, 5, 6, 7, 15) F2 = (0, 2, 3, 4, 6, 7, 15) F1 = (0, 1, 3, 5, 8, 9, 13) F2 = (0, 1, 2, 3, 4, 6, 9, 13) F1 = (0, 3, 4, 8, 10, 11, 12) F2 = (1, 3, 5, 7, 9, 10, 11) F1 = (2, 3, 9, 11, 14, 15) F2 = (0, 1, 8, 9, 11, 14, 15) F1 = (0, 2, 3, 4, 6, 9, 11) F2 = (0, 2, 3, 5, 7, 9, 11) F1 = (0, 1, 2, 3, 4, 6, 7, 15) F2 = (0, 2, 4, 5, 6, 7, 15) F1 = (1, 2, 3, 4, 6, 11) F2 = (2, 3, 4, 6, 7, 14) F1 = (2, 5, 6, 7, 12, 14) F2 = (5, 7, 9, 11, 12, 14, 15) F1 = (0, 1, 2, 6, 10, 14) F2 = (0, 1, 2, 4, 5, 12, 13) F1 = (0, 2, 3, 5, 7, 9, 11) F2 = (0, 2, 3, 4, 6, 9, 11) F1 = (0, 1, 8, 9, 11, 14, 15) F2 = (2, 3, 9, 11, 14, 15) F1 = (1, 5, 7, 8, 12) F2 = (0, 4, 5, 7, 8, 12, 13) F1 = (2, 4, 6, 10, 12, 13) F2 = (0, 2, 4, 6, 7, 10) F1 = (0, 1, 4, 6, 9, 13) F2 = (0, 1, 4, 5, 6, 8, 9) 8 Приложение 1 Титульный лист отчета ФКПОУ «МЭКИ» Минтруда России Отделение программирования в компьютерных системах Расчетно-графическая работа по дисциплине: “Элементы математической логики” на тему: “Синтез логических схем” Оценка: Выполнил: студент гр. 22-п Иванов И.И. Принял: преподаватель Марьина Г.В. г. Михайлов, 2015 9 Приложение 2 Пример оформления отчета для ДНФ Оборот титульного листа Цель работы: Изучение основ синтеза логических схем комбинационного цифрового устройства с двумя выходами с учетом минимизации булевых функций устройства. Задание: Вариант № 30. F1 (1, 3, 8, 9, 12, 13, 15) Даны функции: F2 (1, 3, 4, 6, 12, 13, 14, 15) Набор значений на A=1 входах устройства B=1 C=0 D=0 1. МИНИМИЗАЦИЯ ФУНКЦИЙ Найдем минДНФ для функций F1 и F2, используя карты Карно. 1.1. В В 1 1 1 В В 1 C А 1 1 C А 1 1 1 C C 1 А 1 1 1 1 А 1 D D F1 C D D D F2 C D 10 для F1 AC ABD ABD минДНФ для F2 B D AB ABD В результате имеем одну общую импликанту - A BD . 1.2. Модифицируем минДНФ для функции F2, чтобы выявить дополнительные общие импликанты. В В 1 1 1 1 C А 1 D минДНФ F 2 = B D ABD ABD C минДНФ F1 AC ABD ABD 1 А 1 C 1 D D F 2 В итоге имеем две общие импликанты для функций F 1 и F 2 - ABD и A BD . Вывод: для реализации импликант минДНФ для F1 и F2 потребуется 5 элементов, а для реализации импликант для F1 и F2’ потребуется всего 4 элемента, т.е. синтезируемые схемы будут более компактными. 11 2. СИНТЕЗ ЛОГИЧЕСКИХ СХЕМ В ОСНОВНОМ БАЗИСЕ Синтезируем 8-входовую схему на элементах основного базиса (рис. 2.1). 2.1. Рассчитаем элементную базу для реализации данной схемы (таблица 2.1). Таблица 2.1. Элементная база 8-входовой схемы в основном базисе Элемент Количество Импликанты 2-входовой конъюнктор 2 B D , AC 3-входовой конъюнктор 2 ABD , A BD 3-входовой дизъюнктор 2 Для получения F1 и F2’ Итого 6 A B C — D A — B — — C D & _ AC & 1 ABD & __ ABD F1 1 F2' & _ BD Рис. 2.1. 8-входовая схема в основном базисе 2.2. Для реализации 4-входовой схемы на элементах основного базиса потребуются 4 инвертора и все элементы из 8-входовой схемы (рис. 2.2). 12 2.3. Определим теоретическим путем - какие значения будут получены на выходах схемы F1 и F2’ при значениях входных переменных A=1, B=1, C=0, D=0. _ __ _ F1 = AC ABD ABD = 10 110 000 = 1 0 0 = 1 _ __ _ F2’ = BD ABD ABD = 10 110 000 = 1 0 0 = 1 Значения на выходах элементов показаны на рисунке 2.2. A B C D 1 0 _ С _ AC & 1 1 1 1 1 1 0 & 0 0 0 & 1 1 & ABD 0 1 0 0 1 0 0 1 1 1 F1 1 F2' _ A 0 1 _ B 0 0 _ D __ ABD 0 _ BD 1 1 Рис. 2.2. 4-входовая схема в основном базисе Рассматривая элементный состав этих двух схем, можно сделать вывод о том, что при уменьшении числа входных сигналов увеличивается количество элементов за счет добавления инверторов. 13 3. СИНТЕЗ ЛОГИЧЕСКИХ СХЕМ В БАЗИСЕ ШЕФФЕРА Переведем функции F1 и F2 в базис Шеффера _ __ _ _ _ F1 = AC ABD ABD = (A C) (A B D) (A B D) _ __ _ _ _ F2’ = BD ABD ABD = (B D) (A B D) (A B D) 3.1. Синтезируем 4-входовую схему, реализующую функции F1 и F2’ в базисе Шеффера. Расчет элементной базы приведен в таблице 3.1. Схема представлена на рисунке 3.1. Таблица 3.1. Элементная база 4-входовой схемы в базисе Шеффера Элемент Количество Импликанты 3.2. 2-входовой элемент И-НЕ 6 3-входовой элемент И-НЕ 4 Итого 10 A, B, C , D, B | D, A | C A | B | D, A | B | D, F1, F 2 Синтезируем 4-входовую схему на 2-входовых элементах И-НЕ, в которой инвертор заменяется одним элементом, конъюнктор - двумя элементами, а дизъюнктор - тремя элементами И-НЕ. Поскольку у всех элементов только по два входа, то нельзя сразу получить импликанту третьего ранга, например, ABD. Она будет синтезироваться поэтапно, т.е. сначала будет получена конъюнкция AB, а потом она умножится на D. Аналогичный поэтапный синтез будет применен для импликанты A BD и для дизъюнкции импликант при получении F1 и F2’. Схема представлена на рисунке 3.2. 14 A D B C & _ A|C & A|B|D & __ A|B|D & _ B|D _ С & _ A & _ B & & _ D & F1 & F2' Рис. 3.1. 4-входовая схема в базисе Шеффера A BC D & & & _ AC & & AВ & & _ C & & AВD F1 & __ AВDvABD & & _ A & & & __ AВ & & __ AВD & & & _ В & & & & _ ВD F2' & _ D Рис. 3.2. 4-входовая схема в базисе Шеффера на 2-входовых элементах И-НЕ 15 Приложение 3 Пример оформления отчета для КНФ Оборот титульного листа Цель работы: Изучение основ синтеза логических схем комбинационного цифрового устройства с двумя выходами с учетом минимизации булевых функций устройства. Задание: Вариант № 31. Даны функции: F1 (1, 3, 8, 9, 12, 13, 15) F2 (1, 3, 4, 6, 12, 13, 14, 15) Набор значений на A=1 входах устройства B=1 C=0 D=0 1. МИНИМИЗАЦИЯ ФУНКЦИЙ Найдем минКНФ для функций F1 и F2, используя карты Карно. 1.1. В В 0 0 0 В В 0 0 C А 0 C А 0 0 0 C C 0 А 0 0 0 0 А 0 D D F1 C D D D F2 C D 16 для F1 AC ABD ABD ( A C )( A B D)( A B D) минКНФ для F2 B D AB ABD ( B D)( A B)( A B D) В результате имеем одну общую импликанту - ( A B D) . 1.2. Модифицируем минКНФ для функции F2, чтобы выявить дополнительные общие импликанты. В В 0 0 0 0 C А C 0 0 А C 0 D 0 D D F 2 МинКНФ для F1 = AC ABD ABD ( A C )( A B D)( A B D) минКНФ F 2 = B D ABD ABD ( B D)( A B D)( A B D) В итоге имеем две общие импликанты для функций F 1 и F 2 ( A B D) и ( A B D) Вывод: для реализации импликант минКНФ для F1 и F2 потребуется 5 элементов, а для реализации импликант для F1 и F2’ потребуется всего 4 элемента, т.е. синтезируемые схемы будут более компактными. 17 2. СИНТЕЗ ЛОГИЧЕСКИХ СХЕМ В ОСНОВНОМ БАЗИСЕ 2.1.Синтезируем 8-входовую схему на элементах основного базиса (рис. 2.1). Рассчитаем элементную базу для реализации данной схемы (таблица 2.1). Таблица 2.1. Элементная база 8-входовой схемы в основном базисе Элемент Количество Импликанты 2-входовой дизъюнктор 2 ( A C ) , ( B D) 3-входовой дизъюнктор 2 ( A B D), ( A B D) 3-входовой конъюнктор Итого 2 6 A B C — D A — B Для получения F1 и F2’ — — C D 1 _ AvC 1 & _ _ _ AvBvD 1 _ AvBvD F1 & F2' 1 _ BvD Рис. 2.1. 8-входовая схема в основном базисе 2.2. Для реализации 4-входовой схемы на элементах основного базиса потребуются 3 инвертора для A, B, D и все элементы из 8-входовой схемы. Сигналы с выхода каждого инвертора будут использоваться каждый по два раза. Схема представлена на рисунке 2.2. 18 2.3. Определим теоретическим путем - какие значения будут получены на выходах схемы F1 и F2’ при значениях входных переменных A=1, B=1, C=0, D=0. _ _ _ _ _ _ _ _ _ _ F1 = (A C)(A B D)(A B D) = (1 0)(1 1 0)(1 1 0) = =011=0 _ _ _ _ _ _ _ _ _ _ F2’ = (B D)(A B D)(A B D) = (1 0)(1 1 0)(1 1 0) = =011=0 Значения на выходах элементов показаны на рисунке 2.2. A B C D 0 1 _ A _ AvC 1 0 0 0 0 _ D 1 1 0 1 1 1 _ _ _ AvBvD 0 _ B 0 1 1 1 1 _ AvBvD 0 & 0 1 F1 1 1 1 & 0 F2' 0 0 1 0 0 _ BvD Рис. 2.2. 4-входовая схема в основном базисе Рассматривая элементный состав этих двух схем, можно сделать вывод о том, что при уменьшении числа входных сигналов увеличивается количество элементов за счет добавления инверторов. 19 3. СИНТЕЗ ЛОГИЧЕСКИХ СХЕМ В БАЗИСЕ ВЕББА Переведем функции F1 и F2’ в базис Вебба F1 = ( A C )( A B D)( A B D) ( A C ) ( A B D) ( A B D) F2’ = ( B D)( A B D)( A B D) ( B D) ( A B D) ( A B D) 3.1. Синтезируем 4-входовую схему, реализующую функции F1 и F2’ в базисе Вебба. Расчет элементной базы приведен в таблице 3.1. Схема представлена на рисунке 3.1. Таблица 3.1. Элементная база 4-входовой схемы в базисе Вебба Элемент Количество Импликанты 2-входовой элемент ИЛИ-НЕ 5 3-входовой элемент ИЛИ-НЕ Итого 4 9 A, B, D, В D, A C ( A B D), ( A B D), F1, F 2 3.2. Синтезируем 4-входовую схему на 2-входовых элементах ИЛИ-НЕ, в которой инвертор заменяется одним элементом, дизъюнктор - двумя элементами, а конъюнктор - тремя элементами ИЛИ-НЕ. Поскольку у всех элементов только по два входа, то нельзя сразу получить импликанту третьего ранга, например, (A B D ). Она будет синтезироваться поэтапно, т.е. сначала будет получена конъюнкция A B, а потом вторым дизъюнктором она сложится с D . Аналогичный поэтапный синтез будет применен для импликанты ( A B D) и для конъюнкции импликант при получении F1 и F2’. Схема представлена на рисунке 3.2. 20 A B D C 1 _ A 1 _ D 1 _ A↓C 1 _ _ _ A↓B↓D 1 F1 1 _ B 1 _ A↓B↓D 1 F2' 1 _ B↓D Рис. 3.1. 4-входовая схема в базисе Вебба A BC D 1 1 1 _ А _ D 1 1 1 _ AvC 1 _ _ AvD 1 1 _ _ _ AvBvD 1 1 _ B 1 1 1 1 _ AvD 1 1 _ BvD 1 F1 1 F2' 1 _ AvBvD 1 1 1 1 Рис. 3.2. 4-входовая схема в базисе Вебба на 2-входовых элементах ИЛИ-НЕ