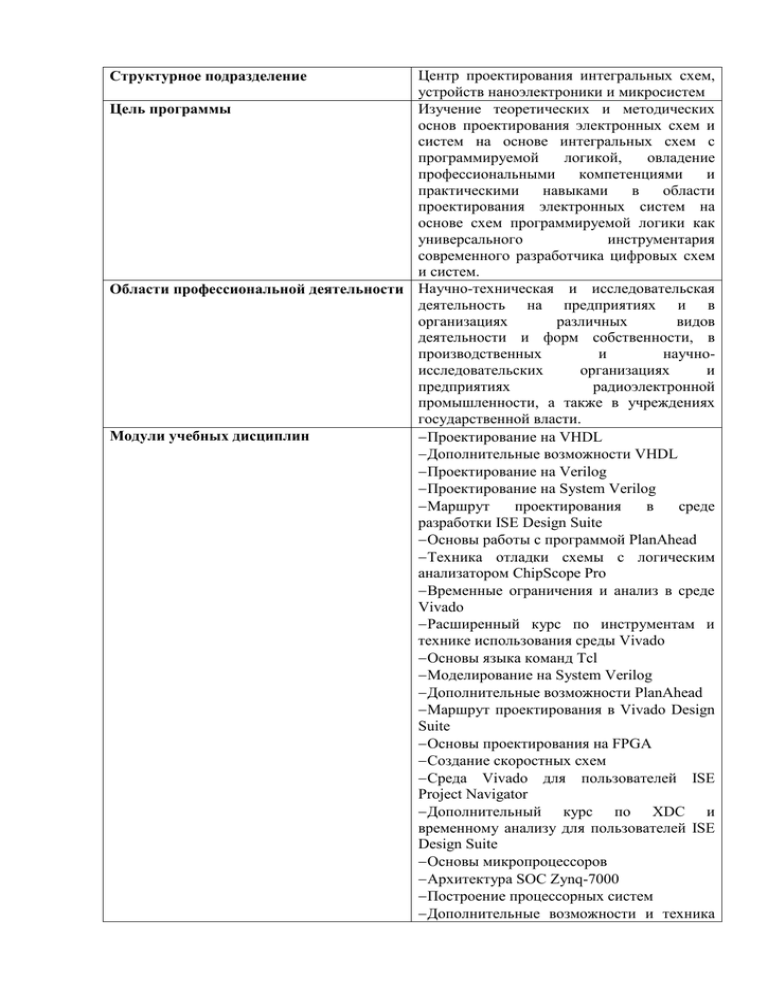

Структурное подразделение Центр проектирования интегральных схем,

advertisement

Центр проектирования интегральных схем, устройств наноэлектроники и микросистем Изучение теоретических и методических Цель программы основ проектирования электронных схем и систем на основе интегральных схем с программируемой логикой, овладение профессиональными компетенциями и практическими навыками в области проектирования электронных систем на основе схем программируемой логики как универсального инструментария современного разработчика цифровых схем и систем. Области профессиональной деятельности Научно-техническая и исследовательская деятельность на предприятиях и в организациях различных видов деятельности и форм собственности, в производственных и научноисследовательских организациях и предприятиях радиоэлектронной промышленности, а также в учреждениях государственной власти. Модули учебных дисциплин Проектирование на VHDL Дополнительные возможности VHDL Проектирование на Verilog Проектирование на System Verilog Маршрут проектирования в среде разработки ISE Design Suite Основы работы с программой PlanAhead Техника отладки схемы с логическим анализатором ChipScope Pro Временные ограничения и анализ в среде Vivado Расширенный курс по инструментам и технике использования среды Vivado Основы языка команд Tcl Моделирование на System Verilog Дополнительные возможности PlanAhead Маршрут проектирования в Vivado Design Suite Основы проектирования на FPGA Создание скоростных схем Среда Vivado для пользователей ISE Project Navigator Дополнительный курс по XDC и временному анализу для пользователей ISE Design Suite Основы микропроцессоров Архитектура SOC Zynq-7000 Построение процессорных систем Дополнительные возможности и техника Структурное подразделение Срок обучения часов (месяцев) проектирования встроенных процессорных систем Программирование на языке С в SDK Разработка ПО для процессорной системы Дополнительные возможности и техника разработки ПО для процессорной системы Проектирование на 6-м семействе FPGA Оптимизация FPGA по энергопотреблению 400 академических часов Компетенции, подлежащие формированию по итогам обучения (образовательные результаты по программе) Профессиональные компетенции (ПК) (образовательный результат) Знать: синтаксис VHDL, типы данных циклы и условия , функции и процедуры, атрибуты, пакеты и библиотеки в VHDL, основы синтеза Testbench, основные приемы работы с симулятором ISIM, организация памяти в ПЛИС, основные положения теории конечных автоматов, структуру кристаллов FPGA. Уметь: описывать типы данных, выполнять параллельные операции, описывать процессы и переменные, работать с Testbench, симулятором ISIM, создавать память, использовать кристаллы FPGA, описывать циклы и условия, функции и процедуры, работать с атрибутами, пакетами и библиотеками. Знать: концепции моделирования, способы задания дополнительных типов данных, подпрограмм и атрибутов проекта, указателей и блоков, основные приемы работы с файлами, и применения VHDL для синтеза, способы поддержки нескольких платформ, приемы работы с нецелыми числами. Уметь: создавать подпрограммы и атрибуты проекта, описывать указатели и блоки, работать с файлами, использовать VHDL для синтеза цифровых схем, осуществлять поддержку нескольких платформ, работать с нецелыми числами. Знать: способы моделирования аппаратуры, основные операции процесса моделирования концепции языка Verilog, способы определения модулей и портов в проекте, основные приемы создания TestBench и дополнительные возможности Профессиональный модуль Модуль 1. Проектирование на VHDL Модуль 2. Дополнительные возможности VHDL Модуль 3. Проектирование на Verilog синтеза TestBench, синтаксис операторов и выражений, процедурных блоков, операций ветвления, функций и задач, дополнительные концепции языка Verilog, основы теории конечных автоматов, методику работы с FPGA Xilinx. Уметь: описывать модули и порты, использовать TestBench, осуществлять процесс моделирования, описывать процедурные блоки, использовать операции ветвления, дополнительные концепции языка Verilog, описывать конечные автоматы, использовать Xilinx FPGA для проектирования цифровых схем, дополнительные возможности написания TestBench. Знать: основные конструкции SystemVerilog, типы данных, структуры, союзы и массивы, дополнительные операторы в System Verilog, процедурные состояния и способы управления потоком, функции, задачи и пакеты, интерфейсы, методику оптимального использования ресурсов FPGA. Уметь: описывать типы данных, процедурные состояния, управлять потоком, описывать интерфейсы. Знать: как планировать проект, основные приемы и способы создания проекта в Project Navigator, синтеза HDL и методику применения синтезатора XST, методы задания ограничений пользователя и распределения контактов ввода/вывода, приемы работы с симулятором ISim и использования расширенных возможностей ISim. Уметь: создавать проекты в Project Navigator, осуществлять синтез HDL, использовать синтезатор XST, устанавливать ограничения и распределение контактов ввода/вывода, работать с симулятором ISim. Знать: основные приемы работы с программой PlanAhead и преимущества ее использования, методику работы с менеджером проектов, способы задания распределения контактов ввода/вывода и ресурсов тактовых частот, приемы интеграции c программой CORE Generator и с Project Navigator. Уметь: работать с менеджером проектов, распределять контакты ввода/вывода и Модуль 4. Проектирование на System Verilog Модуль 5. Маршрут проектирования в ISE Design Suite Модуль 6. Основы работы с PlanAhead ресурсы тактовых частот, осуществлять интеграцию с программой CORE Generator, выполнять анализ временных параметров. Знать: как работает ChipScope Pro, как осуществлять интеграцию модулей ChipScope Pro в схему с помощью Core Inserter, интеграцию модулей ChipScope Pro в схему с помощью CORE Generator, способы стробирования и сохранения данных ChipScope, знать основные приемы работы с Pro Analyzer: отображение данных, советы и трюки, анализировать примеры применения, как реализовать удаленный доступ. Уметь: интегрировать модули ChipScope Pro в схему с помощью Core Inserter и CORE Generator, выполнять стробирование и сохранение данных, использовать советы и трюки, выполнять анализ параметров, устанавливать удаленный доступ. Знать: основы проектирования на FPGA, методологию проектирования, технику проектирования на FPGA, как осуществить доступ к базе данных проекта, задание тактовых сигналов и основы статического временного анализа; способы статического временного анализа и задания тактовых сигналов, как задавать исключения из временных ограничений, технику синтеза, примеры использования карт проверки методологии проектирования; методологию проектирования FPGA, технику кодирования HDL, методологию сброса, типовые схемы синхронизации и содержание отчетов по взаимодействию тактовых сигналов, как достигать временные параметры, как анализировать ситуации в рамках методологии проектирования и основные данные быстродействия. Уметь: осуществлять доступ к базе данных проекта, выполнять статический временной анализ, описывать тактовые сигналы, задавать исключения из временных ограничений, осуществлять сброс схемы. Знать: временные ограничения и способы анализа схем в среде Vivado, приемы работы с временными ограничениями, методологию проектирования, методы проведения дополнительного временного анализа, примеры, демонстрирующие Модуль 7. Техника отладки схемы с ChipScope Pro Модуль 8. Временные ограничения и анализ в среде Vivado Модуль 9. Расширенный курс по инструментам и технике использования среды Vivado временные отчеты; методы задания временных ограничений сигналов ввода/вывода при системной синхронизации и синхронизации от источника сигнала, инструменты Pblocks, приемы и технику планирования размещения, и задания иерархических проектов, основы работы с инструментами проектирования Project- Based и Non-Project Batch, как написать скрипты в маршрутах проектирования Project-Based и Non-Project Batch. Уметь: анализировать временные ограничения сигналов ввода/вывода при системной синхронизации, планировать размещения, создавать скрипты при ProjectBased и Non-Project Batch маршрутах проектирования. Знать: синтаксис Tcl: основы синтаксиса и структуры, типы данных, переменные и выражения, условия и циклы, списки, стандартные выражения на Tcl, как использовать Tcl в среде Vivado, способы описания структур данных в Tcl, процедур и пакетов. Уметь: использовать Tcl в среде Vivado, описывать условия и циклы, структуру данных в Tcl, применять стандартные выражения на Tcl. Знать: основы применения System Verilog для моделирования, типы данных, задачи и функции, блоки System Verilog для моделирования, что такое полнота тестирования, что такое объектноориентированные моделирование, рандомизация, принципы применения операторов контроля. Уметь: описывать задачи и функции, блоки System Verilog для моделирования, осуществлять объектно-ориентированное моделирование, рандомизацию, использовать операторы контроля, осуществлять полное тестирование. Знать: инструменты и утилиты программы PlanAhead, методику разработки и анализ RTL-описания, методы анализа распределения аппаратных ресурсов, методы анализа PBlock, основы техники распределения проекта, метод сохранения проекта с помощью утилиты Partition, последовательность отладки проектов с программой ChipScope Pro, основы Модуль 10. Основы языка команд Tcl Модуль 11. Моделирование на System Verilog Модуль 12. Дополнительные возможности PlanAhead описания проектов скриптами Tcl. Уметь: работать с программой PlanAhead, выполнять разработку и анализ RTL, распределять аппаратные ресурсы проекта, сохранять проект с помощью Partition, выполнять отладку с программой ChipScope Pro, синтезировать проект с помощью Tcl скриптов. Знать: ключевые моменты методологии проектирования, основы планирования проекта, основные приемы работы в среде проектирования Vivado, приемы разработки маршрута проектирования в среде Vivado, ограничения, накладываемые на тактовые сигналы, технику распределения контактов ввода/вывода, последовательность работы с симулятором Vivado. Уметь: работать в среде проектирования Vivado, составлять маршрут проектирования в среде Vivado, устанавливать ограничения на тактовые сигналы и распределять контакты ввода/вывода, использовать симулятор Vivado. Знать: методологию проектирования, основы архитектуры FPGA, инструменты и утилиты среды проектирования Vivado Design Suite, основы разработки маршрута проектирования, способы визуализации для анализа проекта, основы проектирования с IP, базовые временные ограничения и отчеты, способы оптимизации использования ресурсов FPGA: тактовые ресурсы, базовые временные ограничения (XDC), временные отчеты, основные приемы синхронного проектирования, конфигурацию FPGA. Уметь: использовать маршрут проектирования, устанавливать базовые временные ограничения и отчеты, использовать ресурсы FPGA, распределять тактовые ресурсы, задавать временные отчеты. Знать: основы проектирования FPGA, приемы проектирования с использованием аппаратного модуля Digital Clock Manager, методику проектирования на FPGA, типовые приемы работы с программой CORE Generator System, методы реализации временных параметров, временные группы и ограничения OFFSET (на входные и выходные сигналы), Модуль 13. Маршрут проектирования в Vivado Design Suite Модуль 14. Основы проектирования на FPGA (Essentials of FPGA Design) Модуль 15. Создание скоростных схем временные ограничения на распространение сигналов, дополнительные опции реализации проекта, методы оценки потребляемой мощности. Уметь: проектировать с использованием аппаратного модуля Digital Clock Manager, применять методику проектирования на FPGA, использовать программу CORE Generator System, обеспечивать и устанавливать временные ограничения на распространение сигналов, использовать дополнительные опции реализации проекта, выполнять оценку потребляемой мощности. Знать: методики проектирования, Модуль 16. Среда Vivado для пользователей особенности и преимущества среды ISE Project Navigator проектирования Vivado, среду Vivado, основы работы с менеджером проектов и библиотекой IP-блоков, инструменты среды, методологию синтеза и способы формирования отчетов, методы имплементации и статического временного анализа. Уметь: использовать инструменты среды Vivado, выполнять имплементацию и статический временной анализ. Знать: основы методологии Модуль 17. Дополнительный курс по XDC проектирования в среде Vivado, методы и временному анализу для пользователей использования базы данных проекта, ISE Design Suite основы статического временного анализа и распределения тактовых ресурсов, методы определения входов и выходов, исключений, дополнительного временного анализа, дополнительные ограничения интерфейсов ввода/вывода, типовые маршруты проектирования, скрипты, основы и особенности методологии проектирования высокоскоростных схем, методологию проектирования FPGA, технику кодирования на HDL, методы организации сброса, цепей синхронизации и отчетов о взаимодействии тактовых доменов, способы оптимизации временных параметров. Уметь: работать с базой данных проекта, выполнять статический временной анализ и использовать тактовые ресурсы, проектировать входы и выходы, работать с исключениями, устанавливать дополнительные ограничения интерфейсов ввода/вывода, разрабатывать скрипты, кодировать на HDL, использовать методологию сброса, обеспечивать оптимальные временные параметры проекта. Знать: ключевые компоненты процессора; принцип обработки прерывания в процессоре; некоторые особенности современных процессоров; сравнение некоторых существующих архитектур процессоров. Уметь: написать простую программу на языке ассемблер; написать программу управляемою через прерывания. Знать: основные компоненты, входящие в состав системы на кристалле Zynq; основные преимущества выполнения функция в программном обеспечении и в программируемой логики. Уметь: спроектировать аппаратную платформу для СнК Zynq; выбрать наиболее оптимальный интерфейс для связи программируемой логики и процессорной системы; использовать DMA контроллер; произвести аппаратную и программную отладку СнК Zynq; запустить и отладить приложение для операционной системы Linux на СнК Zynq. Знать: программные инструменты Xilinx необходимые для проектирования встраиваемых систем; Уметь: спроектировать встраиваемую систему на основе Micro blaze или CortexA9 при помощи инструмента Vivado IP Integrator и мастера настройки; написать программу, используя средства разработки программного обеспечения на основе Eclipse; создать и внедрить процессорную систему средствами Vivado Design Suite; спроектировать и добавить собственный периферийный модуль, использующий AXI интерфейс; произвести симуляцию собственного модуля используя функциональную модель шины. Знать: процесс загрузки процессорной системы и программируемой логики, схемы ускорения процесса загрузки; особенности использования различных типов памяти. Уметь: применить передовые методы отладки, в том числе использовать анализатор Vivado для отладки процессорной системы; добавить в процессорную систему дополнительные контроллеры памяти; внедрить контроллер прерываний в процессорную систему; Модуль 18. Основы микропроцессоров Модуль 19. Архитектура SOC Zynq-7000 Модуль 20. Построение процессорных систем Модуль 21. Дополнительные возможности и техника проектирования встроенных процессорных систем спроектировать систему использующую flash-память, осуществить загрузку системы из выбранного типа памяти. Знать: синтаксис языка программирования Модуль 22. Программирование на языке С в С; особенности применения функций и SDK макросов; эффективное применение типов переменных. Уметь: спроектировать эффективную программу на языке С для встраиваемых систем; произвести отладку программного обеспечения при помощи GNU отладчика. Знать: типовую архитектуру процессоров, Модуль 23. Разработка ПО для их периферию и инструменты, основы процессорной системы работы с платформой разработки программного обеспечения (ПО), особенности разработки приложений под Linux, ПО для работы в среде SDK, основы программирования в автономной среде, основы программирования в среде Linux, способы управления адресным пространством, обработки прерываний, технику загрузки ПО и отладки приложений, методологию анализа ПО, основы разработки драйверов для собственного устройства, дополнительные сервисы и операционные системы, методы управления энергопотреблением в среде проектирования Xilinx. Уметь: работать на платформе разработки программного обеспечения (ПО), программировать в среде Linux, работать с прерываниями, выполнять отладку приложения, анализ ПО, написать драйвер для собственного устройства, работать с дополнительными службами и операционными системами. Знать: дополнительные возможности Модуль 24. Дополнительные возможности программного загрузчика Zynq, типовые и техника разработки ПО для процессорной операции загрузки Zynq, дополнительные системы возможности процессора Cortex-A9, расширенную конфигурацию DMA в Zynq, способы конфигурирования высокоскоростной и низкоскоростной периферий в Zynq. Уметь: учитывая детали, выполнять загрузку Zynq, устанавливать расширенную конфигурацию DMA в Zynq, работать с низкоскоростной периферией в Zynq. Знать: номенклатуру и особенности 6-го Модуль 25. Проектирование на 6-м семейства FPGA, архитектуру КЛБ, технику семействе FPGA описания проекта на HDL, ресурсы КЛБ, ресурсы памяти, ресурсы ЦОС, основы ресурсов ввода/вывода, ресурсы ввода/вывода 6-го семейства, основы тактовых ресурсов, тактовые ресурсы 6-го семейства, контроллеры памяти, дополнительные аппаратные ресурсы. Уметь: работать с 6-м семейством FPGA, выполнять описание аппаратуры на HDL, работать с ресурсами КЛБ, ресурсами памяти, ресурсами ЦОС, ресурсами ввода/вывода, ресурсами ввода/вывода 6-го семейства, тактовыми ресурсами, тактовыми ресурсами 6-го семейства, контроллерами памяти, дополнительными аппаратными ресурсами. Знать: требования по питанию FPGA, инструменты программы оценки энергопотребления Xilinx Power Estimator (XPE), методы оценки энергопотребления в XPE, возможности анализатора энергопотребления Xilinx Power Analyzer (XPA), методы оценки энергопотребления в XPA, оценки динамического энергопотребления, программные опции управления энергопотреблением, технику управления энергопотреблением, способы оптимизации энергопотребления ресурсов ввода/вывода, особенности управления энергопотреблением в 7-м семействе FPGA. Уметь: выполнять требования по питанию FPGA, работать с программой оценки энергопотребления Xilinx Power, выполнять оценку энергопотребления в XPE, работать с анализатором энергопотребления Xilinx Power Analyzer (XPA), выполнять оценку энергопотребления в XPA и оценку динамического энергопотребления, устанавливать программные опции управления энергопотреблением, управлять энергопотреблением, выполнять оптимизацию энергопотребления ресурсов ввода/вывода, управлять энергопотреблением в 7-м семействе FPGA, учитывая особенности 7-го семейства FPGA, решать типовые оптимизации энергопотребления. Модуль 26. Оптимизация FPGA по энергопотреблению Пояснительная записка Интегральные схемы с программируемой пользователем структурой (другое название программируемые логические интегральные схемы, т.е. ПЛИС), ознаменовали появление нового перспективного направления в развитии элементной базы электронного приборостроения. Именно эти СБИС открывают возможности использования микросхем высокого уровня интеграции не только в массовых изделиях, выпускаемых тиражами в сотни тысяч экземпляров, но и в проектах практически любой тиражности. В ПЛИС задание схеме определенной внутренней структуры (конфигурирование схемы) выполняется потребителем, изготовитель в этом процессе не участвует и поставляет на рынок продукцию, пригодную для многих покупателей, создающих аппаратуру разного назначения. Применяя для целей конфигурирования ПЛИС, можно исключить разработку шаблонов и сравнительно простыми способами получить эффективные средства построения цифровых систем, содержащие набор схем с необходимым функционированием. ПЛИС для потребителя они являются специализируемыми, а для промышленности - стандартными изделиями (со всеми вытекающими из этого выгодами). Применение ПЛИС позволяет кардинально решить проблему реализации вычислительной системы целиком на основе микросхем с высоким уровнем интеграции без резкого увеличения корпусов и внешнего монтажа. Архитектуры ПЛИС разрабатываются фирмами Хilinx, Actel, Altera, Atmel, Agere Systems (ранее Lucent Technologies), QuickLogic и др. Наиболее полную номенклатуру ПЛИС и комплекты программного обеспечения разработок на российском рынке предлагают компании Xilinx и Altera. Фирма Xilinx, являясь ведущим мировым производителем ПЛИС, предоставляет разработчикам широкий спектр кристаллов с различной технологией производства, степенью интеграции, архитектурой, быстродействием, потребляемой мощностью и напряжением питания, выпускаемых в различных типах корпусов и в нескольких вариантах исполнения, включая промышленное, военное и радиационностойкое. Кристаллы, выпускаемые фирмой Xilinx, в полной мере реализуют преимущества ПЛИС по сравнению с "жесткой логикой". С позиции методического обеспечения при обучении основам проектирования систем на ПЛИС целесообразнее ориентироваться на фирму Xilinx, исходя из следующего: фирма имеет специальную программу поддержки университетов; по своим функциональным возможностям изделия фирмы перекрывают весь ряд интегральных схем с программируемой пользователем структурой, включая ИС, содержащие встроенные микропроцессоры и микроконтроллеры; разработана и доступна для пользователей достаточно полная номенклатура инструментальных модулей для разработки проектов на основе ПЛИС Xilinx; имеется мощный пакет программного обеспечения разработок, распространяемый бесплатно.