Книга руденко, Волкова

advertisement

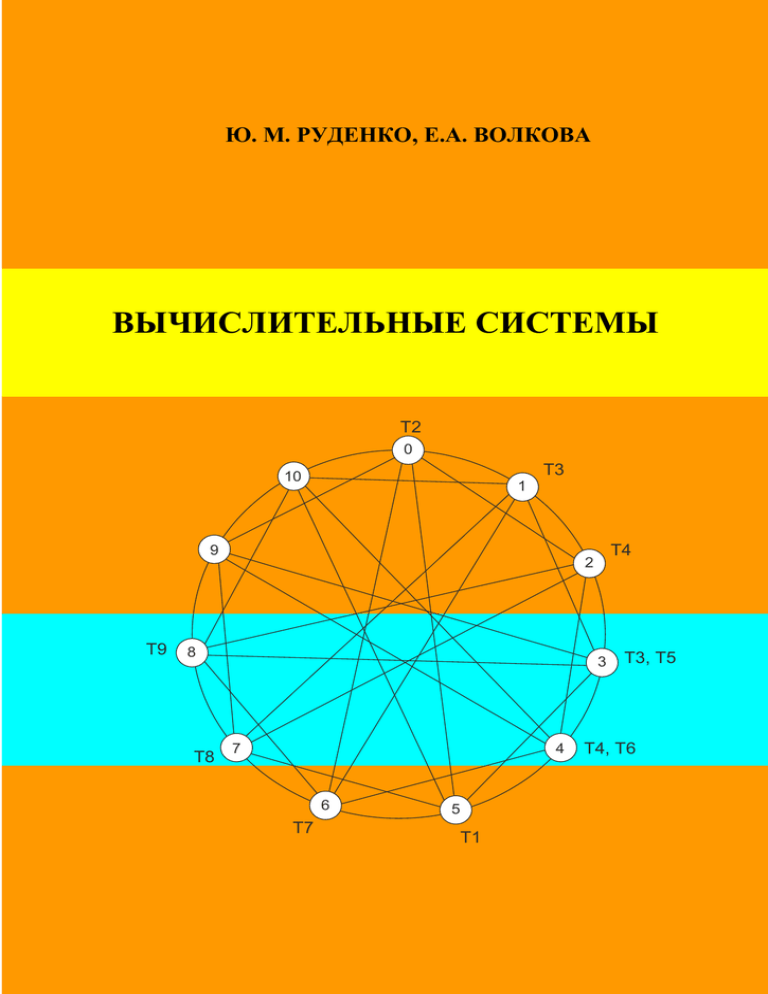

Ю. М. РУДЕНКО, Е.А. ВОЛКОВА

ВЫЧИСЛИТЕЛЬНЫЕ СИСТЕМЫ

T2

0

T3

10

1

9

T9

8

T8

T4

2

3

7

4

6

T7

5

T1

T3, T5

T4, T6

Ю.М. Руденко, Е.А. Волкова

Вычислительные

системы

Архитектура и составляющие её компоненты

Представление параллельных алгоритмов и

оптимизация времени их решения

Москва

Издательство МГТУ имени Н.Э.Баумана

2009

УДК 685.32:519.68(075.8)

ББК

Рецензенты

Руденко Ю.М., Волкова Е.А.

Вычислительные системы.

Предлагаемое учебное пособие рассматривает вопросы, связанные с разработкой и

эксплуатацией вычислительных систем. Подробно излагаются проблемы оценки

производительности и другие эксплутационные характеристики этих систем, принципы

технической реализации, архитектурные свойства и структурные характеристики.

Приведены описания наиболее удачных, на наш взгляд, коммуникационных сред и

коммутаторов. Даны краткие описания параллельных библиотек «Open MP» и «MPI». В

нём представлена вторая составляющая процесса решения параллельных задач представление параллельных алгоритмов с помощью граф-схем, методы построения

ветвей параллельных алгоритмов и размещение их в узлах вычислительных систем.

Учебное пособие предназначено для студентов и магистров технических высших учебных

заведений, университетов, а так же аспирантов и научных работников, работающих в этом

направлении, и написано на основании цикла лекций, читаемых в МГТУ им. Н. Э.

Баумана.

© Издательство МГТУ имени Н.Э.Баумана

3

Оглавление

ГЛАВА 1. АРХИТЕКТУРА ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ ................................................9

1.1. Количественные характеристики, применяемые для оценок параметров

вычислительных систем............................................................................................................9

1.1.1. Вопросы к разделу 1.1. ......................................................................................................13

1.2. Понятие о современных вычислительных системах .................................................13

1.2.1 Вопросы к разделу 1.2. ....................................................................................................16

1.3. Структура современных вычислительных систем ....................................................16

1.3.1. Схема обмена с помощью структуры «Общая шина» .................................................17

1.3.2. Схема обмена с помощью структуры «Линейка»........................................................17

1.3.3. Вычислительная система, имеющая структуру типа «Кольцо».................................18

1.3.4. Схема обмена с помощью структуры типа «Решётка» ................................................18

1.3.5. Схема обмена с помощью структуры типа «Двумерный тор» .....................................19

1.3.6. Схема обмена с помощью структуры типа «n-мерный двоичный гиперкуб» или

«nD-куб» .......................................................................................................................................20

1.3.7. Реализация обмена с помощью структуры типа «Обобщенный nD-куб».................21

1.3.8. Структура ВС типа «N-мерный обобщённый тор» ......................................................21

1.3.9. Структура ВС с сетью типа «Циркулянт» .....................................................................22

1.3.10. Вычислительная система «Максимальный обхват» ...................................................23

1.3.11. Вычислительные системы со структурой сетей типа «Симметричные графы» .......24

1.3.12. Вычислительные системы с сетью связей типа «Гомоморфные графы» ..................25

1.3.13. Вычислительные системы с сетью связей типа «Граф Л(N,v,g)» ...............................28

1.3.14. Структура вычислительной системы типа «Бинарное дерево T0(n) глубины n» ....37

1.3.15. Структура вычислительной системы типа «Мультидерево глубины n и

ширины k T1(n,k)» ......................................................................................................................38

1.3.16 Вопросы к разделу 1.3 .....................................................................................................39

1.4. Коммуникационные среды вычислительных систем ...............................................39

1.4.1. Коммуникационная среда на основе масштабируемого когерентного

интерфейса SCI ............................................................................................................................40

1.4.2. Коммуникационная среда на основе технологии Myrinet ...........................................41

1.4.3. Краткая характеристика коммуникационной среды QsNet II .......................................42

1.4.4 Вопросы к разделу 1.4 .....................................................................................................44

1.5. Коммутаторы вычислительных систем ......................................................................44

1.5.1. Типы коммутаторов..........................................................................................................44

1.5.2 Управление коммутаторами ...........................................................................................47

1.5.3 Алгоритмы определения маршрутов .............................................................................48

1.5.4 Дедлоки в составных коммутаторах ..............................................................................48

1.5.5 Вопросы к разделу 1.5 .....................................................................................................49

1.6 Процесс функционирования вычислительных систем..............................................49

1.6.1 Вопросы к разделу 1.6. ....................................................................................................50

1.7 Принципы технической реализации ВС .....................................................................50

1.7.1. Вопросы к разделу 1.7 .......................................................................................................52

1.8. Архитектурные особенности ВС ...................................................................................52

1.8.1. Архитектурные свойства ВС ..........................................................................................52

1.8.2. Схема обмена информацией между ветвями параллельных алгоритмов ................53

1.8.3. Опыт применения методики крупноблочного распараллеливания сложных задач .56

1.8.4. Архитектурные аспекты при создании ОС ВС .............................................................56

1.8.5. Структурные характеристики ВС ..................................................................................57

1.8.6. Классификация структур ВС ..........................................................................................58

1.8.7. Вопросы к разделу 1.8. ....................................................................................................60

4

ГЛАВА 2. РЕАЛИЗАЦИЯ ПАРАЛЛЕЛЬНЫХ АЛГОРИТМОВ ............................................61

2.1. Реализация параллельных алгоритмов ..........................................................................61

2.1.1. Определение параллельного алгоритма ..........................................................................61

2.1.2. Организация динамического распараллеливания в суперскалярных

микропроцессорах .......................................................................................................................62

2.1.3. Предварительная выборка команд и предсказание переходов ....................................64

2.1.4. Декодирование команд, переименование ресурсов и диспетчеризация ....................64

2.1.5. Исполнение команд .........................................................................................................65

2.1.6. Работа с памятью ............................................................................................................66

2.1.7. Завершение выполнение команды .................................................................................68

2.1.8. Направления развития суперскалярной архитектуры ..................................................68

2.1.9. Мультитредовая модель выполнения программы ........................................................70

2.1.10. Аппаратные и программные средства, необходимые для мультитредовой

архитектуры .................................................................................................................................71

2.1.11. Специфика мультитредовых моделей распараллеливания .........................................73

2.1.12. Вопросы к разделу 2.1 .....................................................................................................74

2.2.Организация распараллеливания на уровне программных модулей............................74

2.2.1. Примеры организации вычислений на уровне программных модулей .....................74

2.2.2. Решение системы линейных уравнений методом Гаусса с помощью ВС типов

«решётка» и «линейка» ...............................................................................................................86

2.2.3. Исполнение алгоритма Гаусса на «решётке» n*n ВM ...................................................88

2.2.4. Исполнение алгоритма Гаусса на «линейке», состоящей из n ВМ ..............................89

2.2.5. Показатели эффективности параллельных алгоритмов ................................................91

2.2.6. Понятие о сложных задачах .............................................................................................92

2.2.7. Вопросы к разделу 2.2 .......................................................................................................93

ГЛАВА 3. НАДЕЖНОСТЬ И ЖИВУЧЕСТЬ ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ ..................94

3.1. Основные задачи создания отказоустойчивых систем .............................................94

3.1.1 Вопросы к разделу 3.1 .....................................................................................................94

3.2. Классификация типов отказоустойчивости сложных систем и ее критерии ..........95

3.2.1 Вопросы к разделу 3.2 .....................................................................................................97

3.3. Способы обеспечения отказоустойчивого функционирования ВС .........................98

3.3.1. Диагностическое тестирование ВС..................................................................................99

3.3.3. Способы восстановления отказоустойчивых ВС .........................................................101

3.3.4 Вопросы к разделу 3.3 ...................................................................................................102

3.4. Построение живучих ВС на основе экспоненциально- надежностного подхода ...103

3.4.1. Показатели надежности ВС ............................................................................................105

3.4.2. Методика расчета показателей надежности ВС .........................................................105

3.4.3. Живучесть ВС ..................................................................................................................107

3.4.4. Вопросы к разделу 3.4 ....................................................................................................110

3.5. Построение живучих ВС, работоспособных в расчетном диапазоне кратностей

отказов ....................................................................................................................................110

3.5.1. Вопросы к разделу 3.5 ....................................................................................................114

3.6. Реализация модели отказоустойчивых систем ............................................................114

3.6.1. Горячий резерв .................................................................................................................114

3.6.2. Репликация ......................................................................................................................115

3.6.3. Кластеры высокой готовности .......................................................................................115

3.6.4. Вопросы к разделу 3.6 .....................................................................................................117

ГЛАВА 4. БИБЛИОТЕКА ПАРАЛЛЕЛЬНЫХ ПРОГРАММ ...............................................118

4.1 Характеристика параллельных языков программирования ........................................118

4.1.1 Характеристика спецификаций OpenMP .....................................................................118

4.1.2. Принципиальная схема программирования в OpenMP ...............................................119

4.1.3. Описание основных конструкций OPEN MP ..............................................................121

5

4.1.4. Способы построения параллельных программ.............................................................126

4.1.5 Спецификация OpenMP для языков C и C++ ..............................................................128

4.1.6. Вопросы к разделу 4.1 ....................................................................................................129

4.2. Основы построения библиотеки MPI ...........................................................................130

4.2.1. Основные понятия ...........................................................................................................130

4.2.2. Структура программ в MPI.............................................................................................132

4.2.3. Определение структуры приходящего сообщения .....................................................135

4.2.4. Определение базовых характеристик коммуникационной сети ................................ 136

4.2.5 Анализ тупиковых ситуаций при обмене ....................................................................138

4.2.6. Организация передачи-приёма сообщений без блокировки ......................................139

4.2.7. Реализация отложенных запросов на взаимодействие ...............................................141

4.2.8. Сравнительная оценка различных способов обмена данными ...................................142

4.2.9. Использование глобальных операций в MPI ...............................................................143

4.2.10. Взаимодействие процессов в MPI ................................................................................143

4.2.11. Вопросы к раделу 4.2 ...................................................................................................146

ГЛАВА 5. Граф-схемы параллельных алгоритмов ................................................................ 147

5.1. Представление параллельных алгоритмов в виде граф-схем ....................................147

5.1.1. Преобразование последовательных алгоритмов в параллельные ..............................147

5.1.2.Использование граф-схем для представления параллельных алгоритмов .................157

5.1.3. Вопросы к разделу 5.1 .....................................................................................................159

5.2.1. Вычисление матриц следования, расширенных матриц следования и матриц

следования с транзитивными связями .....................................................................................159

5.2.2. Вопросы к разделу 5.2 .....................................................................................................168

5.3.1. Построение матрицы логической несовместимости. .................................................168

5.3.2. Построение матрицы логической несовместимости операторов ...............................172

5.3.3. Вопросы к разделу 5.3 .....................................................................................................174

5.4.1. Построение множеств взаимно независимых операторов. .........................................175

5.4.2. Вопросы к разделу 5.4 .....................................................................................................177

ГЛАВА 6. Исследование информационных граф-схем со скалярными весами для

планирования параллельных вычислений ...........................................................................178

6.1. Численные характеристики информационных граф-схем со скалярными весами ..178

6.1.1 Определение ранних и поздних сроков окончания выполнения операторов. ...........178

6.1.2. Определение функций плотности загрузки, и минимальной загрузки для

информационных граф-схем ....................................................................................................181

6.1.3. Вопросы к разделу 6.1 .....................................................................................................184

6.2.1. Распределение операторов по ВМ вычислительной системы с общим полем памяти

для информационной граф-схемы ...........................................................................................185

6.2.2. Распределение операторов по ВМ вычислительной системы с общим полем памяти

для информационно-логической граф-схемы .........................................................................188

6.2.3. Распределение операторов по ВМ вычислительной системы с распределённой

памятью для информационной граф-схемы ...........................................................................190

6.2.4. Реализация диаграмм для общепринятых способов обмена данными между ВМ

вычислительной системы с распределённой памятью для информационной граф-схемы196

6.2.5. Вопросы к разделу 6.2 .....................................................................................................198

ГЛАВА 7. Исследование информационных граф-схем решаемых задач с векторными

весами для планирования параллельных вычислений .........................................................200

7.1 Информационная граф-схема решаемых задач с векторными весами вершин ....200

7.1.1 Понятие об неоднородных системах .............................................................................200

7.1.2. Основные определения, используемые для неоднородных ВС ..................................202

7.1.3. Вопросы к разделу 7.1 .....................................................................................................205

Литература .................................................................................................................................206

6

Введение

Повышение быстродействия вычислительных систем (ВС) является актуальнейшей

задачей современной науки и техники. В данной работе будут рассматриваться

архитектура ВС, как совокупность вычислительных модулей (ВМ), и методы их

организации. Под вычислительным модулем (ВМ) будем понимать процессор или ЭВМ.

Не менее важным вопросом является планирование параллельных вычислений

применительно к ВС, созданных на базе фон-неймановских или гарвардских архитектур,

которые в настоящее время получили наибольшее распространение. В основу первой и

второй главы предлагаемого учебного пособия положены материалы работ [1,2] и

собственные исследования автора. Глава третья представляет собой существенно

переработанные в соответствии с духом времени идеи и методы, предложенные в [3,4].

Более подробное описание рассматриваемых вычислительных устройств, а также

программ приводится в соответствующей цитируемой литературе и в интернете.

Процесс создания быстродействующих ВС развивается по трем основным

направлениям:

1. Совершенствование элементной базы ВС:

1.1. Использование сверхбольших (СБИС) и гипербольших интегральных схем

(ГБИС) с все увеличивающейся плотностью активных элементов (транзисторов) на

единицу площади и скоростью их срабатывания;

1.2. внедрение в СБИС оптоэлектронных элементов;

1.3. перевод СБИС на работу в оптическом диапазоне.

2. Совершенствование архитектур ВС.

2.1. Широко используемые ВС, построенные на основе вычислителей классических

фон-неймановских и гарвардских архитектур совершенствуются за счёт сокращения

времени доступа к обрабатываемым данным, уменьшением времени выполнения

инструкций процессоров. Особенно перспективным является создание архитектур,

позволяющих распараллеливать вычисления на различных уровнях. Различаются три

класса ВС: симметричные мультипроцессоры (SMP), кластеры и массово–параллельные

системы (МРР).

2.1.1. Симметричные мультипроцессоры включают в себя совокупность

процессоров, имеющих общее поле памяти с единым адресным пространством.

2.1.2. Кластеры состоят из совокупности процессоров, объединённых либо сетью

или разделённые устройствами внешней памяти. Используются, например, средства

MEMORY CHANNAL фирмы DEC, AWS фирмы NCR, или локальные, универсальные и

глобальные сети, такие как Ethernet, FDDI (Fiber distributed Data Interface), сети с

протоколами TCP/IP (Transmission Control Protocol/Internet Protocol), или дисковые

массивы с высокоскоростными двойными и квадро PCI SCSI контролерами. Кластер

может включать до нескольких сотен вычислителей и обеспечивать живучесть при

отказах некоторых элементов его оборудования.

2.1.3. Массово – параллельные системы характеризуются высокой пропускной

способностью, возможностью совмещения передач информации с одновременной её

обработкой,

поддержание

различных

топологий,

масштабируемость

и

конфигурируемость.

3. Развитие архитектур ВС, использующих другие принципы обработки данных. В

качестве примера можно привести ВС, использующие нейронные, ассоциативные

процессоры [10,11].

4. Создание новых вычислительных методов и алгоритмов, позволяющих

сокращать время получения требуемой величины, ориентированные на использование

современных архитектур ВС.

Следует отметить, что эти четыре основных направления связаны друг с другом,

взаимно дополняют друг друга. Так, например, при создании СБИС гораздо проще

7

реализовать периодические структуры электронных схем. Это же свойство сушественно

упрощает проектирование ВС для параллельных вычислений.

Разработка архитектур параллельных ВС требует создания новых вычислительных

методов и алгоритмов и, наоборот, некоторые эффективные вычислительные методы

порождают новые архитектуры ВС.

Специфика использования оптических БИС требует разработки принципиально

новых методов и средств обработки данных и т. д.

В связи с появлением вычислительных систем (ВС) актуальнейшей проблемой

стала разработка параллельных алгоритмов и программ, которые являются основными,

чуть ли не главными компонентами этих систем. Решение этих проблем поставило перед

разработчиками много новых проблем. В частности, в казалось бы более или менее

законченной области человеческих знаний – математике потребовалось создание новых

методов, позволяющих вычислять требуемые результаты, получая промежуточные данные

одновременно на нескольких ВМ. Второй важной проблемой является создание на базе

существующих математических методов параллельных алгоритмов решения задач на ВС,

учитывающих архитектуры используемых ВС. Третьей важной проблемой является

создание эффективных параллельных языков программирования. Конечно, список

проблем на этом не заканчивается и можно продолжать этот список ещё достаточно долго.

Темой исследования данной работы являются способы представления

параллельных алгоритмов, также методы отображения этих алгоритмов на структурах ВС.

Было бы неправильно забыть о громадном количестве программ, которые были созданы

для ЭВМ, поэтому в начале этой работы предлагаются методы и алгоритмы для

преобразования последовательных алгоритмом и программ в параллельные. Это

преобразование во многих случаях может вызвать большие затруднения, так как

параллельная программа должна быть представлена в виде совокупности процедур и

функций. Обмен данными между ними должен осуществляться с помощью аппарата

формально – фактических параметров. Использование глобальных параметров различных

уровней проблематично, так как затушёвывается зависимость по данным между

процедурами и функциями. Выделить участок программы, и оформить его в виде

процедуры или функции для создания параллельной секции, как это делается в Open MP,

и добиться от этого выделения некоторого эффекта при распараллеливании, может только

программист. Транслятор в этом случае может создавать параллельные ветви только для

циклов по счётчику циклов. Безусловно, здесь также надо учитывать, что реализация

программы на ВС требует, как правило, гораздо больших накладных расходов, поэтому не

всякое преобразование последовательной программы в параллельную может быть

эффективно и требует предварительных оценок при выборе структур ВС для решения

рассматриваемой задачи. Для тех, кто имел дело с представлением параллельных

алгоритмов с помощью схем алгоритмов по ГОСТ 19.003-80 ЕСПД, ГОСТ 19.701-90

ЕСПД, было понято, что эти схемы мало соответствуют требованиям к изображению

параллельных алгоритмов и способов их отображения на структуры ВС. Поэтому в

данной работе предлагается дополнение к этим ЕСПД для изображения алгоритмов в виде

граф-схем, которые легко отображаются на структуры ВС с помощью библиотек

Open MP, MPI и др. Конфигурации граф-схем позволяют представить в удобной форме

все существующие операторы последовательных языков программирования, а также

представлять схемы обмена данными между ВМ. На базе граф-схем создаются различные

схемы анализа параллельных алгоритмов: матрицы следования, множества взаимно

независимых операторов, внешние и внутренние замыкания в граф-схемах, определения

минимального количества ВМ, обеспечивающих минимальное время решения задачи,

построение нитей в граф-схемах алгоритмов решаемой задачи, распределение нитей

по ВМ и т.д.

8

ГЛАВА 1. АРХИТЕКТУРА ВЫЧИСЛИТЕЛЬНЫХ

СИСТЕМ

1.1. Количественные характеристики, применяемые для оценок

параметров вычислительных систем

Широко распространённым и наиболее простым показателем эффективности

вычислительных модулей является тактовая частота, которая показывает, сколько

элементарных операций может быть выполнено в единицу времени (обычно – в секунду).

Элементарная операция, например, — это опрос регистра, запись кода числа в разряд

регистра, учёт единицы переноса в одном разряде сумматора. В настоящее время частота

может измеряться в герцах, килогерцах, мегагерцах, гигагерцах и т.д. Соотношение

между этими единицами и принятые обозначения выглядят следующим образом (в

круглых скобках приведено обозначение на английском языке):

1 МегаГц (MegaHz) = 1 МГц (MHz)= 10 6 Гц (Hz),

1 ГигаГЦ (GigaHz ) = 10 3 (МГц) MHz = 109 Гц (Hz).

Очевидно, что этот параметр может характеризовать вычислительную систему

только приблизительно. Если взять тактовую частоту и умножить на количество

вычислительных модулей в системе (или усреднённую тактовую частоту для

неоднородных систем), то можно получить некоторое представление о

производительности ВС. Следует отметить, что при этом не будут учтены архитектурные

особенности вычислителей, коммуникационных сред и характер задач, которые будут

решаться на данной вычислительной системе. Кажется целесообразным перенести все

вычисления производительностей вычислительных модулей

на определения

производительности ВС, произведя необходимые коррекции. Дело в том, что решение

задачи на вычислительных устройствах аналогичны по организации вычислений. Вначале

осуществляется ввод данных, преобразование их, затем, собственно, обработка. В связи с

этим методы, используемые для оценок производительности вычислительных модулей, с

некоторыми уточнениями можно использовать для оценок производительности ВС.

Безусловно, ВС имеют более сложную структуру, поэтому при оценке

производительности необходимо учесть архитектурные свойства ВС, класс решаемых

задач и степень соответствия класса решаемых задач архитектуре ВС.

Количество операций в секунду является основной величиной для определения

производительности

вычислительных

устройств.

Единицами

измерения

производительности над числами с фиксированной точкой являются

1 MIPS(millions of instructions per second) = 10 6 операций/секунду;

1 GIPS = 109 операций/секунд.

(1.1.1)

Длительность арифметической операции над числами с плавающей точкой

существенно больше при прочих равных условиях, поэтому в этих случаях используются

другие единицы:

1 FLOPS (floating point operations per second) = 1 операция

с плавающей точкой/секунду

1 MegaFLOPS = 1 M FLOPS = 10 6 FLOPS (миллион операций

с плавающей точкой/секунду)

1 GigaFLOPS = 1 G FLOPS = 109 FLOPS (миллиард операций

с плавающей точкой/секунду)

1 TeraFLOPS = 1 T FLOPS = 1012 FLOPS (триллион операций

с плавающей точкой/секунду )

(1.1.2)

9

1 PetaFLOPS = 1 P FLOPS = 1015 FLOPS (квадриллион операций

с плавающей точкой/секунду )

В реальных условиях в решаемых задачах используются арифметические операции

над целыми числами, над числами с плавающей точкой. В этом случае используется

номинальное или пиковое быстродействие, которое определяется как

k

,

(1.1.3)

p k

tj

j 1

где k – количество выполняемых операций, t j – время выполнения j-й операции из

множества операций R вычислительного модуля. При вычислении n операций вводавывода информация с внешних устройств не учитывается. Для однородной ВС этот

показатель выразится в виде:

k *N

,

(1.1.4)

*p k

*

t j

j 1

где N – количество вычислительных модулей в однородной ВС, k – количество

выполняемых операций, t *j – время выполнения j-й операции из множества операций R

вычислительного модуля.

Для случая неоднородной системы номинальное быстродействие выразится как

n

(k * N )

н

(1.1.5)

p ( ( iki i )) / n ,

*

i 1

t ji

ji 1

где Ni – количество вычислительных модулей i–го типа в неоднородной системе, ki –

операции, выполняемые i-м типе вычислительного модуля, n – число типов

вычислительных модулей, t *ji – время выполнения j-й операции на i-м типе ВМ.

В случае не равновероятного выбора операций используется быстродействие

вычислительного модуля по Гибсону:

1

,

(1.1.6)

g k

t j p j

j 1

Здесь p j – вероятность выбора j-й операции, j 1, k ,

k

p

j 1

j

1.

Для однородной ВС её быстродействие по Гибсону выразится соотношением

N

,

(1.1.7)

g* k

*

tj pj

j 1

где N – количество вычислительных модулей в однородной системе, t*j – время

выполнения j-й операции из множества операций R вычислительного модуля, рj –

вероятность выполнения j-й операции.

Для неоднородной ВС это быстродействие может быть определено, как

n

N

(1.1.8)

gн ( ( ki i )) / n,

*

i 1

t ji p j i

ji 1

10

где Ni – количество вычислительных модулей в неоднородной системе, ki – операции,

выполняемые на i-м типе вычислительного модуля, n – число типов вычислительных

модулей, t *ji – время выполнения j-й операции на i-м типе вычислительного модуля, p ji –

вероятность выполнения j-й операции на i-м типе вычислительного модуля.

Вероятности p j , или p ji ещё называют весовыми коэффициентами. Существуют

определённые наборы коэффициентов, которым соответствуют наборы тестов – т.н. смеси

Гибсона.

Если соотношения (1.1.3 – 1.1.8) применяются только к арифметическим

операциям над целыми числами, то единицей измерения служит MIPS или GIPS согласно

соотношению (1.1.1). В остальных случаях (для чисел с фиксированной и плавающей

точкой) используется соотношение (1.1.2). В качестве примеров таких тестов могут

служить тесты SPECint95 и SPECfp95 [5-9].

Все вышеперечисленные показатели не учитывают обмены информацией между

устройствами. Для учёта этих зависимостей вводят наборы типовых задач

Z Z1 , Z 2 ,..., Z m . Для задачи Z j Z известно количество выполняемых операций i (с

учётом операций ввода-вывода и операций обмена информацией) и время выполнения

вычислительных операций t j . Быстродействие вычислительного модуля при решении

типовой задачи будет:

j j ,

(1.1.9)

tj

Определяются вероятности спроса на типовые задачи в виде

k

j 1

j

1 , 2 ,..., k

1 , тогда среднее быстродействие вычислительного модуля:

ср

1

(1.1.10)

j

j 1 j

Использование соотношения (1.1.10) для однородных ВС может быть использовано

k

в виде

ср*

N

,

(1.1.11)

j

j 1 j

где N – количество вычислительных модулей в ВС.

При использовании соотношения (1.1.10) для неоднородных ВС его необходимо

модифицировать, учитывая наличие n типов вычислительных модулей

n

N

срн ( k i ) / n ,

(1.1.12)

ji

i 1

k

j 1

ji

Для использования показателей (1.1.10-1.1.12) существует множество специальных

тестовых наборов Z. Наиболее известным является набор LINPACK [5-9], определяющий

производительность вычислительных модулей при решении систем линейных уравнений.

Естественно, что применимость тестовых наборов Z должна быть обеспечена для

различных архитектур вычислителей, по крайней мере на уровне языков высокого уровня.

Показатель (1.1.7), как нетрудно заметить, в сильной степени зависит от выбора

системы тестов Z. Поэтому в отдельных случаях чтобы уменьшить эту зависимость,

вводят унифицированные операции и операнды. Унифицированным формам данных

может быть выбран байт. В качестве унифицированной операции выбирают, например,

11

операцию

сравнения

данных.

унифицированную, в виде

Все остальные операции выражаются через

Uf

Kf

, где Uf – рассматриваемая операция, U –

U

унифицированная операция.

Унифицированное быстродействие для j–ого теста определяется как:

V

ун j j ,

tj

(1.1.13)

где V j – количество унифицированных операций в тесте Z j Z , t j – время решения

задачи Z j , которое учитывает как время решения самой задачи, так и накладные расходы

(на преобразование, ввод-вывод информации) и т.д.

Среднее унифицированное быстродействие определим

ун

1

j

j 1 ун j

m

,

(1.1.14)

где j – вероятность вызова Z j типовой задачи.

Для однородных систем среднее унифицированное быстродействие определится

как

N

ун* m

,

(1.1.15)

j

j 1

ун j

где N – количество вычислительных модулей в однородной ВС.

Неоднородные ВС, имеют в своём составе n типов вычислительных модулей,

поэтому среднее унифицированное быстродействие представится в виде

n

N

унн ( n i ) / n ,

(1.1.16)

i 1

j

ji 1

i

унi

При оценке быстродействия ВС все вышеприведенные показатели могут служить

основой для получения соответствующих характеристик производительности ВС, хотя

принципиальным вопросом здесь является выбор соответствующих тестов. Существует

способ использования пиковой производительности для определения составной

теоретической производительности ВС, который характеризует зависимость от тактовой

частоты, набора функциональных устройств, разрядной сетки и др., хотя совершенно не

учитывает взаимодействие структур решаемой задачи и ВС. Для получения реальные

оценки производительности осуществляются с помощью создания специальных тестовых

наборов. К настоящему моменту наметились три пути создания тестовых наборов:

1) тесты, разработанные фирмами-изготовителями ВС специально для отработки

качества выпускаемой продукции, которые для широкого круга пользователей не

применимы,

2) тесты, разработанные фирмами-изготовителями ВС для широкого круга

пользователей, которые применимы в большинстве случаев и дают хорошие результаты. К

таким пакетам относятся пакеты Linpack, пакеты группы производителей SPEC, TPC и

др. [5-9]. Так, например, пакеты Linpack используются при ежегодном формировании

списка TOP 500, в котором определены 500 самых быстродействующих ВС. Этот список

можно найти в Internet под указанным именем [7].

12

3) третья группа тестов создаётся, как правило, пользователями, и учитывают

внутренние условия применения ВС.

Ёмкость памяти ВС, несомненно, является одной из основных характеристик ВС

и существенно влияет на быстродействие ВС, а также на её другие важные параметры.

Представляют интерес единицы измерения ёмкости памяти ВС и порядок величин, с

которыми оперирует современная вычислительная техника. Ниже приведены единицы

измерения ёмкости памяти ВС и порядок величин, с которыми оперирует современная

вычислительная техника (в круглых скобках приведены английские сокращения):

1 Килобит (KiloBit) = 1 Кбит (KBit) = 1024 бит (Bit) = 210 бит (Bit);

1 Килобайт (KiloByte) = 1 Кбайт (KByte) = 1024 байт (Byte) = 210 байт (Byte);

1 Мегабит (MegaBit) = 1 Мбит = 1024 Кбит = 220 бит;

1 Мегабайт (MegaByte) = 1 Мбайт (Mbyte) = 1024 Кбайт (Кbyte) = 220 байт (byte);

1 Гигабит (GigaBit) = 1 Гбит (GBit) = 1024 Мбит(МBit) = 230 бит (Bit);

1 Гигабайт (GigaByte) = 1 Гбайт (Gbyte) = 1024 Мбайт (Мbyte) = 230 байт (Byte);

1 Терабит (TeraBit) = 1 Тбит (TBit) = 1024 Гбит (GBit) = 240 бит (Bit) ;

1 Терабайт (TeraByte) = 1 Тбайт (TByte) = 1024 Гбайт (GByte) = 240 байт (Byte);

1 Петабит (PetaBit) = 1 Пбит (PBit) = 1024 Тбит (TBit) = 250 бит (Bit);

1 Петабайт (PetaByte) = 1 Пбайт (PByte) = 1024 Тбайт (TByte) = 250 байт (Byte).

Быстродействие памяти характеризуется так же скоростью обмена информацией

между памятью и другими устройствами вычислителя. В качестве единицы измерения

этой величины используется:

1 бод (boud) = 1 бит/сек (bit per second);

1 Килобод (Kiloboud) = 1 Кбод (Kboud) = 103 бод (boud);

1 Мегабод (Megaboud) = 1 Мбод (Mboud) = 106 бод;

1 Гигабод (Gigaboud) = 1 Гбод (Gboud) =109 бод;

1 byte/s = 1 байт/сек;

1 Килобайт/сек (Кilobyte/s) =1 Кбайт/сек ( Кbyte/s) = 103 байт/сек;

1 Мегабайт/сек (Мegabyte/s) = 1 Мбайт/сек(Мbyte/s) ) = 106 байт/сек.

1.1.1. Вопросы к разделу 1.1.

1. Чем отличается пиковая нагрузка ЭВМ от пиковой нагрузки ВС ?

2. В чём особенность унифицированного быстродействия ?

3. Какие особенности перехода от оценок быстродействия для ЭВМ к оценкам

быстродействия для ВС ?

4. Почему для оценок быстродействия используется система тестов ?

5. Чем отличается оценка быстродействия для однородных систем от оценки

быстродействия для неоднородных систем ?

6. Какие типы тестов существуют ?

7. Какие принципы положены в формирование единиц измерения параметров ВС ?

1.2. Понятие о современных вычислительных системах

Повышение быстродействия вычислений в случае необходимости в эпоху

отсутствия компьютеров осуществлялся за счёт увеличения коллектива вычислителей

(людей, занятых вычислениями). В этом коллективе существовала определённая

технология проведения вычислений, которая, в конечном счёте, позволяла производить

необходимые вычисления. Как показала практика, организация вычислений в

современных ВС во многом копирует опыт, накопленный коллективами вычислителей. В

связи с этим, целесообразно при формулировании исходных определений для ВС

использовать понятия, выработанные при выполнении соответствующих работ

человеческими коллективами вычислителей. Иными словами, можно сказать, что

13

сущность ВС составляет коллектив аппаратно-программных вычислителей, акцентируя

внимание на методах взаимодействия между вычислителями в этих коллективах. В

дальнейшем, при изложении материала вычислитель назван вычислительным модулем

(ВМ), который подразумевает использование процессора или ЭВМ. В литературе вместо

использования термина «вычислительный модуль» можно встретить термины «элементарный процессор», «элементарная машина» и др. Кроме того, архитектура

процессоров

всё

время

совершенствуется

–

появляются

транспьютерные,

мультискалярные, мультитредовые, и т. д. процессоры. В тех случаях, когда это

необходимо, будут делаться необходимые разъяснения и ссылки. В настоящее время

разница между понятиями процессор или ЭВМ достаточно условна. В дальнейшем, под

ЭВМ будем понимать процессор, оснащённый собственной операционной системой и

периферийными устройствами. Связи между процессорами или ЭВМ осуществляются с

помощью сетей связи, которые, в общем случае, представляют собой сосредоточенные

или распределённые коммутаторы с шинами связи. Наиболее удачной была шина PCI,

разработанная в 1991 году фирмой Intel. При рассмотрении проблемы оптимизации

структуры ВС надо иметь в виду , что при выборе графа в качестве математической

модели ВС одно ребро на графе, который описывает структуру ВС, физически может

соответствовать коммутируемой

шине, содержащей большое количество

дополнительного дорогостоящего оборудования. Поэтому всякое упрощение структуры

вычислительной сети, при прочих равных условиях, уменьшает её стоимость. Это

обстоятельство порождает на мировом рынке всё новые конфигурации вычислительных

сетей, имеющих определённые достоинства и недостатки в зависимости от

предъявляемых к ним требований. Некоторые из них будут рассмотрены ниже.

Определение 1.2.1. Система, представленная множеством описаний W={K,A}, где

K – описание конструкций ВС, А – описание алгоритма работы множества

вычислительных модулей, называется вычислительной. Описание К составляет

множества значений {M,S}, где М – множество базовых вычислительных устройств

{mi}, i=0, ... , N-1, где под базовыми вычислительными устройствами понимаются ЭВМ,

процессоры, блоки памяти, внешние устройства. S – сеть связей между множествами

элементов базиса.

В конструкцию К должны быть заложены следующие принципы:

а) параллелизм при обработке информации, т.е. организация вычислений

одновременно на множестве вычислительных модулей М с организацией в случае

необходимости обмена данными через сеть S;

б) адаптация конфигурации сети S к решаемой задаче. Алгоритм А обеспечивает

наряду с требуемой обработкой управление одновременной работой определённым

множеством ВМ и необходимым обменом данными между ними.

Изучаемый здесь курс вычислительных систем основывается, в основном, на

теории графов, поэтому напомним несколько определений из этой теории, которые в

дальнейшем будут часто использоваться [12].

Определение 1.2.2. Графы изоморфны, если отличаются только нумерацией

вершин.

Определение 1.2.3. Графы гомоморфные, если второй получен из первого заменой

нескольких вершин графа одной с сохранением оставшихся связей.

Определение 1.2.4. Графы гомеоморфные, если второй получен из первого

разбиением его рёбер (p,q) на (p,r) и (r,q), где r – новая вершна.

14

Определение 1.2.5. Граф регулярен, если степени вершин одинаковы.

Определение 1.2.6. Граф F называется частью графа G, F G, если множество

его вершин V(F) содержится в множестве V(G), а множество рёбер R(F) – в множеств

рёбер R(G).

Определение 1.2.7. Часть графа F G называется суграфом, если множество его

вершин V(F) = V(G).

Определение 1.2.8. Часть графа F G называется подграфом, если множество

его вершин V(F) содержится в множестве вершин V(G), а множество рёбер связывает

только вершины V(G).

Структура вычислительных систем представляется в виде графа GS=(М,S), каждой

вершине которого поставлены в соответствие вычислительные модули mi , i = 0, … , N-1,

а ребра sj,k S – связи между ними, j,k {0, … ,N-1}. Набор связей j,k зависит от

конфигурации сети S.

Для возможности оценки времени, затрачиваемого на обмен информацией между

вычислительными модулями, а также других характеристик, вводятся понятия: регулярная

вычислительная система, диаметр и средний диаметр вычислительной системы.

Определение 1.2.9. Регулярная вычислительная система представляется

неориентированным графом, в котором все вершины графа имеют одинаковую степень

вершин графа, где под степенью вершины понимается количество рёбер, примыкающих к

вершине графа.

Пример графа регулярной вычислительной системы представлен на рисунке 1.2.1.

Определение 1.2.10. Диаметр d – это максимальное расстояние, определяемое как

d = max{ri,j}, i,j {0,…,N-1},

где ri,j – расстояние между вершинами i, j графа рассматриваемой ВС.

Расстояние ri,j есть минимальная длина простой цепи между вершинами i, j, где

длина измеряется в количестве ребер между вершинами i, j.

Например, на рисунке 1.2.1 длины между вершинами (0,5) есть 3 ((0,1),(1,2),(2,5)),

2 ((0,1),(1,5)), 2 ((0,4),(4,5)), 3 ((0,3),(3,4),(4,5)), 3 ((0,3),(3,6),(6,5)), 2 ((0,6,),(6,5)) и др.,

длина которых больше 3-х. Следовательно, расстояние ri,j равно 2. При рассмотрении всех

возможных расстояний определяется d=2.

7

1

6

2

5

3

4

Рисунок 1.2.1. Пример графа регулярной вычислительной системы

Определение 1.2.11.

определяется как

Средний

диаметр

d

pn

i pi

pi

di =

N 1

di

для i-й выделенной вершины

(1.2.1)

15

где pi – расстояние от текущей до i-й выделенной вершины, n pi – число вершин,

находящихся на расстоянии p i от выделенной.

Определение 1.2.12. Средний диаметр для графа вычислительной системы

определяется в виде:

N 1

d

d=

i

i=0

N

Примечание: Для регулярной вычислительной системы d i d .

Сеть S должна обеспечивать в каждый момент времени, требуемый обмен данными

между вычислительными модулями. Наиболее подходящей для этой цели является сеть по

полному графу, т.е. связь каждого вычислительного модуля с каждым. Построение такой

сети для большого количества вычислительных модулей, содержащихся в современных

ВС, является сложной и дорогостоящей процедурой. В связи с чем, разрабатываются

различные типы и конфигурации сетей, в которых обеспечиваются связи в зависимости

от различных требований. Очевидно, что в таких сетях, как правило, возникает

необходимость транзитной передачи информации с помощью вычислительных модулей,

попадающих в контур передачи информации. Такие передачи, естественно, требуют

дополнительных затрат времени, в связи с чем возникает задача минимизации этих затрат

c помощью выбора конструкций тех или иных разновидностей сетей с учетом структуры

решаемых задач. Вследствие этого проблему выбора графа межмодульных связей

необходимо рассматривать в нескольких аспектах:

- минимизация времени выполнения межмодульных обменов;

- максимизация числа одновременно выполняемых обменов;

- максимальная сохранность связности при выходах из строя ВМ и линий.

Таким образом, в качестве критериев выбора графа логично выбрать диаметр и

средний диаметр графа. Диаметр графа определяет максимально необходимое число

транзитных передач, а средний диаметр – среднюю длину транзитного пути. В качестве

показателя, оценивающего вероятность существования межмодульных связей в графе

(при заданных значениях коэффициентов готовности ВМ и линий, компоненты связности,

включающей не менее 0, 1, 2, …, N-1 вершин, где N – количество вычислительных

модулей в системе), используется вектор-функция структурной живучести графа. При

определении данного показателя необходимо произвести достаточно сложные

вычисления. По результатам моделирования оказалось, что минимизация обоих диаметров

является необходимым условием максимизации координат вектор-функции структурной

живучести графа. Поэтому в качестве критерия выбираются диаметр и средний диаметр.

1.2.1 Вопросы к разделу 1.2.

1.

2.

3.

4.

5.

Какие параметры используются при определении ВС?

С какой целью вводится параметр диаметр системы?

В чём сущность параметра средний диаметр системы?

Почему возникает необходимость транзитной передачи информации?

В чём сложность использования конфигурации сети по полному графу?

1.3. Структура современных вычислительных систем

Рассмотрим структуры вычислительных систем по мере усложнения сетей связей

между процессорами. Прообразами современных ВС были вычислительные системы с

простыми коммутаторами с временным разделением, которые называют общими шинами

16

или шинными структурами (см. рисунок 1.3.1) [2]. Шинные структуры наряду с рядом

преимуществ, таких как небольшой объём оборудования, достаточно высокая надёжность,

имеют ряд существенных недостатков. К ним относится особенности, связанные с

методом организации обмена, поэтому принципиально неустранимые:

- одновременная работа только одного передающего устройства,

- наличие арбитра шины, активизирующего в определённые моменты времени

устройства, и требующего для этого определённое время,

- необходимость синхронизации сигналов «запрос-ответ», которая осуществляется

за счёт времени работы шины, и др.

В шинах типа Fastbus, IEEE 960, VME и Futurebus+, IEEE 896.x применены ряд

усовершенствований, позволяющих ускорять процессы обмена, хотя вопрос об

использовании шин в быстродействующих вычислительных системах остаётся открытым.

1.3.1. Схема обмена с помощью структуры «Общая шина»

Схема обмена с помощью структуры «Общая шина» представлена на рисунке

1.3.1 в виде неориентированного графа.

Рисунок 1.3.1. Реализация обмена через общую шину. Вершина графа обозначает

вычислительный модуль, жирная линия – общая шина

Данные от вычислителя поступают в общую шину и в соответствии с

алгоритмом А могут поступать на один из оставшихся вычислителей.

Определение 1.3.1. Структура вычислительной системы типа «Общая шина»

описывается графом GS =(М,S*), где М – множество вычислительных модулей,

определяемых вершинами графа, М ={mi}, {i} ={ 0, … , N-1}, N 3, а S* состоит в

каждый момент времени tk {t1, … , tk*} из одного ребра sqj, где q, j { 0, … , N-1}, q≠j,

q<j, а множество времён {t1, … ,tk*} определяет моменты реконфигурации сети S*.

Как правило, интервал времени tk, в течении которого существует определённая

конфигурация сети связи, определяется операционной системой, управляющей

рассматриваемой коммуникационной средой в соответствии с запросами решаемых задач.

На пути развития вычислительной техники появились структуры, которые в

дальнейшем явились прообразами современных ВС. К ним относятся структуры типа

«линейка» и «кольцо».

1.3.2. Схема обмена с помощью структуры «Линейка»

Схема обмена

с помощью структуры

неориентированного графа на рисунке 1.3.2.

«линейка»

представлена

в

виде

•••

Рисунок 1.3.2. Реализация обмена с помощью структуры «Линейка». Вершина графа

обозначает вычислительный модуль. Многоточие обозначает, что опущены ВМ и

связи между ними

17

Каждый вычислительный модуль, кроме первого и последнего, связан с

соседним. Передача данных, в случае необходимости, осуществляется транзитом через

другие вычислители. Недостатком рассматриваемой структуры является малая

надёжность – отказ вычислителя или связи вызывает отказ «линейки». Достоинством

является простота и относительно малая стоимость её изготовления.

Определение 1.3.2. Структура вычислительной системы типа «Линейка»

описывается графом GS =(М,S*), где М – множество вычислительных модулей,

определяемых вершинами графа, М ={mi}, {i} ={ 0, … , N-1}, N 2, а S* состоит из

множества рёбер sq, q+1 , q {0,1, … , N-2}.

1.3.3. Вычислительная система, имеющая структуру типа «Кольцо»

Вычислительная система, имеющая структуру типа «кольцо» представлена на

рисунке 1.3.3.

Каждый вычислительный модуль связан с соседним. «Кольцо» имеет

преимущество перед структурой типа «Линейка», так как первый вычислительный

модуль непосредственно связан с последним.

•••

Рисунок 1.3.3. Схема обмена с помощью структуры типа «Кольцо».

Определение 1.3.3. Структура вычислительной системы типа «Кольцо»

описывается графом GS =(М,S*), где М – множество вычислительных модулей,

определяемых вершинами графа, М ={mi}, {i}={0, … , N-1}, N 2, а S* состоит из

множества рёбер sq, (q+1)mod(N), q {i}.

Операция (q+1)mod(N) означает остаток от деления по модулю N, т.е. при q=N-1

образуется ребро, связывающее 0 и N-1 вычислители.

1.3.4. Схема обмена с помощью структуры типа «Решётка»

Схема обмена с помощью структуры типа «Решётка» представлена в виде

неориентированного графа на рисунке 1.3.4.

По сравнению с «кольцом» и «линейкой» рассматриваемая структура имеет ряд

преимуществ, в частности, много альтернативных путей обхода при обмене данными

между вычислителями, что существенно увеличивает надёжность рассматриваемой

структуры.

Определение 1.3.4. Структура вычислительной системы типа «Решётка»

описывается графом GS =(М,S*), где М – множество вычислительных модулей,

определяемых вершинами графа, М ={mi}, {i} ={0, … , N-1}, N 4, а S* состоит из

множества рёбер sj, k , j {0,1, … ,Y-1}, k {0,1, … , L-1}, и L*Y=N. Ребро проводится

между вершинами, определяемыми декартовыми произведениями [j] [k]. Две

вершины соединяются ребром, если декартовы произведения отличаются друг от

друга на 1 по координате j или k, соответственно.

На рисунке 1.3.4 анализируемый граф помещён в систему координат j, k. Значения,

определяемые индексом k, откладываются по оси k, индексом j – по оси j. Определение

1.3.4, таким образом, задаёт решётку в системе координат j, k. Пусть, например, задана

решётка 3 4. Тогда образуются декартовы произведения:

18

[0] [0], [0] [1], [0] [2], [0] [3],

[1] [0], [1] [1], [1] [2], [1] [3],

[2] [0], [2] [1], [2] [2], [2] [3]

и, соответственно, образуются рёбра – при k=0, значения j при этом, будут: (0,1),

(1,2); при k=1, значения j при этом, будут: (1,2), (1,1) и т. д.

Рисунок 1.3.4. Реализация обмена с помощью структуры типа «Решётка»

1.3.5. Схема обмена с помощью структуры типа «Двумерный тор»

Схема обмена с помощью структуры типа «Двумерный тор» представлена в виде

неориентированного графа на рисунке 1.3.5. «Двумерный тор» имеет преимущество перед

структурой типа «решётка», так как некоторые граничные ВМ, а возможно и все,

непосредственно связаны друг с другом. Под граничными вычислительными модулями

понимаются ВМ, имеющие максимальную координату по одной из осей.

Рисунок 1.3.5. Реализация обмена с помощью структуры типа «Двумерный тор»

Определение 1.3.5. Структура вычислительной системы типа «Двумерный тор»

описывается графом GS =(М,S*), где М – множество вычислительных модулей,

определяемых вершинами графа, М ={mi}, i = 0, … , N-1, N 5, а S* состоит из

множества рёбер s к, j , k {0,1, … , L-1}, j {0,1, … ,Y-1} и L*Y=N. Ребро проводится

между вершинами, определяемыми декартовыми произведениями [j] [k]. Две вершины

соединяются ребром, если их декартовы произведения отличаются друг от друга на 1

или на L-1 по координате L или – на 1 или на Y-1 по координате Y соответственно.

Примечание. К обобщённому двумерному тору (см. рисунок 1.3.5) относятся также

и ВС, содержащие не все рёбра, имеющие индексы j=Y-1или k=L-1.

19

На рисунке 1.3.5 анализируемый граф помещён в систему координат L,Y. Значения,

определяемые индексом k, откладываются по оси L, индексом j – по оси Y.

Определение 1.3.5, таким образом, задаёт двумерный тор в системе координат L,Y.

1.3.6. Схема обмена с помощью структуры типа «n-мерный двоичный

гиперкуб» или «nD-куб»

Схема обмена с помощью структуры типа «n-мерный двоичный гиперкуб» или

«nD-куб» представлена в виде неориентированного графа на рисунке 1.3.6. Главная

причина выбора данных структур – это простота определения трасс передачи данных.

Различают n-мерный двоичный (булев) гиперкуб и обобщенный гиперкуб.

Определение 1.3.6. Структура вычислительной системы типа «n-мерный

двоичный гиперкуб» или «nD-куб» описывается графом GS =(М, S*), где М – множество

вычислительных модулей, определяемых вершинами графа, М ={mi}, i = 0, … , N-1, N=2n .

n-мерный булев куб задается как декартово произведение n множеств {0,1}. S* состоит

из множества рёбер sv,y, таких, что декартовы произведения v и y, отличаются на

единицу.

Y

Z

y

X

X

Рисунок 1.3.6. Пример представления схем булевых кубов различных размерностей:

а)размерность – два, б) размерность – три, в) размерность – четыре

Недостаток таких графов – необходимо, чтобы каждая вершина имела степень n

(число вершин – 2n). Но существует способ упрощения их построения: вершины

представляются как гомоморфные образы простых циклов с n вершинами. Например,

каждая вершина имеет 3 ребра, два из которых используются для образования цикла и

третье – ребро n-мерного куба. На рисунке 1.3.7 показан пример построения такого графа.

Рисунок 1.3.7. Трехмерный куб (каждая вершина – это цикл длины 3)

20

1.3.7. Реализация обмена с помощью структуры типа «Обобщенный nD-куб»

Реализация обмена с помощью структуры типа «Обобщенный nD- куб»

представлена на рисунке 1.3.8.

Рисунок 1.3.8. Схема представления обобщенного 3-х мерного гиперкуба 2х4х3

Определение 1.3.7. Структура вычислительной системы типа «Обобщенный

nD-куб» описывается графом GS =(М, S*), где М – множество вычислительных

n

модулей, определяемых вершинами графа, М ={mi}, i = 0, … , N-1, N П ( N j ) . По

j 1

каждой координате j, j=1,…,n вводятся точки NJ={0,1, ... , Nj-1}, где Nj – размерность

куба по координате j. Множество вершин графа ВС определяется декартовыми

произведениями [N1] [N2] … [Nn], |N1|·|N2|·…·|Nn|=N. Две вершины соединяются

ребром, если декартовы произведения, определяющие эти вершины, отличаются друг от

друга на 1.

Например, для 3-х мерного обобщённого куба 2х4х3 образуются точки по

координатам x, y, z соответственно (0,1), (0,1,2,3), (0,1,2) и соответствующие декартовы

произведения:

(0,0,0), (0,1,0), (0,2,0), (0,3,0), (1,0,0), (1,1,0), (1,2,0), (1,3,0),

(0,0,1), (0,1,1), (0,2,1), (0,3,1), (1,0,1), (1,1,1), (1,2,1), (1,3,1),

(0,0,2), (0,1,2), (0,2,2), (0,3,2), (1,0,2), (1,1,2), (1,2,2), (1,3,2).

Ребра проводятся между вершинами (0,0,0) и (0,0,1), (0,1,0), (1,0,0). Вершина (0,0,1)

соединяется с вершинами (0,0,0), (1,0,1), (0,1,1), (0,0,2) и т.д. Пример представления этой

структуры показан на рисунке 1.3.8.

1.3.8. Структура ВС типа «N-мерный обобщённый тор»

На основе кубических структур ВС введены торы (для одномерного случая –

кольцевые структуры). N-мерный обобщённый тор образуется из обобщенных n-мерных

кубов построением ребер между отдельными или всеми вершинами, прилегающими к

граничным плоскостям. Так, если ВС построена из обобщенных 2D кубов (3х3), то ребра

могут быть проведены, как показано на рисунке 1.3.9(а). Степень вершины равна 4. На

рисунке 1.3.9(б) показано построение трёхмерного тора из обобщенного 3D куба (2x3x2)

со степенью вершины равной 4.

21

Определение 1.3.8. Структура вычислительной системы типа «обобщенный

nD-тор» описывается графом GS =(М, S*), где М – множество вычислительных

n

модулей, определяемых вершинами графа, М ={mi}, i = 0, … , N-1, N П ( N j ) . По

j 1

каждой координате j, j=1,…,n вводятся точки NJ={ 0,1, ... , Nj-1}, где Nj – размерность

куба по координате j. Множество вершин графа ВС определяется декартовым

произведением [N1] [N2] … [Nn], |N1|·|N2|·…·|Nn|=N. Множество рёбер S*

строится следующим образом: две вершины соединяются ребром, если декартовы

произведения отличаются друг от друга на 1 или на Nj-1 только по координате Nj ,

j {1,…,n } соответственно.

y

z

y

x

x

Рисунок 1.3.9 ВС типа двумерный тор (а) и трёхмерный тор (б)

С помощью дополнительных связей, выделенных на рисунке 1.3.9 жирными

линиями, из 2D-куба построена ВС типа двумерный тор (а), а обобщенный 3D-куб

переведен в ВС типа трехмерный тор (б).

Примечание. К обобщённому n-мерному тору относятся также и ВС, содержащие

не все рёбра, отстоящие на расстоянии Nj-1 по координате j.

1.3.9. Структура ВС с сетью типа «Циркулянт»

В настоящее время в индустрии ВС получили широкое распространение сети

связей типа циркулянтных, которые относятся к классу регулярных сетей связи. Эти

структуры традиционно представляются Dn-графами, каждый из которых описывается в

виде:

Dn=G (N,q1,…,qn),

(1.3.1)

где N – число вершин в графе, вершины нумеруются от 0 до N-1, а q1,…,qn удовлетворяет

условиям:

0<q1<…<qn≤(N+1)/2,

(1.3.2)

где q1,…, qn – множество образующих чисел таких, что множество {q1,…,qn} имеет

наибольший общий делитель, равный 1.

Вершина i соединяется ребрами с вершинами

22

(i q1 )(mod N ),..., (i qn )(mod N ).

(1.3.3)

Функция d (mod) N определяет остаток от деления нацело. Например, 3 (mod) 5=3.

Определение 1.3.9. Структура вычислительной системы типа «Циркулянт»

описывается графом GS =(М,S*), где М – множество вычислительных модулей,

определяемых вершинами графа, М ={mi}, i = 0, … , N-1. Построение сети S*

удовлетворяет условиям (1.3.1), (1.3.2) и соотношениям (1.3.3).

Пример циркулянта, представленной в виде двумерной матрицы или хордового

кольца для циркулянта {7,1,3} показан на рисунке 1.3.10а и на рисунке 1.3.10б

соответственно.

Рисунок 1.3.10. Пример циркулянта {7,1,3}, изображенной в виде двумерной матрицы (а)

и хордового кольца (б)

1.3.10. Вычислительная система «Максимальный обхват»

Вычислительная система «Максимальный обхват» имеет граф связей с

максимальным обхватом. Построение графа с максимальным обхватом осуществляется

следующим образом. Обхват графа – это длина его простого кратчайшего цикла. Пусть v –

это степень вершины графа, i – номер яруса. Данный вид графов строится по следующим

правилам:

1) произвольно берется начальная вершина;

2) каждая следующая вершина i-го яруса связывается с одной вершиной (i-1)-го

яруса и с (v-1) вершинами яруса (i+1);

3) максимально возможное число вершин i-го яруса равно v(v-1)i-1;

4) выбранный критерий выполняется, быть может за исключением последнего,

если количество вершин на всех ярусах максимально: N=(v(v-1)d-2)/(v-2);

5) свободные связи вершин последнего яруса соединяются между собой либо на

последнем ярусе находится N-(v(v-1)d-1-2)/(v-2) вершин и соединяются свободные ребра

двух последних ярусов. В настоящее время единственный известный способ построения

таких графов – это полный перебор возможных вариантов.

Определение 1.3.10. Структура вычислительной системы типа «Максимальный

обхват» описывается графом GS =(М, S*), где М – множество вычислительных

модулей, определяемых вершинами графа, М ={mi}, i = 0, … , N-1. Построение сети S*

выполняется согласно вышеприведенным пяти правилам.

23

1.3.11. Вычислительные системы со структурой сетей типа «Симметричные

графы»

Для описания межмодульных связей также используют симметричные графы. Их

главное преимущество перед рассмотренными графами заключается в более компактном и

удобном способе их задания.

Пусть V – множество вершин графа, состоящее из N элементов. Они нумеруются

числами 0, 1, …, N-1. Разобьем множество V на s классов эквивалентности. Распределение

вершин по классам осуществляется по следующей формуле:

Vi i ks mod N , i 0, s 1, k 1,2,...

(1.3.4)

Каждому классу Vi поставим в соответствие множество положительных целых

чисел,

M i m[i, k ], k 1, ri

(1.3.5)

ri задает количество ребер вершины класса Vi. При помощи чисел Mi задаются

связи – какие две вершины необходимо соединить ребром:

(1.3.6)

b; b m[i, j]mod N , b V , j 1, ri .

Определение 1.3.11. Структура вычислительной системы типа «Симметричный

граф» описывается симметричным графом GS =(М, S*), где М – множество

вычислительных модулей, , определяемых вершинами графа, М ={mi}, i = 0, … , N-1.

Построение сети S* выполняется согласно вышеприведенным соотношениям (1.3.4),

(1.3.5), (1.3.6).

Например, для N=12, s=3 и М0={1,2,3}, M1={2,4}, M2={5}, тогда классы

определятся как

V0={0,3,6,9}, V1={1,4,7,10}, V2={2,5,8,11}

Множество ребер составят:

(0,1) (3,4) (6,7) (9,10)

(0;2) (3;5) (6;8) (9;11)

(0;3) (3;6) (6;9) (9;0)

(1;3)

(1;5)

(4;6)

(4;8)

(7;9) (10;0)

(7;11) (10;2)

(2;7) (5;10) (8;1) (11;4)

На рисунке 1.3.11. представлена ВС с симметричным графом.

Рисунок 1.3.11. Симметричный граф, N=12, s=3

24

1.3.12. Вычислительные системы с сетью связей типа «Гомоморфные графы»

В качестве сетей связей иногда используют гомоморфные графы, так как процесс

создания ВС хорошо моделируется процессом построения гомоморфных графов.

Пусть дан граф G=(V,E), где V – множество вершин графа, E – множество его

ребер. Выберем во множестве V любые две вершины xi и xj. Построим множество вершин

V1, заменив выбранные вершины xi и xj одной новой вершиной xij. Далее построим

множество ребер E1. Если ребро в E не инцидентно ни одной из вершин xi и xj, то это

ребро просто переносится во множество E1. Если ребро в E инцидентно хотя бы одной из

вершин xi и xj, то ребро в E1 получается из ребра E заменой вершины xi или xj новой

вершиной xij. Говорят, что образованный таким образом граф G1=(V1,E1) получен из

графа G=(V,E) с помощью операции элементарного гомоморфизма. А граф G1 называется

гомоморфным образом графа G. Пример такого преобразования представлен на

рисунке 1.3.12.

xi

xj

xij

Рисунок 1.3.12. Операция элементарного гомоморфизма над графом

Теперь рассмотрим системы, где находят свое применение гомоморфные графы.

При проектировании реальных ВС часто используется блочно-иерархический подход,

заключающийся в декомпозиции объектов и задач с разной степенью детализации их

описания и иерархической подчиненностью этих описаний. Иными словами, на самом

нижнем уровне система представляется совокупностью «базовых» элементов, на

следующем уровне – эти базовые элементы объединяются в более крупные и так далее.

Например, символически это можно представить следующим образом:

ЭВМ платы блоки стойки,

где стрелки показывают процесс усложнения конструкции. При этом один тип

графа межмодульных связей используется для объединения ВМ на плате, а другой тип

графа, вершинам которого соответствуют платы, – для объединения плат в блоки и т.д.

Из практики также известно, что при решении большой задачи активно

взаимодействует только часть машин системы. На основе этих наблюдений можно

разбить систему на части (блоки), внутри которых активно взаимодействующие

вычислительные модули связаны быстродействующим коммутатором, а межблочные

связи – менее быстродействующими коммутаторами, так как обмен данными происходит

не часто. Построенные по такому принципу системы называют блочными. Они являются

примерами систем с гомоморфными графами.

Определение 1.3.16. Структура вычислительной системы типа «Гомоморфный

граф» описывается симметричным графом, определяемых вершинами графа, GS

=(М, S*), где М – множество вычислительных модулей, определяемых вершинами графа,

М ={mi}, i = 0, … , N-1. Связи сети S* соответствуют рёбрам графа, гомоморфному

заданному.

Ниже приведены примеры систем с гомоморфными графами межмодульных

связей.

25

Граф межмодульных связей Tera MTA-1 [13]. Коммуникационная среда этого

суперкомпьютера реализована в виде трехмерного обобщённого тора 2×4×8 и состоит из

64 узлов. Однако узлы имеют всего 4 коммуникационных порта (помимо одного канала

для подключения процессора, или модуля памяти, или процессора ввода-вывода), а не 6,

как требуется для трехмерного тора. Поэтому часть связей прошлось опустить: узлы

имеют связи по координате z и по одной из координат x или y, в зависимости от четности z

(рисунок 1.3.13).

Рисунок 1.3.13. Фрагмент графа межузловых связей

При гомоморфном отображении соседних узлов с четным и нечетным значениями

z можно получить трехмерный тор с меньшим в два раза максимальным значением

координаты z.

Процессор Процессор

+

+

Память

Память

Коммутатор 5х5

...

Коммутатор 5х5

Кольцевой канал

Когерентного

интерфейса SCI

Рисунок 1.3.14. Структура системы SPP 1000

Граф межмодульных связей Convex Exemplar SPP 1000 [14]. Это еще один пример

системы с гомоморфным графом связей, причем здесь наблюдается двойной

гомоморфизм. Рассмотрим подробнее структуру системы SPP 1000 (рисунок 1.3.14).

Во-первых, в данной ВС ВМ компонуется из двух процессоров. Отображение двух

ВМ в одну вершину – это первый гомоморфизм.

Во-вторых, блоки системы для внутренних взаимодействий используют простые

коммутаторы (crossbar) 5×5, которые для этих целей имеют 4 входа и 4 выхода. А пятые

входы и выходы коммутаторов реализуют связь с кольцевым каналом. Этот канал

представляет собой одномерный тор, объединяющий до 16 блоков, и состоящий из 4-х

независимых подканалов («точка-точка»), что обеспечивает наивысшую скорость обмена

26

между блоками и повышает отказоустойчивость канала и системы в целом. Отображение

коммутатора с подключенными к нему ВМ в одну вершину тора – это второй

гомоморфизм.

Структура MBC-100 [15]. Это пример другого построения блочных систем. Здесь

применены следующие архитектурные решения.

Особенностью MBC-100 является разделение информационного обмена и

вычислительных процессов. Первую задачу реализуют транспьютеры (T425 или T805),

вторую – микропроцессоры типа i860. Обеспечивается также достаточный объем

оперативной памяти в каждом ВМ, что позволяет буферизировать поток сообщений и

реализовать асинхронный режим работы ВМ в системе.

В основе построения MBC-100 лежит блочная структура. Структурный модуль

скомпонован из 16 ВМ, связи между которыми имеют матричную организацию

(рисунок 1.3.15).

ВМ

Рисунок 1.3.15. Структурный модуль MBC-100

В матрице 4×4 4 угловых элемента соединяются попарно по диагонали

транспьютерными линками. Благодаря этому максимальная длина пути в структурном

модуле уменьшилась с 6 до 3.

Из оставшихся 12 связей: 4 угловых служат для взаимодействия с внешними

устройствами и 8 – для соединения с другими структурными модулями. Эти связи

позволяют реализовать блочную структуру, то есть объединять структурные модули в

модули следующего уровня. На следующем уровне – базовый вычислительный

модульный блок, состоящий уже из 32-х ВМ (рисунок 1.3.16а). Здесь число свободных

связей равно 16. Следующий уровень – объединение базовых блоков, которое будет

состоять из 64-х ВМ. Здесь число свободных связей тоже равно 16. Дальнейшее

наращивание числа вычислительных модулей можно осуществить, объединяя базовые

блоки через дополнительные транспьютеры – по одному на каждую внешнюю связь

(рисунок 1.3.16б).

27

а)

Дополнительный

транспьютер

Базовый блок

32 ВМ

Базовый блок

32 ВМ

Базовый блок

32 ВМ

Базовый блок

32 ВМ

б)

ВМ

ВМ

Рисунок 1.3.16. Блоки различных уровней MBC-100: а) система из 4-х базовых модулей,

б) схема построения базового блока их 2-х структурных модулей

1.3.13. Вычислительные системы с сетью связей типа «Граф Л(N,v,g)»

Построение графа Л(N,v,g) осуществляется следующим образом: выбирается

некоторый подграф бесконечного планарного графа L(v,g), содержащий N вершин.

Вершины подграфа, имеющие степень меньше, чем v, соединяются рёбрами так, чтобы

степени этих вершин стали равными v. Таким способом из бесконечного планарного

графа L(v,g) можно построить множество графов Л(N,v,g), среди которых выбирается

граф Л(N,v,g) с минимальным числом простых циклов, длина которых отличается от g.

Рассмотрим алгоритм построения бесконечного планарного графа L(v,g) [1,2] более

подробно:

Заданы: степень вершин графа v; обхват графа g; количество ярусов NY, которые

будут построены. Введем переменную NG общего числа вершин графа; матрицу s[i,j]

номеров j-ых вершин на i-ых ярусах графа; матрицу X(i,j) свободных связей j-ых вершин

на i-ых ярусах; матрицу B(i,j) текущих степеней j-ых вершин на i-ых ярусах; матрицу

A(s[i,j], s[p,q]) смежностей вершин; вектор N(i) – число вершин на i-м ярусе. Пусть i –

номер текущего яруса, j – номер текущей вершины на ярусе. Здесь окружность

соответствует ярусу.

1. Исходные значения: обнуляем X(n,m), B(n,m), A(k,k), N(n).

28

2. Выбираем точку на плоскости, представляющую вершину s[0,0] – единственная

вершина нулевого яруса. Полагаем N[0]:=1; NG:=1. s[0,0]:=0.

3. Номер текущего яруса i:=1. Количество вершин на первом ярусе N[1]:=v;

NG:=NG+N[1].

4. Строим первую окружность (ярус) с центром в вершине s[0,0]. Разбиваем ее на v

разных частей v точками. Размещаем в каждой точке вершины s[1,k], k 0, (v 1) . Причем

вершина s[1,k] располагается между s[1,(k-1)mod v] и s[1,(k+1)mod v], то есть вершины

следуют по порядку. Вычисляем s[1,k]:=N[0]+k, k 0, (v 1) .

5. Строим ребра (s[0,0]; s[1,k]), k 0, (v 1) , то есть соединяем центральную

вершину s[0,0] со всеми вершинами первого яруса. Формируем матрицу смежности

A[0,s[1,k]]:=1; A[s[1,k], 0]:=1.

6. Проверяем, построены ли все ярусы: i>NY. Если да, то переходим на шаг 15,

иначе – шаг 7.

7. Вычисляем i:=i+1. Строим i-ю окружность с центром в вершине s[0,0]. Полагаем

j:=0; N[i]:=0.

8. Проверяем, существует ли j-я вершина предыдущего (i-1)-го яруса: j<N[i-1].

Если да, то переходим на шаг 9. Иначе – NG:=NG+N[i] и переход на шаг 15.

9. Вычисляем для вершины s[i-1,j]: степень B[i - 1, j] :

N [ i 1]1

A[ j, f ] ,

количество

f 0

оставшихся свободных связей X[i-1,j] := v - B[i-1,j]. Вычислим количество вершин,

которые необходимо построить на текущем i-ом ярусе: N[i] := N[i] + X[i-1,j].

10. Вычисляем j := j +1. Переход на шаг 8.

11. Разбиваем i-ю окружность N[i] точками на N[i] равных частей. В каждой точке

размещаем вершины s[i,k], k 0, ( N [i ] 1) . Причем вершины следуют по порядку, то есть

s[i,k] располагается между вершинами s[i,(k-1)mod N[i]] и s[i,(k+1)mod N[i]]. Вычисляем

i 1

s[i, k ] : N[ f ] k , k 0, ( N [i ] 1) .

f 0

12. Строим ребра:

s[i 1, j ];

j 1

s[i, xi 1, k ] ,

k 0

s[i 1, j ];

s[i 1, j ];

j 1

s[i, x(i 1, j ) 1 xi 1, k ] ,

k 0

j 1

s[i, 1 xi 1, k ] , ,

k 0

j 0, ( N [i 1] 1)

Формируем матрицу смежности:

j 1

j 1

A s[i 1, j ], s[i, xi 1, k ] : 1, A s[i 1, j ], s[i, 1 xi 1, k ] : 1, ...,

k 0

k 0

j 1

A s[i 1, j ], s[i, x(i 1, j ) 1 xi 1, k ] : 1

и

k 0

j 1

j 1

A s[i, xi 1, k ], s[i 1, j ] : 1, A s[i, 1 xi 1, k ], s[i 1, j ] : 1, ...,

k 0

k 0

j 1

A s[i, x(i 1, j ) 1 xi 1, k ], s[i 1, j ] : 1,

j 0, ( N [i 1] 1)

k 0

13. Если при слиянии двух соседних вершин i-го яруса s[i,k] и s[i,(k+1)mod N[i]],

k 0, ( N [i ] 1) образуется простой цикл длины g, то эти вершины сливаются; количество

вершин i-го яруса уменьшается на 1: N[i] := N[i] – 1. Перенумеровываем вершины.

Если проверены все возможные слияния вершин, то переход на шаг 14. Иначе – на

шаг 13.

29

14. Если при соединении двух соседних вершин i-го яруса

s[i,k] и

s[i,(k+1)mod N[i]], k 0, ( N [i ] 1) ребром (s[i,k]; s[i,(k+1)mod N[i]]) образуется простой

цикл длины g, то такое ребро вводится в граф. Если введены все возможные ребра, то

переходим на шаг 6. Иначе – переход на 14.

15. Конец алгоритма.

Схема данного алгоритма представлена на рисунках 1.3.17 и 1.3.18.

На вход алгоритма (процедура PPG (v,g,NY)) подаются параметры v, g и NY. Алгоритм