РТФ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

advertisement

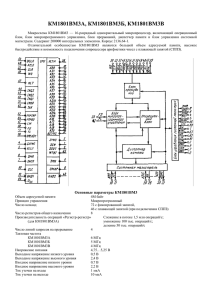

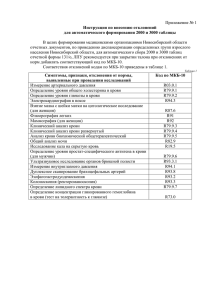

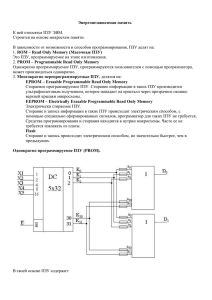

РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ РТФ ЭВМ и периферийные устройства Авторы курса лекций: Хмелевский Игорь Васильевич, канд.техн.наук., доцент кафедры «Автоматика и телемеханика», Шегал Анна Айзиковна, канд.техн.наук., доцент кафедры «Технологии и средства связи» УГТУ-УПИ Екатеринбург 2008 Лекция 19 Однокристальный микроконтроллер семейства MCS-51 : основы организации 4 Цели изучения Рассмотрение функционального состава ядра семейства МК-51. Изучение типовой структуры МК-51. Ознакомление с принципами разделения памяти на программную и данных и изучение их адресных пространств. Рассмотрение регистровой структуры процессора МК. 5 Содержание 1. Функциональный состав МК-51 Технические характеристики выборочного ряда МК семейства MCS-51 2. Описание структуры МК семейства MCS-51 Характеристики центрального процессора МК-51 3. Организация памяти МК-51 Программная память. Память данных. Набор регистров. Булево пространство. 6 Модульный принцип построения семейства микроконтроллеров (МК) MCS -51 Микроконтроллеры MCS-51 являются функционально завершенными однокристальными 8-ми разрядными микроЭВМ гарвардской архитектуры, построенными на основе модульного принципа. Они содержат все необходимые узлы для работы в автономном режиме и предназначены для реализации различных цифровых алгоритмов управления. При этом все МК одного семейства содержат базовый функциональный блок (ядро МК), который одинаков для всех МК семейства, и изменяемый функциональный блок, который отличает различные модели МК в пределах одного семейства. 7 Принципы гарвардовской архитектуры Подразумевается наличие раздельной памяти программ и данных. Если память находится внутри МК, то она называется резидентной . В память программ записывается программа управления МК, которая после отладки не изменяется. Хранить неизменяемый код в ПЗУ значительно дешевле. В современных МК используется либо репрограммируемая память программ либо флэш-память. Дешевые МК используют однократно программируемую память программ. 8 Функциональный состав ядра МК-51 центральный процессор (ЦП); внутренние магистрали адреса, данных и управления; схему формирования многофазной импульсной последовательности для тактирования ЦП и межмодульных магистралей; устройство управления режимами работы МК: активным режимом, режимом пониженного энергопотребления, состоянием сброса, прерывания и др. 9 Технические характеристики выборочного ряда МК семейства MCS-51 10 Структура МК семейства MCS-51 Все микросхемы базового семейства имеют ряд общих узлов. 8-разрядный центральный процессор (ЦП), ориентированный на управление исполнительными устройствами. ЦП имеет встроенную схему 8-разрядного аппаратного умножения и деления чисел. Внутренняя (расположенную на кристалле) память программ масочного или репрограммируемого типа, имеющую для различных кристаллов объем от 4 до 32 Кбайт, в некоторых версиях она отсутствует. Не менее чем 128-байтное резидентное ОЗУ данных, которое используется для организации регистровых банков, стека и хранения пользовательских данных. Не менее 32-х двунаправленных интерфейсных линий (портов), индивидуально настраиваемых на ввод или вывод информации. 11 Не менее двух 16-битных многорежимных счетчика/таймера, используемых для подсчета внешних событий, организации временных задержек и тактирования коммуникационного порта. Двунаправленный дуплексный асинхронный приемопередатчик (UART), предназначенный для организации каналов связи между микроконтроллером и внешними устройствами с широким диапазоном скоростей передачи информации. Имеются средства для аппаратно-программного объединения микроконтроллеров в связанную систему. Двухуровневая приоритетная система прерываний, поддерживающую не менее 5 векторов прерываний от 4-х внутренних и 2-х внешних источников событий. Встроенный тактовый генератор. Структурная схема кристалла 8051 12 Характеристики центрального процессора МК 13 14 Организация памяти МК-51 • • • • Программная память доступна исключительно для чтения (если не применять ее искусственное объединение с памятью данных путем использования внешних цепей). Объем адресуемого пространства может составлять до 64 Кбайт, хотя на различных кристаллах в составе имеется лишь 4, 8, 16 или 32 Кбайт в зависимости от типа микросхемы. Пользователь может расширять память программ установкой внешнего ПЗУ. При считывании команд из внешней программной памяти формируется инверсный сигнал PSEN (Program Store ENable) для всех адресов, кроме области встроенного ПЗУ. Память данных отделена от памяти программ. В этой области возможна адресация до 64 Кбайт внешнего ОЗУ. ЦП генерирует инверсные сигналы чтения RD и записи WR, необходимые для обращения к внешней памяти данных. Внешняя память программ и внешняя память данных могут комбинироваться путем совмещения сигналов RD и PSEN по схеме «логического «И» для получения строба внешней памяти (программ /данных). Организация памяти семейства МК-51 15 Схема сопряжения МК с внешними БИС памяти 16 17 Программная память После сигнала сброса микроконтроллер начнет выполнение программы с адреса 0000h. В нижней части программной памяти располагаются адреса обработчиков прерываний. Если прерывание не используется, то этот адрес доступен, как и остальные. Адреса прерываний расположены с интервалом в 8 байт: 0003h – External Interrupt 0 (внешнее прерывание 0 – вывод INT0); 000Bh – Timer 0 (прерывание от 0-го таймера); 0013h – External Interrupt 1 (внешнее прерывание 1 – вывод INT1); 001Bh – Timer 1 (прерывание от 1-го таймера); 0023h – прерывание от последовательного порта. Младшие 4 Кбайт (8, 16, 32 – для различных модификаций) памяти программ размещаются на кристалле или находятся во внешнем ПЗУ, что определяется переключением вывода ЕА (внешний доступ) соответственно либо к Vcc (напряжению питания), когда используется внутреннее ПЗУ или к Vss (земле) – не используется внутреннее ПЗУ. 18 Программная память После сигнала сброса микроконтроллер начнет выполнение программы с адреса 0000h. В нижней части программной памяти располагаются адреса обработчиков прерываний. Если прерывание не используется, то этот адрес доступен, как и остальные. Адреса прерываний расположены с интервалом в 8 байт: 0003h – External Interrupt 0 (внешнее прерывание 0 – вывод INT0); 000Bh – Timer 0 (прерывание от 0-го таймера); 0013h – External Interrupt 1 (внешнее прерывание 1 – вывод INT1); 001Bh – Timer 1 (прерывание от 1-го таймера); 0023h – прерывание от последовательного порта. Младшие 4 Кбайт (8, 16, 32 – для различных модификаций) памяти программ размещаются на кристалле или находятся во внешнем ПЗУ, что определяется переключением вывода ЕА (внешний доступ) соответственно либо к Vcc (напряжению питания), когда используется внутреннее ПЗУ или к Vss (земле) – не используется внутреннее ПЗУ. 19 Особенность обращения к внешней памяти программ Строб чтения внешнего ПЗУ – PSEN используется во всех обращениях к внешней памяти программ совместно с мультиплексированной шиной адреса/данных внешней памяти. При подключении внешней памяти функцию мультиплексированной шины адреса/данных выполняют линии порта Р0. Фаза выдачи адреса внешней памяти длится 2 такта машинного цикла МК и сопровождается появлением активного уровня сигнала ALE, который применяется для фиксации младшего байта адреса программного счетчика (PCL) на линиях порта Р0 Одновременно на линиях порта Р2 появляется адрес старшего байта программного счетчика (РСН). Адрес в пространстве программной памяти всегда 16разрядный, хотя её объём может быть и меньше 64К. 20 Память данных Микроконтроллер может одновременно использовать два массива памяти данных: внутреннее ОЗУ, расположенное по адресам 00h….7Fh и подключаемое внешнее ОЗУ, или ПЗУ с адресами 0000h….FFFFh. Для управления внешней памятью данных МК генерирует сигналы RD и WR. Архитектура МК51 включает четыре области данных: RSEG – пространство регистров ЦП, DSEG – пространство внутренней памяти данных, BSEG – битовое пространство данных, XSEG – пространство внешней памяти данных/ команд. Пространство регистров и пространство битов совмещаются с пространством DSEG, образуя единую внутреннюю среду для хранения данных, что позволяет рассматривать одни и те же физические данные с разных позиций. Программно доступные регистры процессора 21 8-разрядный аккумулятор – А, выполняющий обычные функции основного арифметического регистра. Регистр В служит расширением аккумулятора А, необходимым для осуществления операций умножения и деления, причем он является как источником, так и приемником операндов Регистр PSW – флаговый, содержит следующие биты: PSW.7 – CY Перенос из старшего разряда АЛУ; PSW.6 – AC Дополнительный перенос из младшей тетрады АЛУ; PSW.5 – FO Флажок пользователя общего назначения; PSW.4, PWS.3 – RS Выбор 1-го из 4-х банков регистров общего назначения; PSW.2 – OV Признак арифметического переполнения результата; PSW.1 – х Не используется; PSW.0 - P Признак четности. 4 банка по 8 рабочих регистров R0 – R7 в каждом.Регистры выполняют общецелевые функции промежуточного хранения данных. Два регистра R0 и R1 каждого банка реализуют также функции 8-разрядных указателей данных. Набор регистров МК51 Использование наборов рабочих регистров позволяет существенно уменьшить длительность переключения контекстов ЦП, что очень важно для МК, работающего в реальном времени. При сбросе МК все регистры устанавливаются в исходное состояние. Программный счетчик РС принимает значение 0000Н, аккумулятор А – 00Н, В – 00Н, PSW – 00H, SP – 07H, DPTR – 0000H. Сброс РС обеспечивает передачу управления по стартовому адресу 0000Н. 22 Назначение регистров управления и адреса МК • • • 23 Шестнадцатиразрядный программный счетчик РС управляет последовательностью выполнения команд, хранящихся в программной памяти объемом до 64 Кбайт. Шестнадцатиразрядный указатель данных DPTR (DPL, DPH) используется в качестве адресного при пересылке констант из памяти программ и доступе к переменным из внешней памяти данных. Указатель стека SP определяет вершину системного стека глубиной до 128 байт. Он содержит адрес последнего байта, занесенного в стек. Стек растёт в сторону увеличения SP. Существует два способа адресации памяти данных МК: прямой (direct) и косвенный (@ Ri, (i = 0, 1)) через регистры R0, R1 выбранного в данный момент времени одного из банков. С введением прямой адресации появились средства прямого доступа в соседние регистровые банки и стек системы, интерпретируемые как обычные ячейки памяти. Микроконтроллер МК51 имеет мощную, развитую подсистему вводавывода (В/В) и средств поддержки режима реального времени. Для их управления в МК предусмотрен ряд регистров, которые размещаются во второй половине прямо адресуемого пространства, образующей пространство специальных регистров – SFR (128 байт). Сюда же включены порты и основные регистры ЦП. Булево пространство • • • 24 Центральный процессор МК51 содержит одноразрядный процессор для вычисления булевых выражений. В основу булевого процессора положен стандартный аккумуляторный принцип организации. Роль аккумулятора выполняет флажок переноса CY. Для хранения булевых данных в архитектуре МК51 предусмотрено специальное одноразрядное линейно упорядоченное пространство BSEG объемом 256 бит, которое физически совмещено с байтовым пространством данных DSEG. При этом первые 128 бит пространства BSEG попадает на обычные ячейки памяти DSEG (20h2Fh). Обычно она используется для хранения булевых переменных. Другая часть пространства BSEG попадает на ячейки памяти, совмещенные со специализированными регистрами МК - SFR, что обеспечивает независимый доступ к их отдельным разрядам. В булевом пространстве определена только прямая адресация bit. Организация внутренней памяти данных 25 26 Выводы 1. Ядро МК-51 включает 8-разрядный процессор (ЦП) с внутренними шинами адреса, данных и управления, схему тактирования ЦП и межмодульных шин, устройство управления режимами работы МК и подсистему прерываний. 2. МК-51 имеет раздельное пространство памяти программ, находящейся на кристалле, емкостью до 32 Кбайт и памяти данных. Это объясняется использованием МК во встроенных системах с неизменяющейся программой управления. 3. Внутренняя память данных физически совмещена с банками регистров общего назначения и битовым пространством. Это способствует оптимизации программирования МК. Имеется возможность подключить к МК внешнюю память до 64 Кбайт. 4. Кристалл МК-51 включает в свой состав не менее 32 линий ввода – вывода, последовательный порт, не менее 2-х 16разрядных таймеров –счетчиков, развитую подсистему векторных прерываний. 27 Информационное обеспечение лекции Литература по теме: Микропроцессорные системы: Учебное пособие для вузов / А.К. Александров, Р.И. Грушвицкий, М.С. Куприянов и др.; Под общ. ред. Д.В. Пузанкова.- СПб: Политехника, 2002. Таненбаум Э. Архитектура компьютера. 5-е издание/ Э. Таненбаум . СПб.: «Питер», 2007.