Тема 4 Средние интегральные схемы

advertisement

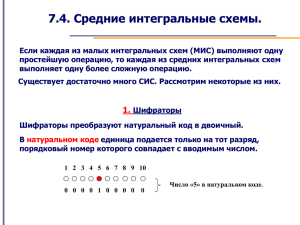

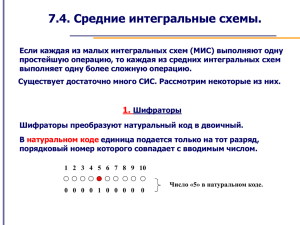

4. Средние интегральные схемы. Если каждая из малых интегральных схем (МИС) выполняют одну простейшую операцию, то каждая из средних интегральных схем выполняет одну более сложную операцию. Существует достаточно много СИС. Рассмотрим некоторые из них. 1. Шифраторы Шифраторы преобразуют натуральный код в двоичный. В натуральном коде единица подается только на тот разряд, порядковый номер которого совпадает с вводимым числом. 1 2 3 4 5 6 7 8 9 10 0 0 0 0 1 0 0 0 0 0 Число «5» в натуральном коде. 4. Средние интегральные схемы. X1 Y1 Y2 X2 X2k P С Yk Рис.4.1. Обозначение шифратора на схемах. «P» − вход стробирования. Шифратор имеет «k» выходов и «2k» входов. На вход стробирования «P» подается «1». Если на входе P = 0, то шифратор прекращает работу. Это делается для того, чтобы не пропустить ошибочный сигнал. Шифраторы обычно стоят на входе цифровых устройств. Входы могут быть соединены с клавиатурой. Все СИС, в том числе шифраторы, конструируются на основе МИС согласно рассмотренному алгоритму (параграф 7.3). 4. Средние интегральные схемы. 2. Дешифраторы Дешифраторы преобразуют двоичный код в натуральный. Они обычно стоят на выходе цифровых устройств. X1 Y1 Y2 X2 Xk P ДС Y2k Рис.4.2. Обозначение дешифратора на схемах. Дешифратор имеет «k» входов и «2k» выходов. Он также может быть снабжен входом стробирования. 4. Средние интегральные схемы. 3. Преобразователи кодов Преобразователи кодов предназначены для преобразования сигнала из одного кода в другой. Например, из двоичного кода в код для управления индикаторами. Xi X Yi Y Рис. 4.3. Обозначение преобразователя кодов. Преобразователь кодов также может быть снабжен входом стробирования. Очень важным является преобразователь из параллельного кода в последовательный, и наоборот. 4. Средние интегральные схемы. В параллельном коде все сигналы одновременно подаются на устройство по многим проводникам. Такая передача производится очень быстро, но требует много проводников. Передача параллельным кодом ведется только в пределах данного устройства или прибора. 4. Средние интегральные схемы. В последовательном коде сигналы передаются по одному проводу последовательно – в виде импульсов тока. Такая передача требует только один проводник, но занимает больше времени. Передача последовательным кодом ведется от одного устройства к другому, в том числе и на большие расстояния. Для преобразования из параллельного кода в последовательный и обратно применяются специальные преобразователи. 4. Средние интегральные схемы. 4. Счетчики Счетчики выполняют задачу подсчета количества единичных импульсов, поступающих с какого-либо устройства. Ответ дается на выходе счетчика в двоичном коде. Y1 Y2 вход S S S R R R а) б) Cч yi Рис. 4.4. a) – схема счетчика на SR- триггерах, б) – обозначение счетчика. Yn1 4. Средние интегральные схемы. Y1 Y2 вход S S S R R R Yn1 Импульсы, поступающие на счетчик, прежде всего проходят через диодно-конденсаторные цепочки. Конденсатор дифференцирует импульсы (рис.4.5-b). a) b) Диод пропускает только отрицательные импульсы в момент прохождения заднего фронта прямоугольных импульсов (рис.4.5-c). c) Рис.4.5. Преобразование импульсов конденсаторно-диодной цепочкой. 4. Средние интегральные схемы. Y1 Y2 вход S S S R R R Yn1 Перед началом работы все триггеры переводятся в такое состояние, что на их верхних выходах – нули. (Счетчик «обнуляют»). Это легко сделать, подав на R-входы единичный импульс. Первый импульс вызывает срабатывание первого триггера по Sвходу. На его выходе – 1. Эта единица (резкое возрастание напряжения) дифференцируется конденсаторами, но положительный импульс не проходит через диоды на второй триггер. Второй импульс вызывает срабатывание первого триггера по Rвходу. На его выходе – 0. Резкое падение напряжения дифференцируется конденсаторами, отрицательный импульс проходит через диоды на второй триггер, он срабатывает по Sвходу. На его выходе – 1, третий триггер не срабатывает. 4. Средние интегральные схемы. Y1 Y2 вход S S S R R R Yn1 Третий импульс вызывает срабатывание первого триггера по Sвходу. На его выходе – 1. Второй и дальнейшие триггеры не срабатывает. Таким образом, первый триггер срабатывает на каждый импульс. Второй триггер срабатывает на каждый второй импульс. Третий – на каждый 4-й. N-й триггер срабатывает на каждый 2N-1-й импульс. 4. Средние интегральные схемы. Y1 Y2 вход S S S R R R На выходе возникает число в двоичном коде (см. табл. 4.1), равное номеру импульса, где Y1 – младший разряд, а Yn-1 – старший. Табл. 4.1. Номер входного импульса 0 1 = 20 2 = 21 3 4 = 22 ... 2n Сигналы на выходах Y1 Y2 Y3 0 1 0 1 0 0 0 1 1 0 0 0 0 0 1 …. …. 0 …. 0 0 ... Yn-1 … … … … … … … 0 0 0 0 0 …. 1 Yn1 4. Средние интегральные схемы. 5. Регистры Регистр – схема, запоминающая на некоторое время сигнал в двоичном коде для его последующего чтения или посылки в другое устройство. Требования к работе регистра. 1. Запись информации производится только по специальному сигналу. 2. Специальная команда «сброс» очищает (обнуляет) все разряды регистра. 3. Информация хранится в регистре сколь угодно долго и может быть подвергнута многократному считыванию. Регистры делятся на параллельные и последовательные. 4. Средние интегральные схемы. Параллельные регистры – воспринимают сигналы в параллельном коде. X1 S & & Y1 R X2 Y2 S & & R X3 Y3 S & & R Запись Сброс Чтение Рис. 4.5. Принципиальная схема трехразрядного параллельного регистра выходы 4. Средние интегральные схемы. X1 S & & Y1 R X2 Y2 S & & R X3 Y3 S & & R Запись Сброс Чтение Начальное состояние – на выходах триггеров «0», на входы Xi подаются сигналы в двоичном коде. При подаче «1» на вход «запись» на нижних входах схем «И» возникает «1» и входные сигналы Xi подаются на Sвходы триггеров. На выходах триггеров возникают соответствующие сигналы. выходы 4. Средние интегральные схемы. X1 S & & Y1 R X2 Y2 S & & выходы R X3 Y3 S & & R Запись Сброс Чтение При подаче «1» на вход «чтение» сигналы с триггеров проходят через схемы «И» на выходы. При этом содержимое триггеров сохраняется! При подаче «1» на вход «сброс» все триггеры переходят в начальное состояние. Содержимое обнуляется. 4. Средние интегральные схемы. Последовательные регистры – воспринимают сигналы в последовательном коде. X S R D S D R S Y R Сдвиг Рис. 4.6. Принципиальная схема трехразрядного последовательного регистра S Значок означает дифференцирующую цепочку R перед входом триггера с запуском триггера задним отрицательным входом импульса. Значок D - линия задержки импульса. 4. Средние интегральные схемы. X S R D S R D S Y R Сдвиг Подача «1» на вход сдвига обнуляет все выходы триггеров. Заполнение регистра осуществляется парами импульсов, подаваемых на вход Х и на вход сдвига. Входной сигнал (1 или 0) Сигнал сдвига (всегда 1) Линия задержки необходима для того, чтобы следующий триггер успел бы придти в устойчивое состояние к моменту прихода сигнала. 4. Средние интегральные схемы. X S R D S R D S Y R Сдвиг Предположим, первой подается «1». Задний фронт импульса переключает первый триггер в состояние «1». Второй триггер не переключается. Сигнал сдвига переключает первый триггер в состояние «0», второй триггер переключается в состояние «1» на выходе. Пусть следующий сигнал «0». Первый и второй триггеры не переключаются. Сигнал сдвига переключает второй триггер в состояние «0», на его выходе отрицательный скачок, третий триггер переключается в состояние «1» на выходе. Пусть следующий сигнал «1». Он будет записан в первый триггер. Тогда сигналы – 101. 4. Средние интегральные схемы. X S R D S R D S Y R Сдвиг Чтение содержимого – последовательная подача «1» на вход сдвига. Тогда содержимое триггеров «выдавливается» вправо и последовательно поступает на выход. Иногда применяют специальные D-триггеры с задержкой. Тогда линия задержки не нужна. 4. Средние интегральные схемы. 6. Компараторы Компараторы предназначены для сравнения двух аналоговых сигналов (двух напряжений U1 и U2). Компараторы имеют два аналоговых входа и один цифровой выход. Если U1 > U2 , то Y = 1. Если U1 < U2 , то Y = 0. Компаратор может быть собран на одном транзисторе, на базу которого подаются оба напряжения с разными знаками. U1 K U2 Рис. 4.7. Компаратор. Y 4. Средние интегральные схемы. Кроме СИС употребляются еще большие интегральные схемы (БИС) и сверхбольшие интегральные схемы (СБИС). Они выполняют достаточно большое количество сложных операций. Другое название СБИС – микропроцессоры. БИС выполняются на основе МИС и СИС. Микропроцессоры выполняются на основе схем с меньшей степенью интеграции.