Программирование на языках описания аппаратуры

advertisement

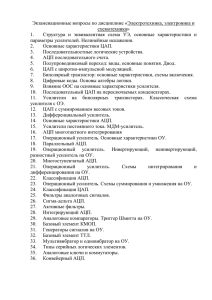

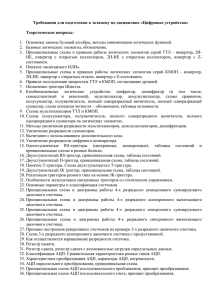

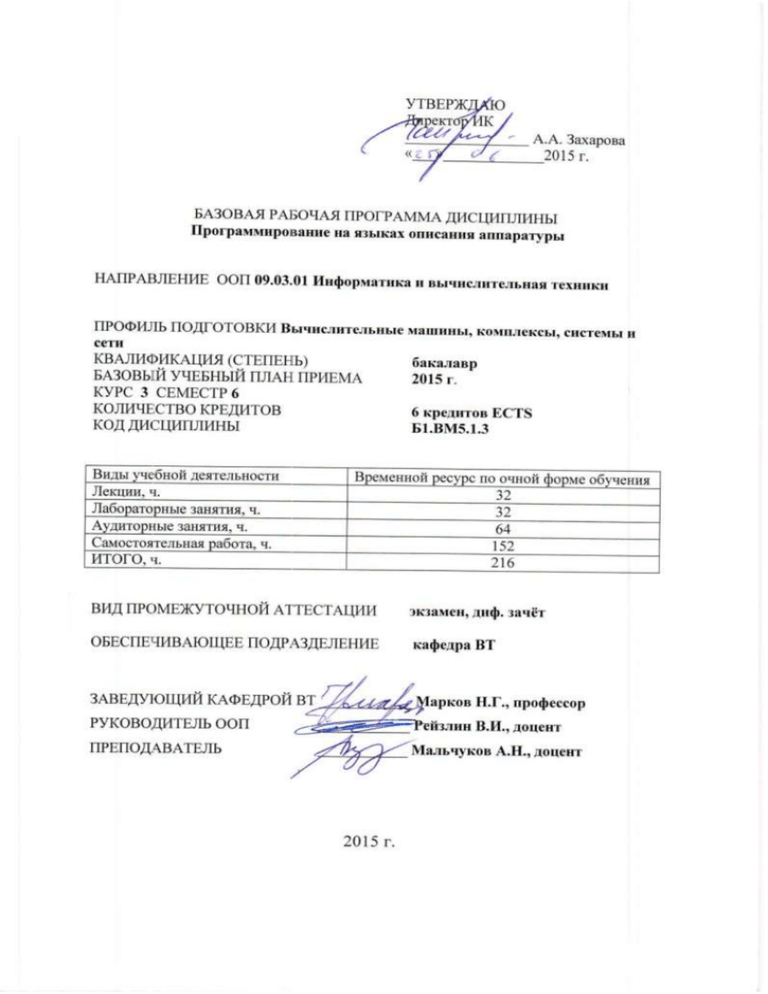

УТВЕРЖДАЮ Директор ИК ________________ А.А. Захарова «___»_____________2015 г. БАЗОВАЯ РАБОЧАЯ ПРОГРАММА ДИСЦИПЛИНЫ Программирование на языках описания аппаратуры НАПРАВЛЕНИЕ ООП 09.03.01 Информатика и вычислительная техники ПРОФИЛЬ ПОДГОТОВКИ Вычислительные машины, комплексы, системы и сети КВАЛИФИКАЦИЯ (СТЕПЕНЬ) бакалавр БАЗОВЫЙ УЧЕБНЫЙ ПЛАН ПРИЕМА 2015 г. КУРС 3 СЕМЕСТР 6 КОЛИЧЕСТВО КРЕДИТОВ 6 кредитов ECTS КОД ДИСЦИПЛИНЫ Б1.ВМ5.1.3 Виды учебной деятельности Лекции, ч. Лабораторные занятия, ч. Аудиторные занятия, ч. Самостоятельная работа, ч. ИТОГО, ч. Временной ресурс по очной форме обучения 32 32 64 152 216 ВИД ПРОМЕЖУТОЧНОЙ АТТЕСТАЦИИ экзамен, диф. зачёт ОБЕСПЕЧИВАЮЩЕЕ ПОДРАЗДЕЛЕНИЕ кафедра ВТ ЗАВЕДУЮЩИЙ КАФЕДРОЙ ВТ ____________ Марков Н.Г., профессор РУКОВОДИТЕЛЬ ООП ____________ Рейзлин В.И., доцент ПРЕПОДАВАТЕЛЬ ____________ Мальчуков А.Н., доцент 2015 г. 1. ЦЕЛИ ОСВОЕНИЯ ДИСЦИПЛИНЫ Целями преподавания дисциплины является усвоение студентами вопросов теории и практики схемотехники с применением современных информационных технологий, современной элементной базы, а также формирование у них мотивации к самообразованию за счёт активизации самостоятельной познавательной деятельности. Поставленные цели полностью соответствуют целям (Ц1-Ц5) ООП. 2.МЕСТО ДИСЦИПЛИНЫ В СТРУКТУРЕ ООП Дисциплина «Программирование на языках описания аппаратуры» (Б1.ВМ5.1.3) является дисциплиной вариативной части блока Б1 вариативного междисциплинарного профессионального модуля (ВМ5) профиля (1) «Вычислительные машины, комплексы, системы и сети». Для успешного усвоения дисциплины «Программирование на языках описания аппаратуры» необходимы знания базовых понятий информатики, форм представления и преобразования информации в компьютере, теории булевых функций и теории графов, основ теории автоматов, методов анализа и синтеза конечных автоматов, методов диагностирования автоматов, принципы построения, параметры и характеристики цифровых и аналоговых элементов ЭВМ, функциональные узлы комбинационного и последовательностного типа; умения применять вычислительную технику для решения практических задач, оперировать элементами алгебры логики, выполнять синтез автоматов, проводить анализ схем управляющих автоматов, ставить и решать схемотехнические задачи, связанные с выбором системы элементов при заданных требованиях и параметрах (временных, мощностных, габаритных и надёжностных). Владеть навыками работы на персональном компьютере, методами выбора элементной базы для построения различных архитектур вычислительных средств. Дисциплине «Программирование на языках описания аппаратуры» предшествует освоение дисциплин (ПРЕРЕКВИЗИТЫ): «Информатика 1.2» (Б1.БМ2.4). «Введение в информационные технологии» (Б1.ВМ4.5). «Электротехника 1.3» (Б1.ВМ3.4). «Электроника 1.3» (Б1.ВМ3.5). «Дискретная математика» (Б1.ВМ4.8). «Схемотехника ЭВМ» (Б1.ВМ4.13). «Теория автоматов» (Б1.ВМ5.1.2). Содержание разделов дисциплины «Программирование на языках описания аппаратуры» согласовано с содержанием дисциплин, изучаемых параллельно (КОРРЕКВИЗИТЫ): «Операционные системы» (Б1.ВМ4.17). В соответствии с требованием ООП освоение модуля направлено на формирование у студентов следующих компетенций (результатов обучения), в т. ч. в соответствии с ФГОС (табл. 1). Таблица 1 Составляющие результатов обучения, которые будут получены при изучении данной дисциплины Результаты обучения (компетенции из ФГОС) Р4 (ОК-7, ОПК-2, 4, ПК- 1, 2) Составляющие результатов обучения Код Умения Код Код Знания З.4.6.1 Принципы построения, параметры и характеристики БИС/СБИС с программируемой структурой и запоминающих устройств, методы автоматизации схемотехнического проектирования. У.4.6. 1 Проектировать устройства на основе СБИС программируемой структуры; строить устройства требуемого объема из микросхем меньшей разрядности и объема; производить проверку работоспособности разработанных схем с помощью моделирования. В.4.6. 1 Владение опытом Владеть навыками схемотехнического проектирования устройств с использованием современной элементной базы, навыками моделирования работоспособности разработанных схем с использованием САПР. В результате освоения дисциплины «Программирование на языках описания аппаратуры (Схемотех-ника ЭВМ. Часть 2)» студентами должны быть достигнуты следующие результаты (табл. 2): Таблица 2 Планируемые результаты освоения дисциплины № п/п РД1 РД2 РД3 РД4 Результат Знать схемотехнику запоминающих устройств, ЦАП и АЦП. Уметь пользоваться справочной научно-технической литературой. Знать методы автоматизации схемотехнического проектирования. Уметь строить ЗУ требуемого объема из микросхем меньшей разрядности и объема. Знать один из языков описания аппаратуры (Verilog, VHDL, AHDL). Уметь проектировать устройства на основе СБИС программируемой структуры, обеспе-чивая требуемые быстродействия, помехоустойчивость и надежность. Знать БИС/СБИС с программируемой структурой. Уметь производить проверку работоспособности разработанных схем с помощью натурного моделирования и моделирования с помощью САПР Quarus II. 4. Структура и содержание дисциплины Раздел 1. Схемотехника запоминающих устройств Классификация микросхем памяти. Запоминающий элемент микросхем динамической памяти. Микросхемы памяти DRAM. Микросхемы синхронной динамической памяти SDRAM. Микросхемы масочных постоянных запоминающих устройств (ПЗУМ – ROM). Микросхемы программируемых и репрограммируемых ПЗУ (ППЗУ – PROM и РПЗУ – EPROM/ РПЗУ-ЭС – EEPROM). Микросхемы флэшпамяти (Flash memory). Микросхемы ферроэлектрической памяти (FeRAM). Раздел 2. Микросхемы цифро-аналоговых и аналого-цифровых преобразователей Классификация ЦАП и АЦП. Схемы и принципы построения преобразователей: однополярные ЦАП с матрицей резисторов двоично-взвешенных номиналов, матрицей R-2R; двуполярные ЦАП; АЦП прямого преобразования, последовательного приближения, двухтактного интегрирования, комбинированного и конвейерного типов. Статические и динамические параметры микросхем ЦАП и АЦП: разрядность, разрешающая способность, характеристика преобразования и т.п. Раздел 3. Микросхемы программируемой логики, базовые матричные кристаллы Общие сведения. Классификация. Программируемые логические матрицы (ПЛМ). Базовые матричные кристаллы (БМК). Программируемые пользователем вентильные матрицы (FPGA). Сложные программируемые логические устройства CPLD и СБИС программируемой логики смешанной архитектуры. СБИС программируемой логики типа “система на кристалле” (SOC).. Перечень лабораторных работ по разделу: 1. Исследование устройства вывода информации на ЖКИ учебнолабораторного комплекса SDK 6.1. 2. Исследование устройства обмена информацией макета SDK 6.1 с ПК через интерфейс RS-232. 3. Исследование устройства обмена информацией макета SDK 6.1 с ПК с помощью матричной клавиатуры. 5. Организация и учебно-методическое обеспечение самостоятельной работы студентов 5.1 Виды и формы самостоятельной работы Самостоятельная работа студентов включает текущую и творческую проблемно-ориентированную самостоятельную работу (ТСР). Текущая СРС направлена на углубление и закрепление знаний студента, развитие практических умений и включает: работу с лекционным материалом; подготовку к лабораторным работам; опережающую самостоятельную работу; изучение тем, вынесенных на самостоятельную проработку; подготовку к экзамену. Творческая самостоятельная работа включает: поиск, анализ научных публикаций; выполнение курсового проекта. 5.2 Контроль самостоятельной работы Оценка результатов самостоятельной работы организуется следующим образом: выполнение и защита лабораторных работ; выполнение курсового проекта и его защита. 6. Средства текущей и промежуточной оценки качества освоения дисциплины Оценка качества освоения дисциплины производится по результатам следующих контролирующих мероприятий: Контролирующие мероприятия Входной контроль Выполнение и защита 2 лабораторных работ Коллоквиум Курсовой проект Экзамен Результаты обучения по дисциплине РД1 – РД4 РД1 – РД2 РД1 – РД4 РД1 – РД4 Для оценки качества освоения дисциплины при проведении контролирующих мероприятий предусмотрены следующие средства: перечень вопросов для коллоквиума; перечень вопросов для экзамена; пример экзаменационного билета. 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. Перечень вопросов для коллоквиума Понятие ЗУ. Требования к идеальному ЗУ. Характеристики МС памяти. Классификация МС памяти. Описание динамических, статических и энергонезависимых ЗЭ. Схема ЗЭ динамической памяти и его работа. Описание работы МС DRAM по структурной схеме, временные диаграммы работы. Глубина адресного пространства. Контроллер памяти. FPM DRAM: описание, временные диаграммы работы в сравнении с DRAM. EDO DRAM: описание, временные диаграммы работы в сравнении с DRAM. Описание BEDO DRAM, EDRAM и CDRAM. Асинхронная динамическая память. Адресация в DRAM. SDR SDRAM: описание, режимы чтения с временными диаграммами, описание работы по структурной схеме. Тайминги. Стандартизированные модули памяти для ПК. DDR SDRAM: описание работы по структурной схеме, временные диаграммы в сравнении с SDR, наглядное описание технологии DDR. DDR2 SDRAM: описание работы по структурной схеме, временные диаграммы работы. DDR3 SDRAM: временные диаграммы работы. Частотный принцип работы SDRAM. Описание DDR4 SDRAM. RDRAM: история развития, характеристики основных этапов, схема подключения планок памяти, достоинства и недостатки технологии. МС статической памяти: схема ЗЭ (n-МОП) и описание её работы, схема ЗЭ (КМОП) и описание её работы. Разновидности SRAM. Охарактеризовать технологии памяти Async SRAM, Sync SRAM, Pipelined SRAM. Привести примеры МС SRAM и их характеристики. МС ROM: описание, схема на биполярных транзисторах и описание её работы, схема на диодах и описание её работы. Характеристики МС ROM. МС PROM: описание, схемы с плавкими перемычками и их описание, схемы с пробойными диодами и их описание, достоинства и недостатки. 18. МС EPROM: описание, ЗЭ МС EPROM и принцип его работы, стирание информации, схема ЗЭ МС EPROM, достоинства и недостатки. 19. МС EEPROM: описание, МНОП-транзистор и описание его работы, достоинства и недостатки. FeRAM: описание, схема ЗЭ и описание его работы в сравнении с DRAM. 20. FLASH-Memory: описание, схема МОП-транзистора с выбирающим затвор и описание его работы в разных режимах. 21. Описание характеристик 3-х поколений FLASH Memory. 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. 21. Перечень вопросов для экзамена Понятие ЗУ. Требования к идеальному ЗУ. Характеристики МС памяти. Классификация МС памяти. Описание динамических, статических и энергонезависимых ЗЭ. Схема ЗЭ динамической памяти и его работа. Описание работы МС DRAM по структурной схеме, временные диаграммы работы. Глубина адресного пространства. Контроллер памяти. FPM DRAM: описание, временные диаграммы работы в сравнении с DRAM. EDO DRAM: описание, временные диаграммы работы в сравнении с DRAM. Описание BEDO DRAM, EDRAM и CDRAM. Асинхронная динамическая память. Адресация в DRAM. SDR SDRAM: описание, режимы чтения с временными диаграммами, описание работы по структурной схеме. Тайминги. Стандартизированные модули памяти для ПК. DDR SDRAM: описание работы по структурной схеме, временные диаграммы в сравнении с SDR, наглядное описание технологии DDR. DDR2 SDRAM: описание работы по структурной схеме, временные диаграммы работы. DDR3 SDRAM: временные диаграммы работы. Частотный принцип работы SDRAM. Описание DDR4 SDRAM. RDRAM: история развития, характеристики основных этапов, схема подключения планок памяти, достоинства и недостатки технологии. МС статической памяти: схема ЗЭ (n-МОП) и описание её работы, схема ЗЭ (КМОП) и описание её работы. Разновидности SRAM. Охарактеризовать технологии памяти Async SRAM, Sync SRAM, Pipelined SRAM. Привести примеры МС SRAM и их характеристики. МС ROM: описание, схема на биполярных транзисторах и описание её работы, схема на диодах и описание её работы. Характеристики МС ROM. МС PROM: описание, схемы с плавкими перемычками и их описание, схемы с пробойными диодами и их описание, достоинства и недостатки. МС EPROM: описание, ЗЭ МС EPROM и принцип его работы, стирание информации, схема ЗЭ МС EPROM, достоинства и недостатки. МС EEPROM: описание, МНОП-транзистор и описание его работы, достоинства и недостатки. FeRAM: описание, схема ЗЭ и описание его работы в сравнении с DRAM. FLASH-Memory: описание, схема МОП-транзистора с выбирающим затвор и описание его работы в разных режимах. Описание характеристик 3-х поколений FLASH Memory. 22. ЦАП: описание, способы формирования выходного сигнала, обобщённая структурная схема, классификация. 23. Схема ЦАП на матрице со взвешенными весами резисторов и описание её работы. 24. Схема на матрице R-2R и описание её работы. 25. Схема ЦАП на матрице конденсаторов и описание её работы, классификация двухполярных ЦАП. 26. Привести схемы двухполярных ЦАП (с двойным источником питания и коммутируемым инвертором) и описание их работы. 27. Параметры МС ЦАП: классификация, описание. 28. АЦП: описание, выходные коды, классификация. 29. Схема параллельного АЦП и описание её работы. 30. Схема SAR АЦП и описание её работы. 31. Схема АЦП с двухтактным интегрированием и описание её работы. 32. Схема комбинированного АЦП и описание её работы. 33. Схема конвейерного АЦП и описание её работы. 34. Параметры МС АЦП: классификация и описание. 35. ПЛИС: история развития, классификация. 36. ПЛМ: описание, схема и описание её работы. 37. ПЛМ: описание задач масштабирования (увеличение количества выходов, термов, входов). 38. ПМЛ: описание, схема и описание её работы. 39. Схемы и описания модификаций ПЛМ и ПМЛ: программируемый выходной буфер, двунаправленный выход, схемы с памятью и с разделяемыми конъюнкторами. 40. БМК: описание, классификация. Канальные БМК: описание, схемы. 41. Бесканальные и блочные БМК: описание, схемы. 42. ППВМ: описание, виды ключей и БЛК. 43. CPLD: описание, архитектура. 44. SoC: описание, пример архитектуры, параметры. Пример экзаменационного билета ЭКЗАМЕНАЦИОННЫЙ БИЛЕТ № 2 1. Схема ЗЭ динамической памяти и его работа. Описание работы МС DRAM по структурной схеме, временные диаграммы работы. Глубина адресного пространства. (10 б.) 2. Охарактеризовать технологии памяти Async SRAM, Sync SRAM, Pipelined SRAM. Привести примеры МС SRAM и их характеристики. (10 б.) 3. Схема ЦАП на матрице конденсаторов и описание её работы, классификация двухполярных ЦАП. (10 б.) 4. ПЛМ: описание задач масштабирования (увеличение количества выходов, термов, входов). (10 б.) 7. Рейтинг качества освоения дисциплины Оценка качества освоения дисциплины в ходе текущей и промежуточной аттестации обучающихся осуществляется в соответствии с «Руководящими материалами по текущему контролю успеваемости, промежуточной и итоговой аттестации студентов Томского политехнического университета», утвержденными приказом ректора № 77/од от 29.11.2011 г. В соответствии с «Календарным планом изучения дисциплины»: текущая аттестация, направленная на оценку качества усвоения теоретического материала (ответы на вопросы коллоквиума) и результатов практической деятельности (выполнение и защита отчетов по лабораторным работам и курсового проекта), производится в течение семестра и оценивается в баллах (максимально 60 баллов), к моменту завершения семестра студент должен защитить все отчёты по лабораторным работам и набрать не менее 33 баллов; по курсовому проекту набрать не менее 22 баллов; промежуточная аттестация (экзамен, защита курсового проекта) производится в конце семестра и так же оценивается в баллах (экзамен максимально 40 баллов, защита курсового проекта – 60), на экзамене студент должен набрать не менее 22 баллов, а на защите курсового проекта не менее 33 баллов. Итоговый рейтинг по дисциплине определяется суммированием баллов, полученных в ходе текущей и промежуточной аттестаций. Максимальный итоговый рейтинг соответствует 100 баллам. 8. Учебно-методическое и информационное обеспечение дисциплины Основная литература: 1. Пухальский, Геннадий Иванович Проектирование цифровых устройств : учебное пособие / Г. И. Пухальский, Т. Я. Новосельцева. — СПб.: Лань, 2012. — 889 с.: ил. + CD-ROM. — Учебники для вузов. Специальная литература. — Библиогр.: с. 871-872. — Предметный указатель: с. 873-878.. — ISBN 978-5-81141265-5. 2. Колесниченко О.В., Аппаратные средства PC / О.В. Колесниченко, И.В. Шишигин, В.Г. Соломенчук. – 6-е изд., перераб. и доп. – СПб.: БХВ-Петербург, 2010 – 800 с. 3. Соловьев, Валерий Васильевич Логическое проектирование цифровых систем на основе программируемых логических интегральных схем / В. В. Соловьев, А. Климович. — Москва: Горячая линия-Телеком, 2008. — 376 с.: ил.. — Библиография в конце глав. — Предметный указатель: с. 361-369.. — ISBN 978-5-99120054-7. 4. Нарышкин, Александр Кириллович Цифровые устройства и микропроцессоры : учебное пособие для вузов / А. К. Нарышкин. — 2-е изд., стер.. — Москва: Академия, 2008. — 318 с.: ил.. — Высшее профессиональное образование. Радиоэлектроника. — Библиография: с. 312-314. — Список сокращений: с. 3-4. — Список условных обозначений: с. 5-7.. — ISBN 978-5-7695-4917-5. Дополнительная литература: 5. Осокин А. Н. Схемотехника. Ч. 2: Учебное пособие. – Томск: Изд-во Томского политехнического университета, 2000 – 144 c. 6. Угрюмов, Евгений Павлович Цифровая схемотехника : учебное пособие / Е. П. Угрюмов. — 2-е изд., перераб. и доп.. — СПб.: БХВ-Петербург, 2007. — 782 с.: ил.. — Учебное пособие. — Библиогр.: с. 761-765. — Предм. указ.: с. 767-782. — Интернет-ресурсы: с. 765-766. — Глоссарий: с. 730-755. — Принятые сокращения: с. 756-760.. — ISBN 978-5-94157-397-4. 7. Стешенко, Владимир Борисович ПЛИС фирмы "ALTERA": элементная база, система проектирования и языки описания аппаратуры / В. Б. Стешенко. — Москва: Додэка-XXI, 2002. — 576 с.. — Мировая электроника. — Библиогр.: с. 572-573.. — ISBN 5-94120-033-1. 8. Антонов, А. П. Язык описания цифровых устройств AlteraHDL : Практический курс / А. П. Антонов. — 2-е изд., стер.. — Москва: РадиоСофт, 2002. — 224 с.: ил. + Прил.:1 CD-ROM. — ISBN 5-93037-052-4. 9. Грушвицкий, Ростислав И. Проектирование систем на микросхемах программируемой структурой / Р. И. Грушвицкий, А. Х. Мурсаев , Е. П. Угрюмов. — 2-е изд.. — СПб.: БХВ-Петербург, 2006. — 736 с.: ил.. — Учебное пособие. — Библиогр.: с. 597-600. — Предметный указатель: с. 601-606.. — ISBN 5-94157-657-9 10. Ульрих Шумахер. Полупроводниковая электроника. http://www.infineon.com/cms/en/product/promopages/Infineon_Russian_Semiconduc tor_Book_/Semiconductor_book_ru.html Internet-ресурсы: 1. Язык описания аппаратуры Verilog HDL http://marsohod.org/index.php/verilog 2. Кафедральный ftp-сервер: ftp://ftp.vt.tpu.ru/study/Malchukov/public/Schem/Курсовой Используемое программное обеспечение: 1. САПР Quartus II. 9. Материально-техническое обеспечение дисциплины Лекционные и практические занятия проводятся в аудиториях с мультимедийным оборудованием. Лабораторные занятия проводятся в компьютерном классе на персональных компьютерах (12 рабочих мест). № п/п 1. 2. 3. Наименование оборудования Мультимедийное оборудование (компьютер, проектор, экран) ПК Intel Core 2 Е6320, 1,86 GHz Макеты SDK-6.1 Корпус, ауд., количество установок 10 корпус ТПУ, 307, 410 ауд. 10 корпус ТПУ, 408 ауд., 8 рабочих мест 10 корпус ТПУ, 408 ауд., 8 шт. Программа составлена на основе Стандарта ООП ТПУ в соответствии с требованиями ФГОС по направлению и профилю подготовки 230100 «Информатика и вычислительная техника», магистерская подготовка. Программа одобрена на заседании кафедры вычислительной техники (протокол № 54 от « 22 » 06 2015 г.). Автор – доцент кафедры вычислительной техники Мальчуков Андрей Николаевич Рецензент – профессор, зав. кафедрой вычислительной техники Марков Николай Григорьевич № Варианта 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 ПРИЛОЖЕНИЕ 1 Количество Язык Интерфейс ввода человек на описания вариант Verilog Блок движковых переключателей и кнопка VHDL 1 AHDL Verilog Матричная клавиатура VHDL 2 AHDL Verilog Последовательный порт RS-232 VHDL 2 AHDL Verilog Матричная клавиатура и блок движковых переVHDL 2 ключателей с кнопкой AHDL Verilog RS-232 и блока движковых переключателей с VHDL 2 кнопкой AHDL Verilog Матричная клавиатура и блок движковых переVHDL 2 ключателей с кнопкой AHDL Verilog RS-232 и блока движковых переключателей с VHDL кнопкой 2 AHDL 22 23 24 25 26 Verilog VHDL AHDL Verilog VHDL 27 AHDL 28 29 30 31 32 Verilog VHDL AHDL Verilog VHDL Матричная клавиатура и блок движковых переключателей с кнопкой RS-232 и блока движковых переключателей с кнопкой Матричная клавиатура и блок движковых переключателей с кнопкой RS-232 и блока движковых переключателей с кнопкой 2 2 2 2 33 AHDL Устройство Калькулятор (выполнение операций над парой чисел: +, –, *, /) Пейджер (вывод полученного / введенного сообщения на экран ЖКИ) кодек ППК (длина блока передаваемых данных равна двум байтам, наличие двукратной ошибки в передающем канале связи, использовать образующий полином 11000011001) Контроллер кодека ECC (длина блока передаваемых данных равна 16 битам, помехоустойчивый код Хемминга с паритетом) цифровые часы с будильником (возможна установка текущего времени и времени срабатывания будильника, включение /отключение будильника, индикация срабатывание будильника)