Содержание отчета

advertisement

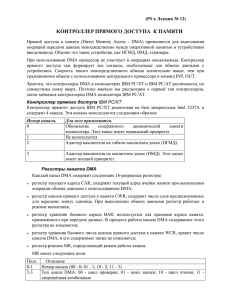

Лабораторная работа № 8 Подсистема прямого доступа к памяти DMA Цель работы: Изучить принципиальную схему и функции сигналов подсистемы прямого доступа к памяти DMA. Порядок выполнения работы 1) Изучить рисунки 1 и 2 ( Рисунок 1 и Рисунок 2 - Принципиальная схема подсистемы прямого доступа к памяти DMA). 2) Определить функциональное назначение основных сигналов подсистемы прямого доступа к памяти DMA. 3) Используя шаблоны, построить принципиальную схему подсистемы прямого доступа к памяти DMA. 4) Оформить отчет. Основные сведения о подсистеме прямого доступа к памяти DMA На рисунках 1 и 2 представлена принципиальная схема подсистемы прямого доступа к памяти DMA. В ее состав входят два контроллера DMA типа 8237, два регистра адреса и память страниц DMA. Контроллеры DMA каскадируются по каналу 4. Первый контроллер DMA (верхний на листе 14) работает только с 8-разрядными устройствами, а второй – только с 16-разрядными устройствами. Во время цикла DMA контроллер выдает разряды адреса с 8 по 15 (второй контроллер выдает разряды с 9 по 16) на шину XD и они сохраняются на регистре, разряды с 0 по 7 (с 1 по 8 для второго контроллера) 8237 выдает непосредственно на шину XA. Старшие разряды адреса считываются из памяти страниц. При передаче из памяти в порт контроллер DMA выдает сигнал –DMAMEMR, который проходит через специальную схему и активизирует сигнал –MEMR. Эта схема задерживает начало выполнения команды на половину такта DMA, чтобы обеспечить достаточное время на дешифрацию адреса. Содержание отчета 1) Цель работы 2) Принципиальная схема подсистемы прямого доступа к памяти DMA 3) Назначение основных сигналов подсистемы прямого доступа к памяти DMA Тестовые вопросы 1) Выходные сигналы, которые являются признаками подтверждения обслуживания запроса на прямой доступ к памяти. а) DASK0- DASK7 b)IRQ7-IRQ15 с) SA0-SA7 d) SD0-SD7 2) Выходной сигнал в высоком состоянии указывает, что выполняется последний цикл обмена по процедуре, на которую был запрограммирован контроллер ПДП. а) T/C b)CS с) GND d) DCS 3) Сигнал VCC а) прерывание b)питание с) сигнал ошибки d) сигнал записи 4) Низкий уровень на этой двунаправленной линии означает, что следует записать данные с ШД а) MEMR b) MEMW с) MD d) WE 5) Входные сигналы используются для передачи запроса на обслуживание контроллером прямого доступа к памяти или запроса на захват шины процессора а) DASK0- DASK7 b)IRQ7-IRQ15 с) DRQ0- DRQ7 d) SD0-SD7 6) Сигнал RESET а) сброс b) подключение к системной шине с) чтение 7) Сигнал HLDA а) младший разряд адреса b) подтверждение захвата шины 8) Сигнал CE а) выбор кристалла d) сигнал готовности с) ошибка d) запись b) вход управления с) разрешение выходов d) чтение в порт Рисунок 1 - Принципиальная схема подсистемы прямого доступа к памяти DMA Рисунок 2 - Принципиальная схема подсистемы прямого доступа к памяти DMA Шаблоны: