МОДУЛЯТОР ПРОМЕЖУТОЧНОЙ ЧАСТОТЫ Мамедов Л.К

advertisement

МОДУЛЯТОР ПРОМЕЖУТОЧНОЙ ЧАСТОТЫ

Мамедов Л.К., главный конструктор ОАО НИИ «САПФИР»

Модулятор в радиотехнике, устройство, осуществляющее модуляцию —

управление

параметрами

соответствии

с

высокочастотного

электрическими

переносчика

сигналами

информации

передаваемого

в

сообщения.

Переносчиком информации обычно служат гармонические колебания или

волны с частотой (несущей или поднесущей) ~ 104—1015 Гц. В зависимости от

того, какой параметр колебаний или волн изменяется, различают амплитудную,

частотную, фазовую или смешанную (при однополосной передаче) модуляцию

колебаний. Часто в функцию модуляции входит усиление модулирующих

колебаний. Непременное требование к модуляции состоит в том, что

модулирующее

колебание

должно

изменяться

во

времени

медленнее

модулируемого. Поэтому в любом модуляторе сочетаются взаимодействующие

цепи модулируемых колебаний или волн с цепями модулирующего сигнала

более низкой частоты.

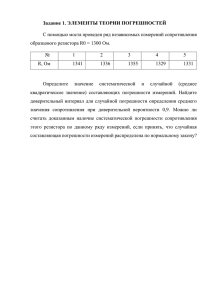

Задача, поставленная перед нами, состояла в том, чтобы разработать

схему модулятора промежуточной частоты со следующими характеристиками:

Частота сигнала на входе равна 21.4МГц, уровнем от 1 мкВ до 1 В;

Сигнал на выходе модулятора ПЧ частотой 2.25МГц уровнем в

пределах от 0.95 до 1.00 В;

Постоянная

времени

срабатывания

автоматической

регулировки

уровня выходного сигнала должна находиться в пределах от 30 до 40 мкс.

Обмен данными с модулятором по промышленному интерфейсу RS485/RS-422;

Частота обработки сигнала не менее 150 МГц;

Напряжение питания модулятора + 24 В;

Потребляемая мощность в активном режиме работы не более 24 Вт;

Модулятор ПЧ должен обеспечивать устойчивую круглосуточную

работу при изменении температуры среды от -40 до + 500 С;

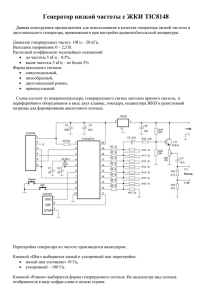

Учитывая изложенные требования в качестве управляющего устройства,

используем DSP процессор, т.к. микроконтроллеры не обеспечивают тактовую

частоту 150 МГц и обработку сигнала – фильтрацию по низкой частоте.

Многократная запись/стирание (корректировки) программы в процессоре

осуществляется с помощью электрически перезаписываемой памяти. Для

управления постоянной времени срабатывания в схему включен усилитель с

программируемым коэффициентом усиления. Функцию преобразования сигнала

высокой частоты с усилителя в цифровой для обработки в DSP процессоре

осуществляет цифровой приемник. Цифровой приемник должен управлять

коэффициентами деления синтезаторов. На синтезаторах формируется частота,

разница с высокой частотой от генератора высокочастотного сигнала и будет

формировать

промежуточную

частоту.

Для

преобразования

цифровой

последовательности в аналоговый сигнал на выходе модулятора в схему

включен цифроаналоговый преобразователь. Структурная схема модулятора

промежуточной частоты представлена на рис. 1.

На российском рынке элементов наиболее распространены цифровые

сигнальные

процессоры

компаний

ANALOG

DEVICES

и

TEXAS

INSTRUMENTS. При выборе процессора учитывались параметры, наличие

русскоязычной документации, поставка Demo версии для изучения среды

программирования и возможность написания программы как на языке низкого

(аппаратного) Assembler, так и на языке высокого С++ уровня.

Рассматривая множество процессоров, представленных на сайтах этих

компаний, выбор (не в последнюю очередь за счет наличия полного описания

процессора и высокого уровня оказываемых технических консультаций

представителями компании) был сделан в пользу ADSP2191M семейства ADSP2100 фирмы ANALOG DEVICES.

Цифровые сигнальные процессоры семейства ADSP-2191M – это

высокопроизводительные 16-разрядные процессоры, предназначенные для

2

использования в системах связи, измерительных приборах, в системах

обработки речи и т.д.. Ядро этих процессоров совместимо с ядром процессоров

семейства ADSP-2100, но имеет ряд дополнительных функций.

Ãåí åðàò î ð

âûñî êî ÷àñò î ò í î ãî ñèãí àëà

EEPROM

Î ï î ðí ûé

ñèãí àë

DSP

ï ðî öåññî ð

Öèô ðî âî é

ï î ò åí öèî ì åò ð

óñèëèò åëü

Öèô ðî âî é

ï ðèåì í èê

ÖÀÏ

óñèëèò åëü

Ñèí ò åçàò î ð 1

óñèëèò åëü

Ñèí ò åçàò î ð 2

Î ï î ðí ûé

ñèãí àë

Рис. 1. Структурная схема модулятора промежуточной частоты

Вместе с ядром ADSP-2191 на кристалл добавлены периферийные

устройства, то есть формируется целостная “система-на-кристалле”. К ним

относятся: статическая оперативная память (Static Random-Access Memory –

SRAM или СОЗУ), интегрированные периферийные устройства ввода-ввывода

(Input/Output – I/O), таймер и контроллер прерываний. Характеристики

процессора ADSP2191M приведены на сайте www.analog.com.

Основными параметрами памяти (EEPROM) является объем и количество

циклов записи/стирания. Учитывая эти критерии и наличие последовательного

периферийного порта, выбор остановлен на EEPROM компании Atmel. Загрузка

процессора происходит

в начальный момент при запуске по SPI порту.

Тактируется процессор частотой 10МГц, с последующим умножением внутри

процессора частоты PLL в 15 раз, переключатель SA1 – определяет

коэффициент умножения. В качестве цифрового потенциометра для управления

уровнем

сигнала

последовательного

высокой

частоты

периферийного

выбор

порта,

основывался

по

которому

на

наличии

изменяется

сопротивление микросхемы. Учитывая эти требования, выбор остановлен на

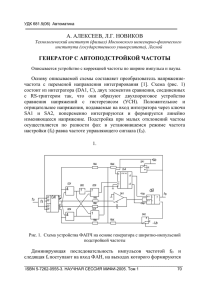

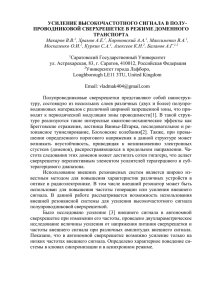

одноканальном 256 позиционном резисторе. Функциональная схема цифрового

3

потенциометра и зависимость сопротивления потенциометра от цифрового кода

приведена на рис. 2.

Рис. 2. Функциональная схема и зависимость изменения сопротивления

потенциометра AD5260 от цифрового кода.

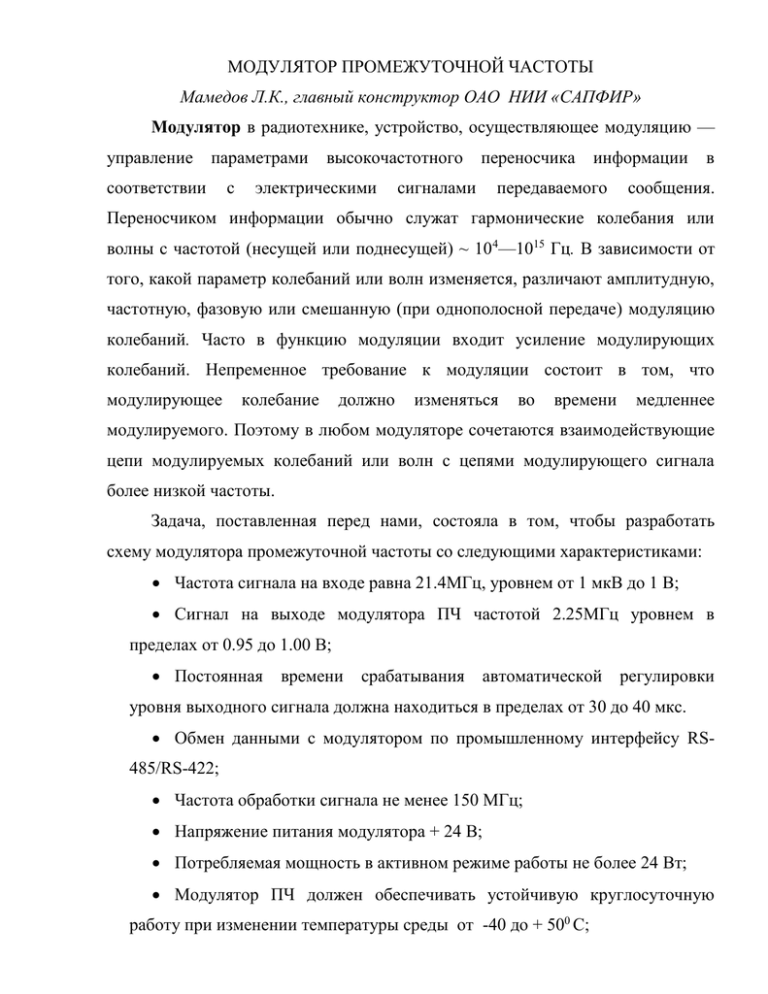

Выбор операционного СМС3300790

усилителя

осуществлялся

по

уровню

шумов, вносимых в сигнал. Сигнал с его

выхода поступает на вход микросхемы

усилителя высокой частоты с диапазоном

усиления в канале от 0 до +48 dB

(предварительное усиление равно +14 dB).

В соответствии с этим требованием,

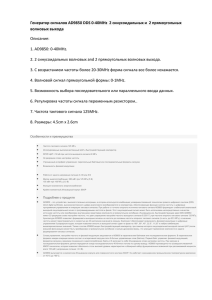

Рис. 3. Зависимость

VGN от напряжения

управления.

а

также

с

учетом

низкой

шумовой

характеристики была выбрана микросхема

AD604AR,

представляющая

собой

двухканальный усилитель с управляемым коэффициентом усиления.

Зависимость коэффициента усиления (VGN) AD604 от напряжения,

поданного на управляющий вход, показана на рис.3.

Контроль питающего напряжения +3.3В осуществляет микросхема

ADM708SAR. При снижении уровня питающего напряжения, на выводе RESET

формируется уровень нуля в течении 200 мсек. Этот сигнал можно также

4

сформировать подачей «низкого» сигнала на вывод MR - ручного управления.

Для сопряжения модулятора с внешними устройствами по интерфейсу RSприменена

485/RS-422

дифференциальный

микросхема

приемопередатчик,

ADM3491,

представляющая

выполняющий

функции

сбалансированной передачи/приема данных в EIA стандарте.

С генератора высокой частоты в схему поступает сигнал частотой 21.4МГц

уровнем от 1мкВ до 1В. В узле преобразования аналогового сигнала в

цифровую

последовательность

использована

микросхема

AD9874,

характеристики которой наиболее подходят для реализации поставленной для

этого узла задачи.

AD9874 предназначенна для оцифровки сигнала промежуточной частоты

низкого уровня в диапазоне от 10 до 300 МГц с шириной спектра до 270 кГц

(рис.4). Сигнальная цепь AD9874 состоит из малошумящего усилителя,

смесителя, широкополосного сигма-дельта АЦП и фильтра с программируемым

коэффициентом децимации. Схема автоматического контроля коэффициента

усиления (AGC, АРУ) обеспечивает в AD9874 непрерывное изменение

коэфициента усиления на 12 дБ. Высокий динамический диапазон и эффект

анти-наложения,

обеспечиваемый

широкополосным

сигма-дельта

АЦП

позволяет AD9874 работать с блокированными сигналами на 80 дБ

превышающими

полезный

сигнал.

Вспомогательные

блоки

включают

синтезаторы LO и тактовой частоты, а также последовательный интерфейс

порта (SPI), который позволяет получить доступ ко всем регистрам,

конфигурирующим внутренние параметры устройства.

Синтезатор LO (Рис. 5) представляет собой программируемый PLL,

имеющий разрешение 6,25 kHz при частоте входного сигнала до 300 МГЦ и

частоте опорного сигнала до 25 МГЦ. Он состоит из малошумящего цифрового

фазо-частотного детектора (PFD), источника тока с переменным выходным

током (CP), 14- битовый делитель опорного сигнала, программируемых A и B

5

счетчиков и двухмодульного предделителя частоты с коэффициентом 8/9. 3разрядный А и 13-разрядный В счетчики вместе с предделителем частоты 8/9

образуют N делитель, где N = 8 x B + A. Кроме того, 14-разрядный счетчик

опорного сигнала (R-счетчик), обеспечивает избирательные входные опорные

частоты fREF, на входе PFD. Замкнутая система стабилизации частоты (PLL)

может быть реализована, если синтезатор используется с внешним фильтром и

ГУНом (VCO). В схеме использованы генераторы, управляемые напряжением

JTOS-25 компании MINI-CIRCUITS, частотой 25МГц.

A, B, и R счетчики программируются через регистры LOA, LOB, и LOR.

Выходной ток источника тока определяются регистром LOI в диапазоне от

0.625 mA до 5.0 mA.

Рис. 5. LO синтезатор AD9874

Рис. 4. Функциональная схема

микросхемы AD9874.

Синтезаторы LO (и CLK) работает следующим образом. Сигнал внешней

опорной частоты fref, заносится в буфер и делится на значение, установленное в

счетчике R. Внутренняя опорная частота fref - сравнивается с поделенной

частотой ГУНа fLO. Фазо-частотный детектор выдает импульсы UP/DOWN,

длительность которых зависит от разности фаз и частот входных сигналов.

UP/DOWN импульсы управляют источником тока заряжающим внешний

фильтр, когда имеется несоответствие между входами детектора. Выход

фильтра питает внешний ГУН, выходная частота fLO, после деления

соответствует опорной частоте fref, что приводит к замыканию цепи обратной

6

связи.

Подпрограмма

инициализации

микросхемы

AD9874

по

последовательному интерфейсу SPI1, реализованная в процессоре ADSP2191M

имеет вид:

unsigned short int ad9874_init[38]={

void transfer_ad9874()

////// 1D-1C REGISTERS ////////////////////

{

0x00ff, 0x3a02, 0x3c0f, 0x3e80, 0x3800, 0x0000,

sysreg_write(sysreg_IOPG, SPI1_Controller_Page);

////// 01-07 REGISTERS ////////////////////

for (int temp1=0; temp1<=37; temp1++) {

0x02f0, 0x0400, 0x0680, 0x0800, 0x0a00, 0x0c83, 0x0e07

io_space_write(TDBR1,ad9874_init[temp1]);

////// 08-0E REGISTERS ////////////////////

wait_spi:

0x1000, 0x12c8, 0x14e0, 0x162f, 0x1803, 0x1a00, 0x1c20,

if((io_space_read(SPIST1)&0x08)!=0)

////// 10-16 REGISTERS ////////////////////

goto wait_spi;

0x2000, 0x22c8, 0x2401, 0x2668, 0x2803, 0x2a00, 0x2c20,

};

////// 18-1A REGISTERS ////////////////////

return;

0x3040, 0x3205, 0x3405

};

////// 37-3E REGISTERS ////////////////////

0x6e00, 0x7000, 0x7200, 0x7400, 0x7600, 0x7800,0x7a00,

0x7c00

};

В качестве выходного узла схемы преобразования цифрового кода в

аналоговый сигнал был выбран кодек, поддерживающий последовательный

порт SPORT. По этому порту передаются данные после обработки в

процессоре. Наиболее удовлетворяющие по функциональному назначению

узла: преобразование цифра-аналог, поддержка последовательного порта,

возможность программного изменения скорости и фильтрации, является

AD1819BJST – звуковой кодек. Включение кодека осуществляется подачей

сигнала высокого уровня на RESET, формируемого на выводе PF10 (флаг)

процессора:

sysreg_write(sysreg_IOPG, General_Purpose_IO);

io_space_write(FLAGS, 0x1400);

Кодограмма (формат АС`97) включает в себя бит разрешения 16 слотов, регистр

адреса последовательной конфигурации и данные, передаваемые в оба канала

(левый и правый) через последовательный порт

SPORT0 процессора

ADSP2191M. Ниже приведена подпрограмма инициализации кодека на языке

ассемблер:

7

/* AD1819 Codec Register Address Definitions */

#define REGS_RESET 0x0000

#define MASTER_VOLUME 0x0200

#define MASTER_VOLUME_MONO 0x0600

#define PC_BEEP_Volume 0x0A00

CD_Volume, 0x8808,

#define PHONE_Volume 0x0C00

VIDEO_Volume, 0x8808,

#define MIC_Volume 0x0E00

AUX_Volume, 0x8808,

#define LINE_IN_Volume 0x1000

PCM_OUT_Volume, 0x0808,

#define CD_Volume 0x1200

RECORD_SELECT, 0x0404,

#define VIDEO_Volume 0x1400

RECORD_GAIN, 0x0F0F,

#define AUX_Volume 0x1600

GENERAL_PURPOSE, 0x8000,

#define PCM_OUT_Volume 0x1800

THREE_D_CONTROL_REG, 0x0000,

#define RECORD_SELECT 0x1A00

MISC_CONTROL_BITS, 0x0000,

#define RECORD_GAIN 0x1C00

SAMPLE_RATE_GENERATE_0,0xBB80,

#define GENERAL_PURPOSE 0x2000

SAPLE_RATE_GENERATE_1, 0xBB80;

#define THREE_D_CONTROL_REG 0x2200

Initialize_1819_Registers:

#define SERIAL_CONFIGURATION 0x7400

I4 = Init_Codec_Registers;

#define MISC_CONTROL_BITS 0x7600

/* указатель на команды инициализации кодека */

#define SAMPLE_RATE_GENERATE_0 0x7800

r15 = ENABLE_Vfbit_SLOT1_SLOT2;

#define SAMPLE_RATE_GENERATE_1 0x7A00

LCNTR = 17, DO Codec_Init UNTIL LCE;

#define ENABLE_Vfbit_SLOT1_SLOT2

0xE000

dm(tx_buf + TAG_PHASE) = r15

#define TAG_PHASE

0

r1 = dm(I4, 1);

#define COMMAND_ADDRESS_SLOT 1

/* взятие следующего адреса регистра кодека */

#define COMMAND_DATA_SLOT

dm(tx_buf + COMMAND_ADDRESS_SLOT) = r1;

2

/* выдача адреса регистра кодека в слот1 */

.var Init_Codec_Registers[34] =

MASTER_VOLUME, 0x0000,

r1 = dm(I4, 1);

MASTER_VOLUME_MONO, 0x8000,

dm(tx_buf + COMMAND_DATA_SLOT) = r1;

PC_BEEP_Volume, 0x8000,

Codec_Init: idle;

PHONE_Volume, 0x8008,

MIC_Volume, 0x8008,

LINE_IN_Volume, 0x0000,

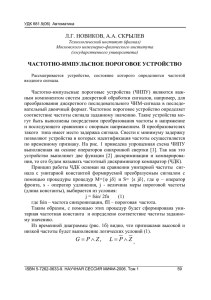

На рис.6 представлена схема модулятора промежуточной частоты.

Конструкция платы

Все

функциональные

узлы

модулятора

промежуточной

частоты

выполнены на печатной плате типоразмера 3U. Элементы ВЧ схемы размещены

на печатной плате, экранированной и закрытой крышками.

ЛИТЕРАТУРА:

1. Информация с сайта Analog Devices www.analog.com.

2. AT25256-10PI. Информация с сайта Atmel www.atmel.ru.

3. MC33079D. Информация с сайта MOTOROLA www.motorola.com

4. Модули питания NVS0.4. Информация с сайта www.power-one.com

8

5. ГУН JTOS-25. Информация с сайта www.minicircuits.com

9

D1

40

73

68

69

+3,3 V

R1 10 ê

R2 10 ê

+2,5.V

+3,3.V

61

70

BMODE0

71

BMODE1

83

OPMODE

72

BYPASS

19

V_INT

58

82

127

13

V_EXT

25

40

63

90

100

118

131

143

65

66

67

56

57

59

60

61

62

64

65

66

67

68

69

55

56

57

58

59

60

46

47

48

49

50

51

62

63

128

RESET

132

CLKIN

133

XTAL

130

CLKOUT

DT0

TCLK0

TFS0

DR0

RCLK0

RFS0

DT1

TCLK1

TFS1

DR1

RCLK1

RFS1

DT2/ MISO0

TCLK2/ SCK0

TFS2/ MOSI0

DR2/ MISO1

RCLK2/ SCK1

RES2/ MOSI1

43

TMR0

44

TMR1

45

TMR2

23

22

21

20

18

17

15

14

12

11

10

9

8

7

6

4

3

24

27

28

30

31

32

26

HA16

HAD15

HAD14

HAD13

HAD12

HAD11

HAD10

HAD9

HAD8

HAD7

HAD6

HAD5

HAD4

HAD3

HAD2

HAD1

HAD0

HACK_P

HCMS

HCIOMS

HALE

HRD

HWR

HACK

DSPROC

A21

A20

A19

A18

A17

A16

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

D15/ PF15

D14/ PF14

D13/ PF13

D12/ PF12

D11/ PF11

D10/ PF10

D9/ PF9

D8/ PF8

D7

D6

D5

D4

D3

D2

D1

D0

DF/ PF7

MSEL6/ PF6

MSEL5/ PF5

MSEL4/ PF4

MSEL3/ PF3

MSEL/ PF2

MSEL1/ PF1

MSEL0/ PF0

RD

WR

MS0

MS1

MS2

MS3

IOMS

BMS

ACK

BR

BG

BGH

TD0

TD1

TMS

TCK

TRSK

EMU

GND

C2 22 ï

4

+3,3.V

Gn

MR

3

37

2

36

UDSP

+3,3.V

2

VCC

3

GND

PF0

-

34

4

5

33

3

6

18

17

16

15

14

13

12

11

32

2

7

31

1

8

8

VCC

4

GND

122

121

115

116

117

119

114

113

120

112

111

110

24

25

26

1

8

32

2

3

7

6

31

4

5

3

7

2

8

1

VDD

A

W

VL

B

VSS

GND

SDO

D/ A

5

SHDH

9

PR

13

R4 10 ê

NC

4

1

2

12

3

11

10

14

263

262 264

265

260 266

C19 10 ì ê

C20 100 ê

C21 47 ê

D4

Rx

15

A

14

B

11

Y

12

Z

8

RO

DI

DE

263

C23 270

264

3

19

C24 1 ì ê

265

6

20

C25 1 ì ê

266

5

54

RE

GND

C22 270

1

+3,3V

C4

C5

C6

C7

C8

C9

C10

C15 10 ì ê

C28 0,1 ì ê

C16 10 ì ê

C29 0,1 ì ê

+3,3V

Ñ3...Ñ12 - Êî í äåí ñàò î ð Ñ0805C104K5RAC KEMET

D7

3

C13 10 ì ê

1

IN

* STU

OUT

2

CD_L

CD_R

CD_GND

23

24

62

61

63

128

R14 10 ê

21

22

14

15

16

17

18

20

19

12

PC

13

PH_IN

LN_OUT_L

LN_OUT_R

MONO_OUT

35

36

37

134

135

D1 - Ì èêðî ñõåì à ADSP- 2191MBST- 140AD

D2 - Í àáî ð ðåçèñò î ðî â CAY16- 103J4 BOURNS

D3 - Ì èêðî ñõåì à AD5260BRU20 AD

D4 - Ì èêðî ñõåì à ADM3491ARU AD

D5 - Ì èêðî ñõåì à MC33079D MOTOROLA

D6 - Í àáî ð ðåçèñò î ðî â CAY16- 103J4 BOURNS

D7 - Ì èêðî ñõåì à ADP3338AKC- 3.3 AD

D8 - Ì èêðî ñõåì à ADP3338AKC- 2.5 AD

D9 - Ì èêðî ñõåì à ADM708SAR AD

D10 - Ì èêðî ñõåì à AT25256- 10PI- 2.7 ATMEL

D11 - Ì èêðî ñõåì à AD1819BJST AD

BQ1 - Ðåçî í àò î ð Q 10.0- MG3A- 30- 50/ 50- FU- T1 JAUCH QUARTZ

+5.V

+5.V

VIDEO_L

VIDEO_R

25

AVCC1

38

AVCC2

26

AGND1

42

AGND2

C11

C12

AUX_L

AUX_R

1

DVCC1

9

DVCC2

4

DGND1

7

DGND2

+5.V

VCC

MIC1

MIC2

29

AFILT1

30

AFILT2

31

FILT_R

32

FILT_L

C27 100 ê

261

8

D_IN

5

D_OUT

6

S_CLK

10

SYNC

LN_IN_L

LN_IN_R

27

REF

28

REF_OUT

33

RX3D

34

CX3D

261

262

BQ2

221

3,3 V

AUD CD

2

XTL_IN

3

XTL_OUT

+3,3V

+3,3V

RESET

45

CS0

46

CS1

47

CH_IN

48

CH_CLK

260

7

SDI

6

CLK

8

CS

C18 22 ï

C3

19

20

4

6

C17 22 ï

4

+3,3V

R8 10 ê

54

5

D3

Rx

Tx

Tx

R3 10 ê

R11 10 ê

53

11

D6

+5 V

R10 10 ê

R7 10 ê

52

+3,3 V

D11

R6 10 ê

60

51

33

48

R9 10 ê

59

D2

34

60

59

51

56

57

55

43

6

SCK

5

SI

2

SO

1

CS

EPROM

+3,3 V

54

53

41

52

48

51

5

C26 0,1 ì ê

SA1

23

22

21

7

HOLD

3

WP

R13 10 ê

4

+V

11

-V

+15V_DA

- 15V_DA

35

40

7

RST

D10

1

+

8

RST

PFI

D5

221

38

38

37

36

35

34

33

32

31

5

16

29

33

54

55

77

80

94

105

129

134

R12 10 ê

R5 100 ê

69

42

41

39

38

37

36

35

34

74

75

76

78

79

81

1

BQ1

2

1

144

142

141

140

139

138

137

136

135

128

126

125

124

123

52

RXD

53

TXD

D9

C1 22 ï

68

109

108

107

106

104

103

102

101

99

98

97

96

95

93

92

91

89

88

87

86

85

84

BQ2 - Ðåçî í àò î ð Q 24.576- MG3A- 30- 50/ 50- FU- T1 JAUCH QUARTZ

SA1 - Ï åðåêëþ÷àò åëü DHS- 04SR APEM

+3,3 V

C30 10 ì ê

GND

D8

+5.V

3

C14 10 ì ê

1

IN

GND

* STU

OUT

2

+2,5 V

C31 10 ì ê

C32

C33

C34

C35

Ñ32...Ñ35 - Êî í äåí ñàò î ð Ñ0805C104K5RAC KEMET

Рис. 6. Принципиальная электрическая схема модулятора промежуточной частоты (лист 1 из 3)

10

L2

C3 0,1 ì ê

+15V

C41 10 ì ê

L6

C40 10 ì ê

L5

- 5V

+5V

Z3

Z2

Z4

C6 10 ì ê

C16 0.1 ì ê

R3 120

C14 0,1 ì ê

1

- DSX1

C4 10 í

2

R1 2,2 ê

C12 0,1 ì ê 3

TV1

"B(3)"

4

C5 10 í

5

C2 10 í

TV2

6

R6 47

7

8

VT1 BFR92A

R2 1,5 ê

9

D1 - ÃÓÍ JTOS- 25 MINI CIRCUITS

D2 - Ì èêðî ñõåì à AD820AR AD

UDSP

C69 10 ì ê

D3

VGN1

+DXS1

VREF

PAO1

OUT1

FBK1

GND1

PAI1

VPOS

COM1

VNEG

COM2

VNEG

PAI2

VPOS

FBK2

GND2

10

C68 0,1 ì ê PAO2

C8 10 í

11

+DSX2

R4 270

C13 0,1 ì ê

12

- DSX2

OUT2

VOCM

VGN2

D3 D4 D5 D6 -

R18 1 ê

24

23

Ì èêðî ñõåì à AD604AR AD

Ì èêðî ñõåì à AD9874BST AD

Ì èêðî ñõåì à AD820AR AD

Ì èêðî ñõåì à ADP3338AKC- 3.3 AD

D7 - ÃÓÍ JTOS- 25 MINI CIRCUITS

22

C23

21

C35

0,1 ì ê

0,1 ì ê

20

L1...L9 - Äðî ññåëü BCL 322522- 10R BI TECHNOLOGIES

R19 1 ê

Z1...Z6 - Ôèëüò ð NFM 4516P13C204F MURATA

C24

0,1 ì ê

19

18

C25

0,1 ì ê

17

16

C26

0,1 ì ê

C36

0,1 ì ê

15

C39 0,1 ì ê

C17 0,1 ì ê

14

R20 330

13

VD

C18 0,1 ì ê

Z5

L7

D6

3

+5V

C60 C61

10 ì ê 1,0 í

R21 47

C56 0,1 ì ê

L4

L3

C27 0,21 í

1

IN

* STU

L9

2

OUT

VA

C64

GND

10 ì ê

C65 0,1 ì ê

C66

10 ì ê

C67 0,1 ì ê

L8

+15V

C58 0,1 ì ê

C28 0,21 í

D4

1

2

C34 0,1 í

C21 0,1 í

3

4

5

+15V

C1 0,1 ì ê

C7 10 ì ê

Z1

8

9

C9 0,1 ì ê

C29 100 ï

R7 2,7 ê

R5 100

C30 100 ï

C10 1 í

U/ F

D2

8

D1

13

VCC

2

C11 1 í

7

OUT

VTUNE

5

6

5

NC

NC

+VS

- IN

VOUT

+IN

NC

- VS

R11 5,6 ê

1

2

3

4

R8 1 ê

C20 8.2 í

R9 3,3 ê

10

C22 1,2 í

16

17

VD

18

C19 10 í R12 68

C32 10 í

R13 82

21

R14 10 ê

R15 10 ê

23

24

RF/ ADC

VDDI

IFIN

CXIF

IF2N

GNDI

IF2P

CXVL

LOP

LON

GCN

CXVM

VDDA

VDDL

GNDA

VDDP

IOUTL

GNDP

GNDL

FREF

IOUTC

GNDS

GNDQ

SYNCB

VDDC

GNDH

GNDC

19

CLKP

C38 10 í

20

CLKN

22

UD

GNDF

11

VREFP

C33 10 í

12

VREFN

R17 100 ê

13

RREF

C31 0,1 ì ê

14

VDDQ

15

C15 680 ï

R10 82

MXON

6

VDDF

C37 2,2 í

7

GCP

VA

L1

MXOP

GNDS

FS

DOUTB

DOUTA

CLKOUT

GNDD

VDDH

PC

VDDD

PD

PE

48

VA

C48 0,1 ì ê

47

46

C42

Z6

0,1 ì ê

45

C44 0,1 ì ê

44

C50 10 í

R25 68

43

42

41

C57 10 ì ê

R24 82

C45 0,1 ì ê

C46 10 í

1

VD

2

R28 3,3 ê

38

C52

1,2 í

37

C53

8,2 í

36

35

C49 10 í

3

C55

680 ï

4

NC

R31 100

NC

- IN

+VS

+IN

VOUT

- VS

NC

8

C59 1 í

7

C62 0,1 ì ê

D7

2

VCC

U/ F

OUT

6

5

13

VTUNE

5

R30 2,7 ê

R26 5,6 ê

C51 10 í

"F"

R29 1 ê

34

33

C63 0,1 ì ê

R27 82

D5

40

39

C54 10 í

C43 0,1 ì ê

R23 47

R22 10 ê

VD

32

67

31

30

58

29

65

66

28

27

26

VD

C47 10 í

25

R16 10 ê

52

60

59

Рис. 6. Принципиальная электрическая схема модулятора промежуточной частоты (лист 2 из 3).

11

U1

+24B

C1

GND

C2

22

+UI

23

+UI

1

+UI

24

- UI

2

- UI

3

- UI

DC/ DC

13

+5V

14

+5V

15

+5V

16

- 5V

11

- 5V

12

- 5V

+5V

C3

C1

- Êî í äåí ñàò î ð 50CV100AX SANYO

C2...C7 - Êî í äåí ñàò î ð Ñ0805Ñ104K5RAC KEMET

C8...C12 - Êî í äåí ñàò î ð 50CV100AX SANYO

U1, U2 - Ì î äóëü ï èò àí èÿ NVS01YG- M6 POWER ONE

C8

U2

22

+UI

23

+UI

1

+UI

24

- UI

2

- UI

3

- UI

DC/ DC

13

+5V

14

+5V

15

+5V

16

- 5V

11

- 5V

12

- 5V

U3

U4

C4

- Ì î äóëü ï èò àí èÿ NVS0.4YJ- M6 POWER ONE

- Ì î äóëü ï èò àí èÿ NVS0.4YJJ- M6 POWER ONE

C9

- 5V

U3

22

+UI

23

+UI

1

+UI

24

- UI

2

- UI

3

- UI

DC/ DC

U4

22

+UI DC/ DC

23

+UI

1

+UI

24

- UI

2

- UI

3

- UI

13

+15V

14

+15V

15

+15V

16

- 15V

11

- 15V

12

- 15V

14

+15V

15

+15V

10

COM

16

COM

- 15V 13

- 15V 11

- 15V 12

+15V

C5

C10

C6

+15V_DA

C11

C7

C12

- 15V_DA

Рис. 6. Принципиальная электрическая схема модулятора промежуточной частоты (лист 3 из 3).

12