Общие сведения о цифровых устройствах

advertisement

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

Глава

3.

ЭЛЕКТРОННЫЕ ЦИФРОВЫЕ

АВТОМАТИЧЕСКИХ СИСТЕМ

ЭЛЕМЕНТЫ

§ 1. Общие сведения о цифровых автоматических системах

Многие автоматические системы действуют при

прерывистом поступлении информации о задающем воздействии.

Причиной этого является обычно импульсный режим работы

устройства. Так, если в состав импульсной гидролокационной

станции входит автоматическое дальномерное устройство, то

сигналы о текущем значении дальности поступают на следящие

системы только во время приема отраженных импульсов. В

импульсном

режиме

осуществляется

многоканальная

гидроакустическая связь при временном разделении каналов.

Некоторые

гидронавигационные

устройства работают в

импульсном режиме и т.д.

Прерывистость может возникать и в случае непрерывного

поступления входных сигналов за счет прерывания, например

сигнала рассогласования или других сигналов внутри следящей

системы. Это имеет место, когда в состав системы входит

микропроцессор (цифровой процессор обработки сигнала),

выходные данные которого выдаются дискретно, с тактом,

характерным для каждого цифрового процессора обработки

сигналов.

Точность, которая может быть достигнута в прерывистой

системе, из-за прерывистости поступления информации всегда

хуже той, которую можно получить от аналогичной непрерывной

системы.

Чтобы

“заполнить”

перерывы,

внутри

системы

устанавливают различные “запоминающие” (фиксирующие или

экстраполирующие) устройства. Их назначение состоит в том,

чтобы на основе предшествующих данных о процессе

регулирования “предсказать” ход процесса на время перерыва

сигнала в точке установки устройства. Для “запоминания” в

системах автоматики применяют пиковые детекторы, амплитудные

123

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

детекторы со сбросом, расширители импульсов, запоминающие

(интегрирующие) конденсаторы (устройства выборки хранения) и

т.д.

Отличие цифровых систем от прерывистых или, как чаще

их называют, дискретных состоит в том, что данные, выдаваемые

микропроцессором, квантованы по уровню. Однако это отличие во

многих практических случаях не является существенным,

поскольку число градаций, выдаваемых микропроцессором, может

быть достаточно большим. По этой причине иногда не делают

различий между дискретными и цифровыми системами.

Отметим, что при анализе дискретных систем используется

математический аппарат уравнений в конечных разностях и zпреобразование.

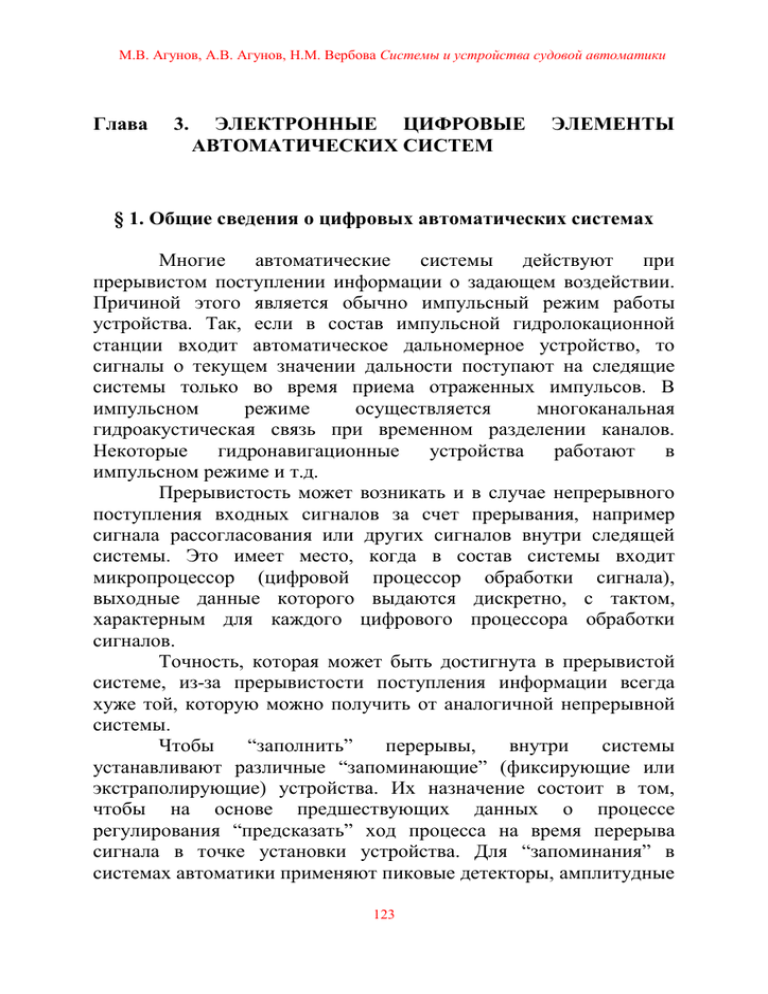

Рис. 3.1 Функциональная схема цифровой автоматической системы

Функциональная схема цифровой автоматической системы

показана на рис. 3.1. Цифровая автоматическая система включает

аналоговый коммутатор (мультиплексор) (АК), аналого-цифровой

преобразователь (АЦП) и цифро-аналоговый преобразователь

(ЦАП) между которыми включен цифровой процессор обработки

сигналов (ЦПОС). ЦПОС осуществляет сравнение задающего

воздействия xз(t) с поступающим по цепи обратной связи

значением регулируемой величины y(t) (задающее воздействие xз(t)

и значение регулируемой величины y(t) могут быть представлены

не только в аналоговой, но и в цифровой форме) и дальнейшую

цифровую обработку сигнала (ЦОС) рассогласования z(t).

Отметим, что в большинстве ЦПОС аналоговый мультиплексор,

аналого-цифровой и цифро-аналоговый преобразователи входят в

состав микропроцессора в виде устройств ввода и вывода данных.

Прерывистость в такой системе обусловлена прерыванием

124

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

информации внутри системы, поскольку микропроцессор выдает

результаты вычислений в виде отсчетов (дискрет) в определенные

тактовые моменты времени.

§ 2. Цифровые устройства

В цифровых автоматических системах принят алфавитный

способ задания информации. Символы, из которых состоит

алфавит, называют буквами. Конечные последовательности букв

алфавита называют словами. Число букв в слове называется длиной

слова. В алфавите из m букв можно получить mk различных слов

длиной k.

Любой дискретный преобразователь информации можно

представить в виде устройства, на вход которого поступают слова

из букв входного алфавита, а на выходе образуются слова из букв

выходного алфавита. Процесс преобразования информации в

таком устройстве сводиться к установлению соответствия между

входными и выходными словами. Такое определенным образом

заданное соответствие называется алфавитным оператором.

Алфавитные операторы, задаваемые на основе конечной системы

правил, принято называть алгоритмом.

Отличительная особенность функционирования цифрового

автомата определяется его двумя свойствами:

1.

автомат имеет конечное множество внутренних

состояний;

2.

переход автомата из одного состояния в другое,

происходит скачкообразно. Скачкообразность перехода позволяет

рассматривать его как мгновенный. Такая абстракция хорошо

описывает основные свойства реальных автоматов и поэтому

принята при построении их теории. Для учета же присущей

реальным устройствам инерционности вводится ограничение в

условие работы цифровых автоматов: после изменения состояния

автомата переход его в следующее состояние возможен не ранее,

чем через фиксированный для данного автомата промежуток

времени, называемый интервалом дискретности (такт). Это

обстоятельство позволяет рассматривать функционирование

автомата в так называемом дискретном автоматном времени,

принимающем целые значения t = 0, 1, 2, …, n … .

125

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

Изменения состояний автомата вызываются входными

сигналами, а результат работы автомата фиксируется

формированием выходного сигнала.

При описании алгоритма функционирования автомата

задаются:

1.

множество букв входного алфавита автомата

U = {u} = {u1, u2, …, un};

2.

множество букв выходного алфавита автомата:

V = {v} = {v1, v2, …, vn};

3.

множество

состояний:

букв

алфавита

его

внутренних

W = {w} = {w1, w2, …, wn}.

Одно из состояний w0 выделяется в качестве начального; в

момент t = 0 автомат всегда находится в начальном состоянии.

На перечисленных множествах необходимо задать

функцию переходов и функцию выходов.

Функция переходов определяет состояние автомата w(t+1)

в момент t+1 в зависимости от его состояния w(t) и входного

сигнала u(t+1):

w(t+1) = ψ[w(t), u(t)].

Функция выходов определяет выходной сигнал v(t). Она

может быть задана несколькими способами. Если выходной сигнал

в момент t определяется только состоянием автомата в этот

момент, т.е.

v(t) = φ(w(t)),

(3.1)

то такой автомат называют автоматом Мура. Если же выходной

сигнал зависит не только от состояния автомата, но и от входного

сигнала, то есть

126

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

v(t) = φ(w(t), u(t)),

(3.2)

то такой автомат называют автоматом Мили.

Два цифровых автомата называются эквивалентными, если

совпадают их входные и выходные алфавиты и для любого

входного слова совпадают их выходные слова. В теории цифровых

автоматов доказывается, что для всякого автомата Мили

существует эквивалентный ему автомат Мура. Это обстоятельство

позволяет рассматривать только автоматы одного вида – автоматы

Мура; законы их функционирования выражаются в более

компактной форме.

Частным случаям дискретных автоматов, находящих

широкое применение, является автомат без памяти, называемый

комбинационной схемой. Сигнал на выходе комбинационной

схемы в момент t согласно (3.2) однозначно определяется

значением входного сигнала в тот же момент времени

v(t) = φ(u(t)).

Если в общем случае при N значениях входного сигнала и L

внутренних состояниях автомата максимальное число возможных

выходных сигналов Мmax=N L, то в автоматах без памяти Мmax=N.

В этом смысле можно считать, что комбинационные схемы имеют

только одно внутреннее состояние (L=1), являющееся

неизменным.

При практическом применении цифровых автоматов

важное место занимает простейшее (побуквенное) преобразование,

заключающееся в замене каждой буквы исходного алфавита

определенной комбинацией букв нового алфавита, имеющей

одинаковую для всех букв длину. С помощью простейших взаимно

однозначных преобразований информацию, заданную в любом

конечном алфавите, можно записать в алфавите, содержащем

только две буквы. Такой алфавит называется стандартным

двухбуквенным или двоичным, а две его буквы обозначаются нулем

и единицей.

Двоичная переменная (у), значения которой зависят от

значений других двоичных переменных (х1, х2, ..., хр), именуемых

аргументами называется переключательной (двоичной, булевой)

функцией:

127

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

у=у(х1, х2,

, хр).

Задание двоичной функции означает, что каждому из

возможных сочетаний (наборов) её аргументов х1, х2, ..., хр

поставлено в соответствие определенное значение у. Функции

считаются различными, если значения у отличаются по крайней

мере для одного набора аргументов. При р аргументах полное

число P их различных наборов P=2р. Поскольку каждому из

наборов может соответствовать два значения у (0 или 1), то общее

число F различных функций р аргументов

p

F 22 .

(3.3)

Наборы аргументов принято нумеровать: при этом

условливаются, что номера наборов совпадают со значениями

двоичных чисел, разрядами которых являются аргументы (х1, х2, ...,

хр). Очевидно, что номера наборов меняются в таком случае от 0 до

2р-1.

Алгебра логики предполагает (допускает) возможность

образования сложных функций, то есть функций, аргументы

которых являются функциями других двоичных аргументов.

Например, если у=у1(z1, z2), а z1=z1(х1, х2) и z2=z2(х3, х4), очевидно,

что у=у1(х1, х2, х3, х4). Операция замены аргументов одной функции

другими функциями называется суперпозицией функций. Эта

операция дает возможность с помощью функций меньшего числа

аргументов, получать функцию большего их числа. Многократное

применение этих операций позволяет получать функции любого

требуемого числа аргументов. В частности, такую возможность

обеспечивает суперпозиция функций двух аргументов.

В соответствии с (3.3) существует 16 различных функций

двух аргументов. Перечень этих функций у0, ..., у15 с указанием

наборов аргументов х1, х2 представлен в таблице 3.1 (там же

указаны наименования логических элементов, реализующих

соответствующие функции).

В алгебре логики справедливы следующие законы:

1.

переместительный

закон

или

закон

коммутативности

128

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

A B B A;

A B B A;

Таблица 3.1

Значения аргументов (х1,

х2) и функций (у0-у15)

x1

0

0

1

1

x2

0

1

0

1

y0

0

0

0

0

Наименование

функций

Наименование

элементов

Константа нуля

Конъюнкция

(лог. умн.)

Генератор «нуля»

Конъюнктор (И)

y1

0

0

0

1

y2

0

0

1

0

Запрет по х2

Схема запрета

(НЕТ) по х2

y3

0

0

1

1

Переменная

(тавтология) х1

Повторитель х1

y4

0

1

0

0

Запрет по х1

Схема запрета

(НЕТ) по х1

y5

0

1

0

1

y6

0

1

1

0

y7

0

1

1

1

y8

1

0

0

0

y9

1

0

0

1

y10

1

0

1

0

y11

1

0

1

1

y12

1

1

0

0

y13

1

1

0

1

y14

1

1

1

0

Штрих Шеффера

y15

1

1

1

1

Константа

«единицы»

2.

Переменная

(тавтология) х2

Логическая

неравнозначность

Дизъюнкция (лог.

слож.)

Стрелка Пирса

Логическая

равнозначность

Инверсия х2

Импликация от х2

к х1

Инверсия х1

Импликация от х1

к х2

Повторитель х2

Исключающее

ИЛИ

Дизъюнктор

(ИЛИ)

Элемент Пирса

(ИЛИ-НЕ)

Эквивалентность

Инвертор х2

Импликатор из х2

Инвертор х1

Импликатор из х1

Элемент Шеффера

(И-НЕ)

Генератор

«единицы»

сочетательный закон или закон ассоциативности

129

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

A B C A B C ; A B C A B C ;

3.

распределительный

дистрибутивности

закон

или

закон

A B C A C B C ; A B C A C B C ;

4.

законы инверсии (законы де Моргана)

A B A B;

A B A B .

В выражениях алгебры логики может возникнуть

неоднозначность, если не условиться о порядке выполнения

операций. Так, в выражении A B C имеется двоякий смысл:

A B C или A B C ; эти выражения не тождественны. В

алгебре логике, как и в обычной алгебре, условились в начале

выполнять операции умножения, а затем сложения. Если же

раньше нужно выполнить сложение, то используются скобки.

Любое выражение алгебры логики представляет собой

суперпозицию функций отрицания, дизъюнкции и конъюнкции.

Возникает вопрос, достаточно ли такого набора функций для

выражения с их помощью произвольной переключательной

функции.

Система

функций

алгебры

логики

называется

функционально полной (базисом), если любую переключательную

функцию ƒ(хn-1, xn-2, …, x0) можно представить как результат

суперпозиции хn-1, xn-2, …, x0 и функций системы, взятых в любом

конечном числе.

В алгебре логики показывается, что функционально

полными являются, например, системы функций состоящие из

двух функций: отрицания и дизъюнкции или же отрицания и

конъюнкции. Пользуясь только любой парой этих функций, можно

выразить любую переключательную функцию. На практике при

построении логических схем широко используется система из трех

функций: отрицания, дизъюнкции и конъюнкции. Добавление к

функционально полной системе еще одной функции, не нарушая ее

130

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

полноты, упрощает построение логических схем. Интересно, что

можно построить функционально полную систему, состоящую из

одной функции. Таковыми являются функции Шеффера и Пирса.

Недостаток такой системы, например в том, что для реализации

даже такой простой операции, как дизъюнкция, требуется

выполнить три операции Шеффера.

Логические схемы, входящие в состав любого цифрового

устройства, строятся из логических элементов. Одним из основных

требований к набору логических элементов является требование

функциональной полноты. Набор логических элементов является

функционально полным, если реализуемые им переключательные

функции составляют функционально полную систему.

Предположим теперь, что зафиксирован, какой-либо набор

логических элементов. Задача построения из такого набора

комбинационной

схемы,

реализующей

некоторую

переключательную функцию, сводится, прежде всего, к ее

представлению в виде выражения алгебры логики. При

составлении

выражений,

описывающих

произвольную

переключательную функцию, важное значение имеют две

простейшие переключательные функции: конституенты единицы и

нуля.

Конституентой

единицы

(минитерм)

называется

переключательная функция n переменных K(хn-1, xn-2, …, x0) = K(x),

равная единице только на одном наборе значений аргументов. Из

этого определения следует, что число различных конституент

единицы равно числу наборов. Удобно каждую конституенту

пронумеровать, присвоив ей номер набора, на котором эта

конституента равна единице. Набор Xα и конституента Kj при α=j

называются соответствующими друг другу. При этом оказывается

справедливым соотношение:

1 при j

K j X

0 при j

(3.4)

Конституента единицы представляет собой конъюнкцию

всех переменных, входящих в это произведение с отрицанием или

без него. Рассмотрим например, конъюнкцию xn1 xn2 ... x0

131

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

всех аргументов с инверсией. Эта конъюнкция равна единице, если

все ее аргументы равны единице. Для этого необходимо, чтобы

xi=0 для всех i. Следовательно, рассматриваемая конъюнкция –

конституента единицы, соответствующая нулевому набору, т.е.

K 0 xn 1, xn 2 ,..., x0 xn 1 xn 2 ... x0 .

В общем случае, чтобы получить конституенту единицы,

соответствующую набору Xα=αn-1, αn-2, …, α0 с номером α, следует

образовать конъюнкцию всех аргументов, причем аргумент xi

входит в конъюнкцию без инверсии, если αi=1 и с инверсией, если

αi=0. Например, для переменных x1=1; x2=0; x3=0 конституента

единицы будет образована, если образовать следующую

конъюнкцию

K x1 , x2 , x3 x1 x2 x3 .

Конституентой

нуля

(макситерм)

называется

переключательная функция n переменных M(хn-1, xn-2, …, x0), равная

нулю только на одном наборе значений переменных. Конституента

нуля Mα на наборе с номером α представляет собой дизъюнкцию

всех аргументов, причем аргумент xi, входит в дизъюнкцию без

инверсии, если в наборе Xα=αn-1, αn-2, …, α0 - αi=0, и с инверсией,

если αi=1. Например для функции четырех аргументов x0=1, x1=0,

x2=1, x3=0

M x0 , x1 , x 2 , x3 x0 x1 x 2 x3 .

Рассмотрим способ выражения переключательной функции

в аналитической форме.

Пусть имеется переключательная функция ƒ(Х), заданная

своими значениями ƒ(xj) для всех наборов (см. табл. 3.2). Образуем

следующую функцию n аргументов:

2 n 1

f X f x0 K 0 f x1 K 1 ... f x2 n 1 K 2 n 1 f x j K j X

132

j 0

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

f X 1 x x x 0 x x x 0 x x x 1 x x x 1 x x x 1 x x x 0 x x x 1 x x x

1 2 3

1 2 3

1 2 3

1 2 3

1 2 3

1 2 3

1 2 3

1 2 3

Таблица 3.2

Х

0

1

2

3

4

5

6

7

x1

0

0

0

0

1

1

1

1

x2

0

0

1

1

0

0

1

1

x3

0

1

0

1

0

1

0

1

f

1

0

0

1

1

1

0

1

Для произвольного набора Х=Хα можно записать:

2 n 1

f X f X j K j X

j 0

.

В соответствии с (3.4) Kj(Xα)=1 при j=α откуда

ƒ*(Xα)=ƒ(Xα). Поскольку мы взяли произвольный набор, то можно

утверждать, что ƒ*(X)=ƒ(X). Следовательно:

2n 1

f X f X j K j X

j 0

и мы получи разложение функции ƒ(X) по конституентам единицы.

Последнее выражение можно упростить, так как члены для

которых ƒ(Xj)=0 можно исключить, а в оставшихся конъюнкциях

ƒ(X)=1 можно не писать. Поэтому в правой части последнего

выражения останутся лишь те конституенты Kj для которых

ƒ(Xj)=1:

f X K j X ,

j 1

(3.5)

f X x1 x2 x3 x1 x2 x3 x1 x2 x3 x1 x2 x3 x1 x2 x3

133

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

где σ1 представляет собой совокупность номеров наборов, на

которых функция ƒ(X) равна единице.

Представление переключательной функции в соответствии

с (3.5) называется совершенной дизъюнктивной нормальной

формой (СДНФ) этой функции. Изложим правило такого

представления:

1.

Записывается дизъюнкция произведений всех

аргументов, причем число таких произведений равно числу

наборов, на которых данная функция равна единице.

2.

Под каждым произведением записывается набор,

обращающий заданную функцию в единицу.

3.

Над аргументами, под которыми записаны нули,

ставятся знаки отрицания.

Переключательную функцию можно представить так же в

совершенной конъюнктивной нормальной форме (СКНФ):

f X M j X

,

j 0

где σ0 - совокупность номеров наборов, на которых функция равна

нулю. Такое представление целесообразно применять, если число

наборов, на которых функция равна нулю, меньше числа наборов,

на которых функция равна единице.

Полученные выше аналитические выражения служат

основой для построения логических схем, реализующих заданные

переключательные функции.

Прежде чем строить логическую схему, реализующую

требуемую переключательную функцию, целесообразно упростить

выражение этой функции, что может быть выполнено различными

методами.

В

частности,

можно

использовать

метод

тождественных преобразований, вытекающих из законов

алгебры логики. Ниже приводится ряд возможных приемов

упрощения.

Прием, основанный на применении формулы

Ax Ax A ,

134

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

называется склеиванием (склеиванием по х).

Прием, называемый поглощением, основан на применение

тождества

Ax A A .

Эти же приемы применены к операции умножения:

A x A x A ;

A x A A .

Иногда

раскрытие:

целесообразно

вынесение

за

скобки

и

их

A x1 A x2 A x1 x2 ;

A x1 A x2 A x1 x2 .

Следующие приемы также иногда приводят к упрощениям:

x xA x A ;

x x A Ax .

Для иллюстрации метода тождественных преобразований

упростим выражение

f x2 , x1 , x0 x2 x1 x0 x2 x1 x0 x2 x1 x0 x2 x1 x2 x1 x0 x2 x1 x1 x0 x2 x1 x0

Для минимизации переключательных функций с числом

переменных до 6 удобен метод диаграмм Вейча (карт Карно).

Метод основан на представлении переключательных функций в

виде прямоугольных таблиц с числом клеток, равным числу

всевозможных наборов, то есть 2n. Каждая клетка диаграммы

Вейча соответствует определенному набору переменных и в нее

вписывается значение функции (0 или 1), которое она принимает

135

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

на данном наборе. В то же время каждой клетке диаграммы

соответствует конституента единицы с номером, совпадающим с

номером набора. Специальная разметка столбцов и срок

диаграммы и, следовательно, нумерация клеток производится

таким образом, что конституенты, соответствующие двум

соседним клеткам обязательно склеиваются по одной из

переменных. Для переключательных функций двух, трех и четырех

переменных разметка диаграмм и нумерация клеток показаны на

рис. 3.2. Важно отметить, что в диаграмме для функции от трех

переменных соседними, следует считать так же крайние клетки

каждой строки, а в диаграмме для функции от четырех переменных

соседними, являются крайние клетки каждой строки и столбца.

При большем числе переменных разметка диаграмм и правила

склеивания несколько усложняются.

Рис. 3.2 Диаграмма Вейча для функций двух, трёх и четырех

переменных

Минимизация переключательных функций начинается с

заполнения диаграммы Вейча. Если на данном наборе функция

равна единице, то в клетке с номером, равным номеру набора,

ставится единица; остальные клетки отмечаются нулями (что

необязательно).

136

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

Диаграмма Вейча позволяет получить выражение

переключательной функции в дизъюнктивной нормальной форме

(ДНФ), представляющей собой дизъюнкцию произведений

аргументов. В отличие от СДНФ входящие в ДНФ произведения

не обязательно содержат все переменные. Для получения ДНФ в

заполненной диаграмме обводят прямоугольными контурами все

единицы. При этом каждый контур должен быть обязательно

прямоугольным и состоять из одних единиц. Число клеток в

контуре должно равняться целой степени числа 2. Говорят, что

контур покрывает 1, 2, 4, 8 и т.д. клеток. Указанными контурами

необходимо покрыть все единицы диаграммы; некоторые контуры

могут содержать только одну клетку.

Каждому контуру соответствует логическое произведение,

входящее в ДНФ. Изолированной единице (контуру, состоящему

из одной клетки) соответствует произведение n переменных, а

именно конституента единицы, номер которой совпадает с

номером клетки. Контуру из двух клеток соответствует

произведение n-1 переменных, причем исключается та переменная,

которая входит в данный контур, как с инверсией, так и без нее.

Если контур состоит из четырех единиц, то в ДНФ ему будет

соответствовать произведение n-2 переменных. В общем случае

наличие единиц в 2m соседних клетках позволяет исключить из

соответствующего произведения m переменных. Следовательно,

при образовании контуров надо стремиться к тому, чтобы

количество контуров было возможно меньшим. При этом одни и

те же клетки, заполненные единицами, могут входить в несколько

контуров.

Применение метода плоскостных диаграмм рассмотрим на

примере минимизации логической функции

F x 0 , x1 , x 2 , x 3 x 0 x 1 x 2 x 3 x0 x1 x 2 x 3 x 0 x 1 x 2 x 3 x0 x1 x 2 x 3 x 0 x 1 x 2 x 3 x0 x1 x 2 x 3 .

Для

минимизации

данной

функции

строим

шестнадцатиквадратную диаграмму (рис. 3.3). Квадраты,

отвечающие членам исходной формулы, отмечаем единицами

(например, набор x0 x1 x2 x3 – соответствует 7 квадрату). Обводим

прямоугольными контурами все единицы. Для каждого

обведенного

контура

записываем

соответствующие

им

137

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

конъюнкции, в которые входят все переменные за исключением

тех по которым происходит склеивание (т.е. переменные входящие

в контур в прямом и инверсном видах). Для контура 1 запишем

x1 x2 , для контура 2 запишем x1 x2 x3 .

Рис. 3.3 Диаграмма для заданной функции

Таким образом, минимальная дизъюнктивная нормальная

заданной логической функции, представляется как

F x1 x2 x1 x2 x3 .

Метод диаграммы Вейча удобно применять при

минимизации не полностью определенных функций. Так

называются функции значения, которых определены не на всех

наборах. Не полностью определенные переключательные функции

описывают условия функционирования схем, на вход которых

некоторые комбинации сигналов вообще не подаются. При

минимизации не полностью определенных функций их удобно

рассматривать как всюду определенные функции, некоторые

значения которых могут выбираться произвольно. Доопределение

следует производить так, чтобы получились группы с

максимальным числом единиц, а число таких групп было

минимальным.

В качестве примера рассмотрим синтез логической схемы,

предназначенной для выделения пяти старших цифр десятичной

системы, представленных в четырехразрядном двоичном коде,

когда номер набора совпадает со значением цифры. Так как всего

имеется 16 четырехразрядных наборов, а цифр - только 10, то в

наборах с номерами от 10 до 15 переключательная функция,

форма

138

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

описывающая данную схему, оказывается неопределенной. На

наборах с номерами от 0 до 4 она равна нулю, а на наборах от 5 до

9 – единице (см. табл. 3.3). На рис. 3.4, а приведена диаграмма

рассматриваемой переключательной функции, а на рис. 3.4, б –

способ ее доопределения, приводящий к минимальной форме:

F x3 , x2 , x1 , x0 x3 x2 x0 x2 x1 .

Таблица 3.3

Номер набора

Значение переменных

Значение функции

x0x1x2x3

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0000

1000

0100

1100

0010

1010

0110

1110

0001

1001

0101

1101

0011

1011

0111

1111

0

0

0

0

0

1

1

1

1

1

*( не определена)

* (не определена)

* (не определена)

* (не определена)

* (не определена)

* (не определена)

Без доопределения функция оказалась бы значительно более

сложной:

F x3 , x2 , x1 , x0 x3 x2 x1 x3 x2 x0 x3 x2 x1 .

С помощью диаграммы Вейча можно находить также

минимальные конъюнктивные формы (КНФ). При этом в группы

следует объединить не единицы, а нули. Кроме того, разметка

139

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

диаграммы изменяется таким образом, что на место переменных с

инверсией ставятся переменные без инверсии и наоборот.

Рис. 3.4 Диаграмма Вейча для не полностью определенной

функции

Выше

было

показано,

что

можно

любую

переключательную функцию представить в виде выражения

алгебры логики, содержащего операции конъюнкции, дизъюнкции

и инверсии. Для решения задачи синтеза логической схемы

необходимо определять схемы реализации таких функций при

помощи любой функционально полной системы элементов.

Элементы, выполняющие непосредственно операции конъюнкции,

дизъюнкции и инверсии, называются соответственно элементами

И, ИЛИ и НЕ. На рис. 3.5 показаны обозначения этих элементов.

При помощи функционально полной системы из элементов

И, ИЛИ и НЕ функции представленные в ДНФ, реализуются

особенно просто. Для этого в начале образуются нужные

конъюнкции. Перед образованием конъюнкций для некоторых

переменных, возможно, придется выполнить операции инверсии.

Для образования конъюнкции от многих переменных применяются

многовходовые элементы И. Если число переменных в

конъюнкции превышает число входов элемента И, то конъюнкция

формируется поэтапно. Дизъюнкция полученных произведений

реализуется путем подачи сигналов с выхода элементов И на

входы элементов ИЛИ. Элементы ИЛИ также могут быть

многовходовыми.

140

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

Широко применяются элементы, реализующие комбинации

операций И, ИЛИ, НЕ. Так, элемент И – ИЛИ позволяет

непосредственно реализовать некоторые несложные функции,

заданные в ДНФ.

Рис. 3.5 Изображение одноступенчатых (а) и двухступенчатых (б)

логических элементов

Наибольшее распространение

элементы И – НЕ и ИЛИ – НЕ (рис. 3.6).

получили

логические

Рис. 3.6 Изображение логических элементов И – НЕ и ИЛИ – НЕ

На рис. 3.7 в виде примера приведена логическая схема из

элементов И – НЕ, реализующая функцию F ABD ABD BD .

141

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

Рис. 3.7 Реализация функции F ABD ABD BD

Последовательностные устройства обладают свойством

запоминания информации, поскольку строятся на элементарных

автоматах с памятью. Количество элементарных автоматов m с

памятью, необходимое для кодирования всех состояний M

последовательностного автомата, определяется соотношением:

m log 2 M .

Значение

m

называют

объемом

памяти

последовательностного автомата.

Основная модель последовательностного устройства

включает комбинационную часть, которая формирует выходные

сигналы устройства и сигналы обратной связи исходя из значений

входных сигналов и значений внутренних переменных (рис. 3.8). В

зависимости от свойств цепей обратной связи различают два вида

автоматов – асинхронные и синхронные.

142

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

Рис. 3.8 Структурная схема автомата с памятью

143

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

В синхронных автоматах цепи обратной связи содержат

элементы задержки (ЭЗ, рис. 3.8, а). Они управляются внешними

тактовыми импульсами и выполняют функцию запоминания

сигналов внутренних переменных на один такт. Благодаря этому

при отсутствии тактовых импульсов передача сигналов по цепям

обратной связи не осуществляется.

В асинхронных автоматах (рис. 3.8, б) задержка сигналов

внутренних переменных обусловлена инерционностью логических

элементов и конечной скоростью распространения электрических

сигналов по цепям (главным образом, первым фактором). Различие

сигналов внутренних переменных на входе и выходе

комбинационных частей имеет место при этом только в течение

динамической части такта; в статической части значения

совпадают и именно эта часть соответствует устойчивому

состоянию автомата.

В комбинационной части последовательностного автомата

могут иметь место состязания (гонки). При применении

синхронных элементов задержки, временные (преходящие)

ошибки не оказывают влияния на работу устройства, поскольку

тактовые импульсы, разрешающие передачу сигналов внутренних

переменных с выхода на вход, подаются по истечении

динамической части тактов. В асинхронных устройствах явление

состязаний имеет первостепенное значение, т.к. именно

динамическая часть такта определяет смену состояний автомата.

Асинхронные

последовательностные

устройства,

включают лишь комбинационные элементы. Синхронные

устройства

предполагают

применение

тактируемых

запоминающих элементов (элементарных автоматов памяти).

Меньшая стоимость комбинационных элементов по сравнению с

запоминающими на начальном этапе внедрения цифровых

устройств определяла преимущества асинхронных автоматов перед

синхронными (несмотря на присущую последним опасность

состязаний). Внедрение микроэлектронной элементной базы

привело к тому, что стоимости комбинационных элементов и

тактируемых элементов задержки стали близкими. Соответственно

в настоящее время применяют главным образом синхронные

последовательностные устройства. Далее задача логического

проектирования рассматривается применительно к устройствам

этого типа.

144

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

Элементарными автоматами с памятью или триггерами

принято

называть

автоматы,

которые

характеризуются

следующими свойствами:

1.

число входных переменных не более трех (входные

переменные принято обозначать специальными символами в

соответствии с функциями, выполняемыми триггерами); в это

число не входит тактовый вход, на который подаются

синхронизирующие импульсы, фиксирующие смену тактов работы

устройства;

2.

число внутренних состояний равно двум, чему

соответствует одна внутренняя переменная (последнюю принято

обозначать символом Q);

3.

число выходных переменных – одна (y), причем

значение y совпадает со значением Q (т. е. функция выхода

y Q ); обычно в триггерах имеется возможность наряду со

значением Q получать инверсную переменную Q ;

4.

функции

переходов,

называемые

t 1

t

t

характеристическими уравнениями Q Q( x , Q ) , являются

полными.

Разновидности триггеров отличаются числом входов, а при

их одинаковом числе – функциями переходов. Общее число W

различных триггеров с p входами определяется соотношением

W 52 ;

p

число практически применяемых разновидностей

существенно

меньше.

Далее

рассматриваются

наиболее

употребимые из них.

Триггер R-S типа представляет собой элементарный

последовательностный автомат с двумя входами R и S,

функционирующий в соответствии с таблицей 3.4. В триггерах R-S

типа одновременная подача единичных значений входных

переменных R и S недопустима (ведет к появлению критических

состязаний). В строчках таблицы переходов триггеров,

соответствующих R t S t 1 , содержится знак неопределенности

значения Q t 1 . Такая комбинация входных переменных

недопустима (считается запрещенной), что алгебраически

t t

выражается требованием R S 0 . Доопределяя значения Q t 1 ,

соответствующие запрещенным комбинациям R t и S t , единицами

145

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

и упрощая СДНФ можно представить характеристическое

уравнение R S триггера в следующей минимальной форме:

Q t 1 S t R t Q t или с учетом закона инверсии (де Моргана)

Q t 1 S t R t Q t .

Таблица 3.4

Такт

R

t

S

0

0

1

1

0

0

1

1

Q t 1

t

t

Q

0

1

0

1

0

1

0

1

t

0

0

0

0

1

1

1

1

0

1

0

X

1

1

0

X

Таблица 3.5

Q t Q t 1

Rt

St

00

01

10

11

*

0

1

0

0

1

0

*

В соответствии с характеристическими уравнениями такой

триггер можно построить на логических элементах И - НЕ и ИЛИ –

НЕ.

На рис. 3.9 приведены две схемы R S триггера, на

элементах И – НЕ и ИЛИ – НЕ соответственно и их графическое

обозначение в соответствии с ЕСКД. Такой триггер называют

асинхронным. В отличие от асинхронного триггера, тактируемый

R S триггер на каждом входе имеет дополнительные схемы

совпадения, первые входы которых объединены и на них подаются

146

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

тактирующие сигналы C (рис. 3.9). Тактируемый R S триггер

описывается уравнениями

Qt 1 S t C t Qt ( R t C t ) ; или

Q t 1 S t C t Q t R t C t .

Рис. 3.9 Схемы асинхронных R S триггеров и их обозначение в

соответствии с ЕСКД

В большинстве случаев на практике требуется определить

комбинацию входных сигналов при заданном переходе триггера из

одного состояния в другое. Такая задача возникает, например, при

синтезе счетчиков, регистров и т.п.

Решить эту задачу можно с помощью характеристической

таблицы (таблица 3.5). Для построения этой таблицы

рассматривают характеристическое уравнение триггера для всех

возможных переходов Q t Q t 1 : 0 0 , 0 1 , 1 0 , 1 1 .

После подстановки в характеристическое уравнение значений Q t

и Q t 1 получают равенства определяющие значения переменных

147

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

и S t для соответствующего перехода. Если переход

происходит при любом значении переменной ее значение считают

безразличным и в таблице отмечают (*).

Rt

Рис. 3.10 Схема тактируемого (синхронного) R S триггера и его

обозначение по ЕСКД

Характеристические таблицы триггеров используют при

синтезе сложных последовательностных схем.

Триггер D типа относится к одновходовым триггерам.

Характеристическое уравнение триггера согласно таблице

переходов

(таблица

3.6)

определяется

соотношением

t 1

t t

t

t

t

Q DQ DQ D .

Из уравнения следует, что триггер в момент времени

t 1 принимает состояние, соответствующее значению переменной

на D входе в момент времени t , т.е. с помощью D триггера

осуществляется задержка входного сигнала. Таблица 3.7 является

характеристической таблицей для D триггера.

Тактируемый D триггер функционирует в соответствии с

таблицей переходов 3.8. Характеристическое уравнение D

148

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

триггера, составленное в соответствии с этой таблицей,

записывается в виде Q t 1 C t Q t C t D t . Из уравнения следует,

что при наличии тактирующего сигнала ( C 1 ) триггер переходит

в состояние Q t 1 D t , а при отсутствии тактирующего сигнала

( C 0 ) триггер сохраняет предыдущее состояние.

Таблица 3.6

Такт

D

Q t 1

t

Qt

t

0

1

0

1

0

0

1

1

0

1

0

1

Таблица 3.7

Q t Q t 1

Dt

00

01

10

11

0

1

0

1

Таблица 3.8

Ct

Dt

Qt

Q t 1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

1

1

149

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

В соответствии с характеристическим уравнением

(инвертировав левую и правую части уравнения) тактируемый D

триггер может быть построен например так, как показано на

рис.3.11, а, здесь же приведено его обозначение в соответствии с

ЕСКД.

Рис. 3.11 Схема тактируемого (а) и двухступенчатого (б) D

триггера

Среди триггеров типа D большое распространение

получили триггеры тактируемые фронтом. Такие триггеры

строятся по двухступенчатой схеме. Двухступенчатые триггеры

состоят из двух тактируемых импульсом триггеров (основного –

master и дополнительного – slave), которые синхронизируются

взаимно инверсными тактовыми сигналами. На рис. 3.11, б

приведена логическая структура двухступенчатого триггера. При

воздействии тактового импульса информация со входа ведущего

триггера T1 переписывается на его выход. Ведомый триггер T2 в

это время не меняет своего состояния, поскольку на его тактовом

150

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

входе действует нулевой сигнал. После окончания тактового

импульса ведомый триггер перейдет в то состояние, в котором

находится ведущий триггер. Так как выходной сигнал снимается с

ведомого триггера, то внешне это проявляется таким образом, как

если бы перепись сигнала со входа производилась в момент

воздействия на тактовый вход перепада 1/0. Такой тактовый вход

обозначают треугольником, повернутым вершиной в обратную

сторону от триггера, если активным является перепад 0/1

треугольник повернут вершиной внутрь триггера.

Триггер T типа является одновходовым устройством с

двумя устойчивыми состояниями, изменяющим свое состояние на

противоположное всякий раз, когда на его вход T поступает

управляющий сигнал. Триггер T типа функционирует в

соответствии с таблицей переходов 3.9 и описывается

характеристическим уравнением Qt 1 Q t T t Q t T t .

Функция перехода T триггера по виду совпадает с

функцией логической неравнозначности двух переменных x1 и x2

(Если значения T и Q поставить в соответствие со значениями x1

и x2 ). Это означает, что счетный триггер выполняет операцию

суммирования входной переменной по модулю 2.

Характерной особенностью T триггера является то, что

частота изменения потенциала на его выходе в два раза меньше

частоты сигнала на входе T . Это свойство триггера используется

при построении счетчиков.

Триггер T типа можно построить на логических

элементах. Однако в настоящее время в составе серий, как

правило, либо имеются триггеры T типа, либо триггеры D типа и

J K типа в интегральном исполнении, которые можно перевести

в режим T

триггера коммутацией некоторых выводов

микросхемы. Так например, если в тактируемом D триггере вход

D соединить с инверсным выходом Q , то D триггер

превращается в T

уравнение

триггер, поскольку при условии D t Q t

тактируемого

триггера

D

Q t 1 C t Q t C t D t

приобретает вид Q t 1 C t Q t C t Q t , при этом на вход C

151

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

подаются счетные импульсы. На рис. 3.12 приведено условное

обозначение асинхронного и тактируемого T триггера.

При

синтезе

многоразрядных

счетчиков

и

последовательных регистров на T триггерах используется

характеристическая таблица 3.10.

Таблица 3.9

Такт

T

Q t 1

t

Qt

t

0

1

0

1

0

0

1

1

0

1

1

0

Таблица 3.10

Q t Q t 1

Tt

00

01

10

11

0

1

1

0

Таблица 3.11

Такт

j

0

0

1

1

0

0

1

1

t

K

Q t 1

t

t

Q

0

1

0

1

0

1

0

1

0

0

0

0

1

1

1

1

152

t

0

0

1

1

1

0

1

0

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

Триггер J-K типа относится к двухвходовым

устройствам, функционирующим в соответствии с таблицей 3.11.

Таблица 3.12

Q t Q t 1

00

01

10

11

Kt

jt

0

1

*

*

*

*

1

0

Из таблицы 3.11 следует, что при комбинации сигналов J

K , соответствующей конъюнкции J K 1, триггер

и

J K 1,

инвертирует предыдущее состояние (т.е. при

t 1

t

Q Q ). В остальных случаях J K триггер функционирует

как R S триггер. При этом вход J эквивалентен входу S , а

вход K - входу R . Функционирование J K триггера

t 1

t t

t t

описывается характеристическим уравнением Q J Q K Q .

Рис. 3.12 Условное обозначение асинхронного и тактируемого T

триггера

В схемотехнике наибольшее распространение получили

J K

тактируемые

триггеры. Эти триггеры являются

универсальными, поскольку коммутацией внешних выводов J K

триггер можно превратить в триггер, выполняющий функции

RS , D и T

триггера. Так например, если в

характеристическом уравнении для J K триггера принять

J t D t и K t D t , то в результате получим Q t 1 D t . Это

153

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

выражение

полностью

совпадает

с

характеристическим

уравнением для D триггера. Для получения T триггера

достаточно объединить входы J и K . В этом случае

характеристическое уравнение J K триггера приобретает вид

характеристического уравнения T триггера.

Условное обозначение тактируемого J K триггера, а

также организация D и T триггеров на основе J K триггера

приведены на рис. 3.13. Характеристическая таблица для J K

триггера имеет вид таблицы 3.12.

Рис. 3.13 Условное обозначение тактируемого J K триггера (а) и

организация на его основе D триггера (б) и T триггера (в)

В настоящее время существует ряд разновидностей

триггеров с дополнительными входами. Введение этих входов

придает триггеру дополнительные свойства характерные

нескольким типам триггеров. Примером может служить триггер

К155ТМ2, который обладает свойствами тактируемого D триггера

и асинхронного R S триггера (см. рис. 3.14).

Рис. 3.14 Условное обозначение триггера К155ТМ2

Синтез синхронных последовательностных устройств

выполняется исходя из заданной (таблично или алгебраически)

системы функций выходов и переходов, в предположении, что

154

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

элементная база определена (заданы разновидности применяемых

триггеров и комбинационных элементов; считается, что по способу

синхронизации триггеры относятся к двухступенчатым).

Составление уравнений выходов и переходов предполагает

предварительное установление (на основании содержательного

описания автомата) числа его внутренних состояний и

кодирования последних наборами внутренних переменных.

Сложность структуры автомата зависит от выбора объема его

памяти (он может превышать минимально необходимый), способа

кодирования возможных внутренних состояний и разновидности

применяемых триггеров. По этой причине рациональное решение

упомянутых вопросов, должно составлять неотъемлемую часть

синтеза автомата. Однако в общей постановке эта задача

относится к числу проблемных в современной теории конечных

автоматов и даже ее ограниченное решение связано со

значительными

трудностями.

В

практике

логического

проектирования типовых узлов цифровых устройств число

устойчивых состояний, их кодирования и тип применяемых

триггеров определяют, как правило, эвристически на основании

известных сведений по опыту разработки аналогичных узлов.

Методы структурного синтеза гарантируют при этом

определение работоспособной структуры автомата.

При

синтезе

последовательностных

автоматов

принципиально новой задачей в сравнении с синтезом

комбинационных схем является обеспечение требуемого вида

функции переходов автомата. Каждое уравнение системы

переходов

определяет

переходы

одного

из

триггеров

синтезируемого автомата (для произвольной i-ой переменной

Wi Qi ). Анализ показывает, что любому из уравнений переходов

(далее

i-му)

может

быть

придана

форма

t 1

t 1

t

t

t

t

t

t

Wi Qi g1i Qi g 2i Qi , где g1i и g 2 i - функции множества

внутренних состояний W t и множества входных переменных u t .

Уравнения данного вида определяют переходы каждого триггера в

соответствии с выполняемыми ими функциями в автомате,

поэтому они получили наименование прикладных уравнений

триггеров.

С другой стороны, переходы каждого триггера

определяются его характеристическим уравнением; для триггера

155

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

любой

t 1

i

Q

разновидности его можно представить в виде

c Qit c2t i Qi t , где c1ti и c 2t i - функции входных переменных

t

1i

триггера в течение такта t ( R и S в триггерах R S типа, J и

K в триггерах J K типа и т.п.).

Для определения структуры комбинационных ветвей

автомата необходимо установить связь входных переменных

каждого триггера U Qt i с множеством входных U t и внутренних

W t переменных автомата U Qt i U Qi (U t , W t ) .

Уравнения этого вида получили наименование уравнений

входов триггеров. Знание этих уравнений позволяет определить

структурные схемы комбинационных ветвей в соответствии с

методами синтеза комбинационных схем. В целом структурный

синтез автомата сводится, таким образом, к определению

прикладных уравнений и совместному решению их с

характеристическими уравнениями применяемых триггеров с

целью получения уравнений входов последних.

Совместное решение прикладных и характеристических

уравнений можно осуществлять алгебраически или с помощью

таблиц переходов и соответствующих им карт Карно.

Рассмотрим последовательность синтеза автомата с

помощью карт Карно на следующем примере.

Пусть требуется построить автомат, управляющий

полумостовым инвертором напряжения (см. рис. 3.15), который

должен сформировать импульсы управления силовыми ( VT1 и

VT2 ) и коммутирующими ( VT3 и VT4 ) тиристорами (рис. 3.16).

Рис. 3.15 Принципиальная схема однофазного инвертора

156

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

Полумостовой

инвертор

напряжения

работает

следующим образом. Пусть в некоторый момент времени на

управляющие электроды тиристоров VT1 и VT4 поданы

отпирающие импульсы. Тиристоры VT1 и VT4 отпираются и через

нагрузку Zн начинает протекать ток по цепи: положительная

клемма источника питания E, открытый тиристор VT1, нагрузка Zн,

конденсатор C2, отрицательная клемма источника питания.

Одновременно происходит заряд коммутирующего конденсатора

C3 по цепи: положительная клемма источника питания E,

открытый тиристор VT1, коммутирующий дроссель L1,

коммутирующий конденсатор C3, открытый тиристор VT4,

отрицательная клемма источника питания. По окончании заряда

конденсатора C3 тиристор VT4 запирается, при этом левая на рис.

3.15 обкладка конденсатора оказывается заряженной до

положительного потенциала. По окончании формирования

полуволны напряжения питающего нагрузку управляющий

импульс подается на тиристор VT3, при этом начинается перезаряд

конденсатора C3 по цепи левая обкладка конденсатора, дроссель

L1, диод VD1, открытый тиристор VT3, правая обкладка

конденсатора C3. Тиристор VT1 оказывается под действием

приложенного к нему обратного напряжения падающего на диоде

VD1 и запирается. Затем управляющие импульсы подаются на

тиристоры VT2 и VT3 и начинается дозаряд конденсатора C3 и

формирование второй полуволны напряжения питающего нагрузку

которые протекают аналогично описанному выше.

На основании словесного описания работы плумостового

инвертора напряжения строятся временные диаграммы работы его

системы управления. Временные диаграммы входных и выходных

сигналов являются одним из способов задания автомата. Они

описывают все возможные комбинации сигналов. На основании

анализа временных диаграмм (см. рис. 3.16), можно выделить

шесть состояний автомата, таким образом, для его реализации

потребуется три триггера. Выберем в качестве элементной базы

триггеры типа J K (К155ТВ1). Составим в соответствии с

временными диаграммами таблицу переходов (см. таблицу 3.13),

причем для устранения гонок кодирование состояний автомата

проведем в соответствии с кодом Грея, переход автомата из одного

состояния в другое будем осуществлять по переднему фронту

157

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

сигнала C , а формирование импульсов управления в соответствии

с тактовыми импульсами C .

Рис.3.16 Временные диаграммы работы системы управления

автономным инвертором

Таблица 3.13 функционирования автомата, отражает

двоичные коды всех предыдущих и последующих его состояний,

выраженных через состояния триггеров в моменты времени

прихода очередного входного стробирующего (тактирующего)

сигнала C , а также значение импульсов управления силовыми

( VT1 , VT2 ) и коммутирующими ( VT3 , VT4 ) тиристорами в эти же

моменты времени.

Таблица 3.13

№

сос

т

1

2

3

4

5

6

c

Q0t

Q1t

Q2t

Q0t 1 Q1t 1 Q2t 1

VT1 VT2 VT3 VT4

1

1

1

1

1

1

0

1

1

0

0

0

0

0

1

1

1

0

0

0

0

0

1

1

1

1

0

0

0

0

1

0

0

0

0

0

0

1

1

1

0

0

158

0

0

0

1

1

0

0

0

0

1

0

0

0

0

1

1

0

0

1

0

0

0

0

1

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

На основе таблицы 3.13 для каждого триггера составим

карты Карно, отражающие переход данного триггера из

предыдущего состояния Qit в последующее Qit 1 (см. рис. 3.17).

Для этого в клетки карты, соответствующие номерам предыдущих

состояний автомата, вписываются 2-х разрядные двоичные числа,

выражающие переход триггера Qit Qit 1 при изменении

состояния автомата. Полученные таблицы называют прикладными.

В этих таблицах прочеркнутая клетка соответствует исключенному

состоянию автомата, например состоянию Q0Q1Q2 .

Рис. 3.17 Прикладные таблицы автомата

На основании полученных прикладных таблиц и

характеристической таблицы J K триггера (таблица 3.12)

составляем карты Карно соответственно для J (см. рис. 3.18) и K

(см. рис. 3.19) входов каждого триггера. Для этого 2-х разрядные

двоичные

числа

в

прикладных

таблицах

заменяют

соответствующими обобщенными значениями из клеток

характеристической таблицы для каждого входа триггера. В

результате получается набор карт Карно, отражающих значения

логических функций на всех входах каждого триггера в

зависимости от состояний автомата.

Рис. 3.18 Карты Карно для J входов

159

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

Используя методы минимизации логических функций, из

полученного набора карт Карно составляем минимизированные

логические уравнения, которые связывают между собой входы и

выходы всех триггеров автомата.

Учитывая, что в прочеркнутых клетках, как и в клетках со

звездочками, функция не определена, при проведении контуров в

картах Карно включаем в контуры указанные клетки.

Рис. 3.19 Карты Карно для K входов

После минимизации получаем логические уравнения

входов J и K триггеров автомата

J 0 Q1t Q2t ; K 0 Q1t ;

J 1 Q0t ; K1 Q2t ;

t

J 2 Q0t Q1t ; K 2 Q1 .

Эти уравнения полностью определяют структуру

синтезируемого автомата (см. рис. 3.20). Логические выражения,

описывающие работу выходной комбинационной схемы, получим

из таблицы 3.13.

VT1 CQ0t Q1t Q2t ;

VT2 CQ0t Q1t Q2t ;

160

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

VT3 CQ0t Q1t Q2t CQ0t Q1t Q2t C (Q0t Q1t Q2t Q0t Q1t Q2t ) CQ1t Q2t ;

VT4 CQ0t Q1t Q2t CQ0t Q1t Q2t C (Q0t Q1t Q2t Q0t Q1t Q2t ) CQ0t Q1t .

Принципиальная схема синтезированного автомата

приведена на рис. 3.20 (без выходной комбинационной схемы).

Рис. 3.20 Синтезированный автомат без выходной

комбинационной схемы

При составлении логических схем узлов цифровых

устройств необходимо выполнить два условия:

не подсоединять к одному и тому же входу

логического элемента несколько выходов;

не образовывать замкнутых цепей, по которым

сигнал с выхода какого-либо элемента мог бы снова попасть

(пройдя, возможно, другие элементы) на один из входов того же

самого элемента.

Как было показано, при наличии замкнутых цепей

устройство на логических элементах может иметь несколько

внутренних состояний, что используется для построения

триггерных структур.

161

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

Дешифраторы. Дешифратор – устройство, которое служит

для дешифрования любого n-буквенного слова. Он представляет

собой комбинационную схему с n входами и m выходами, на

каждом из выходов сигнал, равный единице, возникает только при

вполне определенной для каждого из выходов комбинации

входных сигналов. Если пронумеровать наборы входных сигналов,

а также выходы дешифратора целыми числами, начиная с нуля, то

его работу можно описать так: при подаче на вход j-го набора

входных сигналов x j сигнал y j 1 появляется только на выходе с

номером j.

Рис. 3.21 Дешифратор: условное обозначение (а), внутренняя

структура (б)

Максимальное количество выходов дешифратора равно

числу n-разрядных двоичных чисел, т.е. m 2 n . Такие

дешифраторы

называются

полными.

Иногда

возникает

необходимость дешифровать только одно или несколько входных

162

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

слов (чисел). В этом случае имеют дело с неполными

дешифраторами.

Иное название дешифраторов – декодеры. Условное

обозначение дешифраторов приведено на рис. 3.21, а, на рис. 3.21,

б его внутренняя структура.

Для примера приведем таблицу истинности дешифратора

3-х разрядного числа (табл. 3.14).

Таблица 3.14

№

слова

1

2

3

4

5

6

7

8

X3

X2

X1

Y1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

1

Y2

Y3

Y4

Y5

Y6

Y7

Y8

1

1

1

1

1

1

1

Рис. 3.22 Преобразователь кода для управления семисегментным

индикатором

Для решения некоторых конкретных задач выпускаются

ИС, которые служат преобразователями кодов. В отличие от

дешифратора преобразователь кодов может формировать

произвольное число нулевых и единичных сигналов на выходах.

163

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

Каждому входному набору (слову) ставится в однозначное

соответствие выходной набор (слово). Примером преобразователя

кодов служит микросхема, преобразующая двоичный код в

сигналы управления семисегментным индикатором (рис. 3.22).

Здесь, например, двоичному набору 0000 должно соответствовать

формирование логической единицы на всех выходах, кроме G.

Обратную функцию выполняют шифраторы. У

шифратора 2n входов, на один из них подается логическая 1, а на

остальные – 0, на n выходах формируются слова, соответствующие

двоичному коду номера единичного входа.

Мультиплексор.

Мультиплексор

осуществляет

подключение одного выхода к любому из имеющихся входов.

Логический сигнал на выходе F (рис. 3.23) принимает значение

сигнала на входе Di в зависимости от управляющих сигналов A0,

A1, A2, …, Ai. Обычно вход D0 подключается к выходу при наборе

управляющих сигналов 000 … 0, D1 – при 000 … 1 и т.д.

Функциональный узел, который выполняет функции,

противоположные мультиплексору (сигналы, поступающие на

вход, распределяются по нескольким каналам) называется

демультиплексором.

Существуют

мультиплексоры

и

демультиплексоры для коммутации аналоговых сигналов.

Рис. 3.23 Мультиплексор

Сумматоры. Сумматор – схема осуществляющая

получение арифметической суммы двух одноразрядных двоичных

чисел. Числа в двоичной системе складываются по тем же

правилам, что и в десятичной системе счисления. Например:

21+22=43, 1011+1001=10100. Основу сумматоров составляют

либо элементарные одноразрядные комбинационные сумматоры,

164

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

либо элементарные автоматы с памятью. Соответственно принято

делить сумматоры на комбинационные и накапливающие.

Одноразрядные

комбинационные

сумматоры

осуществляют сложение двух двоичных разрядов x, y и значения

переноса z из младшего разряда и осуществляют выработку

значения суммы S и переноса p в старший разряд.

Рис. 3.24 Комбинационные полусумматор (а) и полный сумматор

(б)

Одноразрядный сумматор (рис. 3.24, б) с тремя входами

строится в соответствии с таблицей 3.15 двоичного сложения, из

которой вытекают минимальные дизъюнктивные формы для

функций S и p:

S x yzVx yz Vxyz Vxyz;

p xyVyzVxz.

165

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

На основе одноразрядного сумматора могут быть

построены схемы сравнения, выявляющие совпадения (равенство)

кодов.

Таблица 3.15

x

0

0

0

0

1

1

1

1

y

0

0

1

1

0

0

1

1

z

0

1

0

1

0

1

0

1

S

0

1

1

0

1

0

0

1

p

0

0

0

1

0

1

1

1

Для совпадения цифр в i-м разряде необходимо, чтобы обе

цифры были равны нулю или единице. Отсюда получаем функцию

эквивалентности одноразрядных двоичных чисел Ri xi yi xi yi .

Соответственно функция неравнозначности или сумма по

модулю два (исключающее ИЛИ) определяется выражением

Ri xi yi xi yi x y , которое реализуется в полусумматоре (рис.

3.24, а) для получения суммы S. На рис. 3.25, а приведено условное

обозначение сумматора по модулю 2. Кроме рассмотренных схем в

цифровых устройствах применяются также логические схемы,

выявляющие большее или меньшее из двух сравниваемых

двоичных чисел (см. рис. 3.25, б) (К555СН1).

Рис. 3.25 Схемы сравнения чисел.

166

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

Накапливающие сумматоры строятся, как правило, на

статических триггерах со счетными входами и рассчитываются на

последовательный ввод разрядов слагаемых.

Двоичные накапливающие сумматоры строятся на базе

триггеров со счетными входами. Одноразрядный сумматор имеет

один вход, на который последовательно подаются разряды

слагаемых и цифра переноса в данный разряд, и два выхода S и p:

на одном выходе формируется сумма S по модулю два, а на другом

сигнал переноса p в старший разряд (см. рис. 3.26, а).

Рис. 3.26 Накапливающие сумматоры.

За время суммирования в одном разряде триггер может

переключаться до 3 раз. Четвертое переключение необходимо при

установке нуля. С этим связан основной недостаток

накапливающего сумматора – низкое быстродействие. Однако,

если далее к сумме первых двух чисел нужно добавить третье,

четвертое число и т.д., то добавление каждого нового числа

потребует максимум двух переключений триггера, потому что к

началу сложения цифры одно из слагаемых уже находятся в

счетчике. В связи с этим проигрыш в скорости при выполнении

167

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

многократных суммирований по сравнению с комбинационным

сумматором получается не слишком большим. В то же время

экономия в количестве оборудования получается заметной.

На рис. 3.26, б показан принцип соединения одноразрядных

накапливающих сумматоров. Имеющиеся между одноразрядными

сумматорами линии задержки исключают возможность наложения

во времени сигналов переноса и второго слагаемого.

Регистры. Регистром называют совокупность триггеров,

объединенных общими схемами управления, предназначенных для

хранения одного двоичного слова (кода). Регистры используются

также для выполнения некоторых операций над кодами: сдвиг кода

вправо или влево, образование обратного кода и др.

В зависимости от способа ввода и съема информации

различают параллельные и последовательные регистры.

В регистрах параллельного действия все разряды кода

вводятся и выводятся одновременно. Помимо триггеров в состав

регистров входит еще и ряд схем И для управления приемом и

выдачей кода (рис. 3.27). Каждый триггер предназначен для

запоминания одного разряда кода. Перед записью кода на шину

установки нуля подается сигнал, переводящий все триггеры в

нулевое состояние. Для записи кода в регистр на схемы И,

соединенные с единичными входами подаются цифры ai разрядов

кода и сигнал записи информации. Возникающие на выходах схем

И сигналы воздействуют на входы установки единицы триггеров;

при ai 1 соответствующие триггеры переводятся в единичное

состояние. Для считывания кода записанного в регистре, на схемы

И, подключенные к выходам Q триггеров, подается сигнал

считывания. При этом сигналы, соответствующие единице,

появляются на выходе только тех схем И, для которых Qi 1 .

Параллельные регистры могут быть образованы из

триггеров любого типа.

От типа применяемых триггеров будет зависеть лишь

способ управления вводом информации.

Последовательные регистры воспринимают информацию

через один разряд – входной и выдают ее также через одни разряд

называемый выходным. Последовательные регистры состоят из

триггеров, соединенных последовательно таким образом, что

выходной сигнал предыдущего триггера поступает на вход

168

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

последующего.

Все

триггеры

управляются

общими

синхронизирующими импульсами, причем появление импульса на

тактовом входе вызывает сдвиг записанной в нем информации на

один разряд вправо или влево. Поэтому такие регистры

называются регистрами сдвига.

Рис. 3.27 Параллельный регистр.

На рис. 3.28 показана схема регистра позволяющего

производить сдвиг кода как в сторону младших разрядов, так и в

сторону старших разрядов. Здесь выход Q каждого триггера может

быть соединен как со входом D последующего триггера, так и со

входом D предыдущего, в зависимости от состояния

управляющего сигнала y. При наличии сигнала y 1 включается

прямая связь между разрядами, а при y 0 - обратная. Таким

образом при y 0 происходит сдвиг в сторону старших разрядов,

а при y 1 - в сторону младших разрядов. Подобные регистры

называются реверсивными регистрами сдвига. Сдвиг информации

осуществляется под воздействием тактового импульса.

При построении регистров сдвига применяются триггеры

типа R-S, D или J-K.

Сдвигающие

регистры

применяются

также

для

преобразования параллельного кода в последовательный и

наоборот. Для этого каждый разряд регистра должен иметь

дополнительный вход для параллельного приема кода.

169

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

Преобразование последовательного кода в параллельный

осуществляется путем одновременного опроса состояний всех

триггеров регистра (см. рис. 3.27).

Рис. 3.28 Реверсивный регистр сдвига.

Импульсные счетчики. Импульсный счетчик можно

определить как автомат Мура с N состояниями, имеющий один

элементарный входной канал. При подаче на вход счетчика

сигнала, он переходит в состояние, номер которого на единицу

больше номера предыдущего состояния; если же номер состояния

является максимальным, то счетчик переходит в нулевое

состояние.

При кодировании состояния счетчика обычными

двоичными кодами последовательных целых неотрицательных

чисел, начиная с нуля, т.е. числами вида 00 … 00, 00 … 01, 00 … 10,

00 … 11 и т.д., импульсный счетчик называется двоичным.

Двоичный n-разрядный счетчик имеет N 2 n различных

состояний, каждому из которых соответствует двоичное число в

пределах от 0 до 2 n 1 .

Рис. 3.29 Двоичный счетчик.

170

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

При построении двоичных счетчиков в качестве

элементарных автоматов обычно используют двухступенчатые

счетные триггеры с дополнительным входом установки нуля.

Двоичный счетчик можно получить, если последовательно

соединить выход i-го триггера с T – входом (i+1) – го триггера

(рис. 3.29). Если сигнал на вход T – триггера последующего

разряда подавать с инверсного выхода триггера предыдущего

разряда (рис. 3.30) получим вычитающий счетчик.

При исключении некоторых устойчивых состояний

двоичного счетчика можно построить счетчик с коэффициентом

пересчета не равным 2n. Такие счетчики называют недвоичными.

Рис. 3.30 Вычитающий двоичный счетчик.

На рис. 3.31 иллюстрируется пример построения счетчика с

коэффициентом пересчета равным трем.

Рис. 3.31 Недвоичный счетчик.

Счетчики являются одним из наиболее распространенных

узлов цифровых устройств. Существует большое многообразие

171

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

счетчиков, это и так называемые реверсивные счетчики, способные

работать как в режиме сложения, так и в режиме вычитания, и

кольцевые, в которых происходит сдвиг единицы из разряда в

разряда под действием поступающих на вход импульсов и т.д.

Способы построения таких счетчиков основаны на введении в них

дополнительных элементов и связей.

§ 3. Микропроцессоры и узлы микропроцессорных устройств

Микропроцессор (МП) - это программно управляемое

устройство, осуществляющее процесс обработки цифровой

информации и управление им, построенное на основе одной или

нескольких больших (сверхбольших) интегральных схем.

Этот микроэлектронный прибор стал в последние годы

ядром многих электронных систем автоматического регулирования

и управления аппаратурой и технологическими процессами,

измерительных устройств и устройств отображения и обработки

информации.

Такое широкое внедрение микропроцессора в обширный

класс устройств обусловлено, в первую очередь, тем, что МП в

отличие от традиционных интегральных схем выполняет не одну

какую-либо функцию, а набор арифметических и логических

функций и, кроме того, экономичен в изготовлении как

стандартное изделие в условиях серийного производства.

Первый МП был разработан фирмой Intel inc. в 1973 г. Это

был МП с фиксированной длиной слова и системой команд,

физически оформленный в виде 4-х разрядной p-МОП большой

интегральной схемы с названием I 4004.

Первым, действительно универсальным в рамках широкого

круга решаемых задач стал разработанный этой же фирмой МП I

8080. Этот МП имеет довольно большое (64К слов) адресное

пространство и универсальную мощную (78 команд) систему

команд.

Существует большое количество разновидностей МП,

выпускаемых различными фирмами, как отечественными, так и

зарубежными, отличающихся друг от друга как по архитектуре,

так и по другим различным признакам. Рассмотрим некоторые

особенности их построения и функционирования на примере

172

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

отечественного

аналога

однокристальной

ЭВМ

I8051,

однокристального микроконтроллера КМ1816BE51.

Микроконтроллер (МК) KM1816BE51 выполнен на основе

высокоуровневой n-МОП технологии и выпускается в корпусе,

имеющем 40 выводов.

Отечественные и зарубежные фирмы предлагают полный

аналог этого МК, выполненный по другим технологиям, например,

МК KM1830BE51 (I 87C51) выполнен по К-МОП технологии. На

рис. 3.32 показана цоколевка корпуса МК51 и имена выводов.

Для

работы

МК51

требуется

один

источник

электропитания +5В. Через 4 программируемых порта

ввода/вывода МК51 взаимодействует с внешними устройствами в

стандарте ТТЛ - схем с тремя состояниями выхода.

Рис. 3.32 Цоколевка корпуса МК 51 и имена выводов

173

М.В. Агунов, А.В. Агунов, Н.М. Вербова Системы и устройства судовой автоматики

В состав МК51 входят: 8-битное АЛУ; ПЗУ емкостью 4

Кбайт; ОЗУ емкостью 128 байт; два 16-битных таймера/счетчика;

последовательный

порт

с

максимальной

скоростью

приемопередачи в асинхронном режиме - 375 Кбит/сек;

двухуровневая система прерываний от 5 источников; 32

двунаправленные программируемые линии ввода/вывода. Имеется

возможность расширения памяти программ и внешней памяти

данных. Отличительной особенностью системы команд МК51