Уточнение спецификаций архитектуры СБИС

advertisement

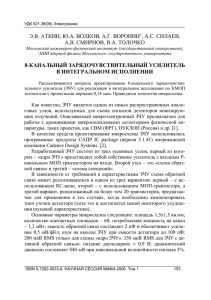

CИГНАЛЬНЫЕ КОНТРОЛЛЕРЫ МС-0226 (ЦПОС-02) И МС-0226G (МЦОС) НА БАЗЕ ПЛАТФОРМЫ «МУЛЬТИКОР» Т.В. Солохина, А.В. Глушков, Я.Я. Петричкович ГУП НПЦ «ЭЛВИС», secretary@elvees.com 1. Введение. Современные тенденции в разработке микропроцессоров связаны с переходом к размещению на одном кристалле нескольких процессорных ядер и созданию для таких систем специальных технологий интеграции ядер на кремнии, тестирования и верификации. Микросхемы сигнальных микроконтроллеров ЦПОС-02 и МЦОС спроектированы как однокристальные трехпроцессорные «системы на кристалле» на базе IP-ядерной (IP-intellectual property) платформы «МУЛЬТИКОР», разработанной в ГУП НПЦ «ЭЛВИС». По общепринятой классификации СБИС, разрабатываемых на базе платформы «МУЛЬТИКОР», микросхемы ЦПОС-02 и МЦОС(MC-0226 и МС-0226G по классификации сигнальных контроллеров соответственно) относятся к сигнальным контроллерам мидиконфигурации с плавающей и фиксированной точкой. Главное отличие между микросхемами - наличие второго накристального PCI контроллера в составе микросхемы МЦОС, который позволит интегрировать микросхему МЦОС на плате с серией микросхем графических контроллеров разработки НИИСИ РАН, обеспеченных также накристальным PCI контроллером. Поэтому далее по тексту технические особенности реализации данной пары микросхем рассматриваются в приложении к микросхеме ЦПОС-02 (MC-0226), где аббревиатура «ЦПОС» может быть расшифрована как «Цифровой Процессор Обработки Сигналов» - т.е. сокращенно ЦПОС. Платформа «МУЛЬТИКОР» [1-16] - это комплекс современных аппаратно-программных средств проектирования СБИС и систем на их основе. В состав платформы входит обширная библиотека для отечественных и зарубежных фабрик, включающая около 40 цифровых и аналоговых IP ядер в виде «Soft Cores», «Hard Cores» и «FPGA-дизайнов», объединяемых в «систему на кристалле (СнК)» на основе наиболее популярной в мире стандартной системы внутренних шин AMBA. Библиотеки платформы постоянно пополняются за счет ядер, проектируемых разработчиками НПЦ «ЭЛВИС» и партнерами фирмы. Макробиблиотеки и библиотеки IP - ядер разрабатываются таким образом, что они совместимы с лучшими зарубежными электронными фабриками. Это допускает изготовление первых образцов ИМС за рубежом с последующим изготовлением в России. При этом все проекты остаются закрытыми для зарубежного изготовителя. Стандартный подход к построению СнК на базе шин АМВА позволяет разработчикам микросхем (ИМС) на базе платформы эффективно интегрировать, наряду с собственными библиотеками, также и ядра, разработанные ведущими отечественными центрами проектирования. Основополагающим подходом в такой стратегии проектирования является использование ранее разработанных и верифицированных функционально законченных блоков, которые извлекаются из базы системы проектирования и повторно используются для разработки ИМС. Такие повторно используемые блоки называются IP-ядрами (IP - Intellectual-Property reused cores), а платформа «МУЛЬТИКОР», основанная на таком подходе, является IP-ядерной. Микросхемы сигнальных контроллеров МС-0226/MC-0226G спроектированы отечественным дизайн - центром ГУП НПЦ «ЭЛВИС» по техническому заданию НИИСИ РАН при участии специалистов центров проектирования «АНГСТРЕМ-М» (топологическое проектирование) и «АНГСТРЕМСБИС» (разработка блока PLL). Изготовление выполняется по 0.25-мкм/5 металлов/3.3В технологии на зарубежной фабрике с топологического уровня. Чипы содержат внутри по три процессорных ядра, занимают площадь кремния, чуть превышающую 12 мм по линейному размеру, имеют интеграцию свыше 26 млн. транзисторов и обеспечивает пиковую производительность 1440 MFLOPs. Микросхемы ЦПОС-02/МЦОС предназначены для применения в следующих приложениях: Радиолокационные и гидроакустические системы; Графические ускорители; Телекоммуникации и мультимедиа: базовые станции, DVB - приемники и т.д.; Сигнальная обработка: БПФ, фильтрация, корреляция, быстрая свертка; Управление объектами с использованием высокоточных адаптивных методов; Системы промышленного контроля; Высокоточная обработка сигналов и данных. 2. Архитектура микросхемы. В качестве трех процессоров «системы-на-кристалле» (СнК) ЦПОС-02 содержит 32-разрядный центральный процессор (CPU - Central Processing Unit) и два высокопроизводительных процессоров-акселераторов для цифровой обработки сигналов (DSP - Digital Signal Processing) с плавающей/фиксированной точкой, обеспечивающий обработку информации с переменными форматами данных от битовых форматов до стандартных форматов данных с плавающей точкой в формате IEEE754. 249 Все три процессора работают независимо друг от друга (каждый по своей собственной программе) и вследствие этого представляют систему на кристалле MIMD - архитектуры (MIMD - Multiple Instructions Multiple Data). ЦПОС-02 сочетает в себе лучшие качества двух классов приборов: микроконтроллеров и цифровых процессоров обработки сигналов, что особенно важно для встраиваемых применений, когда приходится решать в рамках ограниченных габаритов одновременно обе задачи: управления и высокоточной обработки информации, включая сигналы, изображения и графическую информацию. В состав ЦПОС-02 входят следующие основные узлы и компоненты: CPU - центральный процессор на основе RISC-ядра; CRAM - двухпортовая оперативная память центрального процессора; DSP0, DSP1 - сопроцессоры цифровой обработки сигналов с плавающей и фиксированной точкой; MPORT - порт внешней памяти; PMSC (PCI Master-Slave controller) - контроллер PCI; ICTR - контроллер прерываний;LPORT0:LPORT3 - линковые порты (совместимые с ЦПОС SHARC 21160N, ADI); UART - универсальный асинхронный порт; ICACHE - кэш программ центрального процессора; IT - интервальный таймер; WDT - сторожевой таймер; RTT - таймер реального времени; DMA контроллер прямого доступа в память; LportCh - каналы DMA линковых портов; MemCh - каналы DMA типа память-память; PMCh, PSCh- каналы DMA контроллера PCI; CDB[31:0] - шина данных CPU; JTAG - отладочный порт; SWITCH- коммутатор; PLL - узел фазовой автоподстройки частоты (умножитель частоты); A[31:0] - шина адреса порта внешней памяти; D[63:0] - шина данных порта внешней памяти; OnCD - встроенные средства отладки программ; JTAG - отладочный порт. Микросхема содержит около 3 Мбит внутренней памяти, периферийные SHARC - совместимые линки и последовательные порты, порт UART. СБИС ЦПОС-02 реализована на основе трех типов программируемых интеллектуальных ядер из библиотеки платформы «МУЛЬТИКОР»: Во-первых, это процессорное RISC - ядро RISCore32™, поддерживающее архитектуру MIPS32™, которое реализует функции топ - контроллера «системы на кристалле» и обеспечивает основу для использования стандартного С - компилятора. Во-вторых, это два программируемых DSP ядра, имеющие общее поле регистровой памяти, c плавающей и фиксированной точкой и с уровнем производительности по плавающим операциям, который лидирующие зарубежные фирмы демонстрировали на мировом рынке всего лишь какихнибудь пару-тройку лет назад. Микросхемы конкурируют по производительности DSP - ядра с рядом 16(32)-разрядных процессоров обработки сигналов разработки ADI и TI, но имеет в своем составе стандартное RISC -ядро, что увеличивает ее функциональность. В-третьих, архитектура микросхемы по организации потоков данных и инструкций поддерживает пиковую производительность на большинстве реальных задач спектрально-корреляционной и фильтровой обработки. Для этого в микросхеме имеется многоканальный интеллектуальный контроллер прямого доступа (DMA) с поддержкой режимов самосинхронизации ресурсов микросхемы и 32-разрядный по данным порт внешней памяти со встроенным SDRAM/FLASH/SRAM/ROM контроллером. CPU имеет доступ ко всем устройствам ЦПОС-02. Ключевым элементом контроллера является коммутатор. Он выполнен в соответствии со спецификацией AMBA AXI Protocol (AXI - Advanced eXtensible Interface) [17]. Коммутатор обеспечивает передачу данных между любым исполнительным устройством (Slave) и любым задатчиком (Master). При этом процесс передачи данных между любыми парами Slave Master выполняется параллельно и без конфликтов. Исполнительными устройствами являются блоки внутренней памяти, (CRAM, память DSP0-DSP3) или любая внешняя память, доступная через MPORT. Задатчиками могут быть CPU, каналы DMA линковых портов, каналы DMA типа память-память и каналы DMA контроллера PCI. В состав системы на кристалле микросхемы ЦПОС-02 в качестве DSP-сопроцессоров включены два одинаковых IP- ядра из IP-ядерной библиотеки платформы «МУЛЬТИКОР», называемые ELcore-26™ (ELcore = ELVEES’s core). Каждое из них имеет гарвардскую архитектуру с внутренним параллелизмом по потокам обрабатываемых данных типа 2SIMD (SIMD-Single Instructions, Multiple Data - «один поток инструкций, множественные потоки данных»), типичную для ЦПОС, и предназначено для высокоскоростной обработки информации в форматах с фиксированной и с плавающей точкой. DSP-ядра функционируют под управлением CPU и расширяют его возможности по обработке сигналов. Система инструкций DSP обеспечивает программирование всех базовых процедур сигнальной обработки. Описание системы инструкций и дополнительная информация о работе DSP - ядра приведены в [8, 11 и 15]. Система инструкций и гибкие адресные режимы DSP-ядра ELcore-26™ позволяют эффективно реализовать алгоритмы сигнальной обработки. Время выполнения минимизируется за счет использования программного конвейера и высокопроизводительных инструкций, реализующих параллельно несколько вычислительных операций и пересылок. Ядро ELcore-26™ программно совместимо с ядром ELcore-24™ (микросхемы 1892ВМ2Т и 1892ВМ3Т) серии «Мультикор», но имеет более эффективную реализацию внутренней микроархитектуры, что позволяет на 20% улучшить параметры быстродействия (100МГц - рабочая частота для 250 ELcore-24™, в составе микросхемы МС-24 и 120 МГц - для ELcore-26™ в составе микросхемы ЦПОС-02). Для повышения производительности ядра ELcore-26™ используется распараллеливание потоков обработки по SIMD-типу. Это достигается благодаря свойству масштабируемости DSP-ядра ELcore-х6, то есть возможности увеличения числа секций обработки данных (SIMD-секций) от одной (ELcore-16) до двух (ELcore-26), оставаясь в рамках одной системы инструкций и одной среды разработки (платформа «МУЛЬТИКОР»). Таким образом, параллелизм обработки данных в ЦПОС-02 имеет три уровня: на уровне использования двух ядер DSP -акселераторов (MIMD -параллелизм), т.е. несколько потоков команд - несколько потоков данных); на уровне архитектуры каждого DSP-ядра в целом, что определяется наличием двух SIMD-секций в каждом DSP -ядре (SIMD -параллелизм. SIMD - ingle Instructions Multiple Data, т.е. один поток команд - несколько потоков данных); на уровне каждой из SIMD-секций он определяется возможностью выполнения в рамках одной инструкции (т.е. в течение одного командного цикла) нескольких вычислительных операций и пересылок. 3.Функциональные параметры и возможности СБИС. ЦПОС-02 имеет следующие функциональные параметры и возможности: Центральный процессор (CPU): Архитектура - MIPS32; 32-х битные шины передачи адреса и данных; Кэш команд объемом 16 Кбайт: Архитектура привилегированных ресурсов в стиле ядра R4000: Регистры Count/Compare для прерываний реального времени; Отдельный вектор обработки исключений по прерываниям; Программируемое устройство управления памятью: Два режима работы - с TLB (Translation Lookaside Buffer) и FM (Fixed Mapped); 16 строк в режиме TLB. Устройство умножения и деления; JTAG IEEE 1149.1, встроенные средства отладки программ Производительность - 120 млн. оп/сек (здесь и далее параметры производительности приведены при тактовой частоте 120 МГц); Оперативная память центрального процессора (CRAM) объемом 32 Кбайт; 5 внешних запросов прерывания, в том числе немаскируемое прерывание (NMI). Два цифровых сигнальных сопроцессора (DSP0-DSP1), каждый из которых характеризуется следующими возможностями: “Гарвардская” RISC - подобная архитектура с оригинальной системой команд и преимущественно однотактным исполнением инструкций; 2SIMD (Single Instruction Multiple Data) организация потоков команд и данных; Набор инструкций, совмещающий процедуры обработки и пересылки; 3-ступенчатый конвейер по выполнению 32- и 64-разрядных инструкций; Расширенные возможности по динамическому диапазону обрабатываемых данных, позволяющие обрабатывать данные в 8/16/32-разрядных форматах с фиксированной точкой, либо в одном из форматов с плавающей точкой - 24Е8 (стандарт IEEE 754) или 32Е16 (расширенный формат). Обеспечение при этом компромиссного выбора между точностью и производительностью. Аппаратные меры повышения точности и динамического диапазона (блочная плавающая точка; режим насыщения; инструкции преобразования форматов); Аппаратная поддержка программных циклов; Программная совместимость снизу с сигнальными контроллерами 1892ВМ2T и 1892ВМ3T; Память программ PRAM в каждом DSP – ядре - объемом 8 Кбайт (2К 32-разрядных слов); Двухпортовые памяти данных XRAM и YRAM объемом 96 и 32 Кбайт соответственно для каждого; Пиковая производительность обеспечиваемая двумя DSP-ядрами: 1440 млн. оп/с 32-битных операций с плавающей точкой (IEEE 754); 8640 млн. оп/с 8-битных операций с фиксированной точкой; 3840 млн. оп/с 16-битных операций с фиксированной точкой; 1920 млн. оп/с 32-битных операций с фиксированной точкой. Порт внешней памяти (MPORT): Шина данных - 64 разряда, шина адреса - 32 разряда; Поддержка асинхронной памяти типа SRAM, ROM, FLASH; Поддержка синхронной памяти типа SDRAM; Поддержка синхронной статической памяти типа SBSRAM; Программное конфигурирование типа памяти и объема ее сегмента; Программное задание циклов ожидания; Формирование сигналов выборки 4 сегментов памяти; Обеспечение обслуживания 4 внешних прерываний; Перевод SDRAM в режим энергосбережения. 251 Режим обмена Flyby: Режим Flyby используется контроллером DMA (каналы MemCh) для передачи данных между внешним устройством ввода-вывода и внешней памятью (как асинхронной, так и синхронной). Например, контроллер DMA может быть запрограммирован для передачи данных из аналого-цифрового преобразователя в SDRAM. При передаче данных в режиме Flyby ЦПОС-02 отключается от шины данных, и активизирует внешнюю память и внешнее устройство ввода-вывода одновременно. Память управляется как обычно, а устройство ввода-вывода – при помощи сигналов nFLYBY (признак данного режима) и nOE (активизация выходных формирователей устройства ввода-вывода). Каждому каналу MemCh может соответствовать свое устройство ввода-вывода. Контроллер PCI (PMSC - PCI Master-Slave controller): Соответствует спецификации Local Bus Specification. Rev. 2.2; Тактовая частота - до 100 МГц; Разрядность - 32 разряда; Режимы Master и Slave; 2 канала DMA; встроен арбитр с циклически изменяемыми приоритетами запросов. PMSC предназначен для обмена данными между шиной PCI и любой областью внутренней (CRAM и XRAM, YRAM, PRAM любого из ядер DSP1 и DSP2) и внешней памяти ЦПОС-02. Кроме того, PMSC обеспечивает выполнение программного ввода-вывода данных под управлением CPU. PMSC имеет аппаратные средства для организации мультипроцессорных систем. Для обмена данными между PCI и коммутатором в контроллере PMSC имеются два канала DMA: канал PSCh выполняет обмен данными в режиме Slave на PCI. Он настраивается и управляется из шины PCI; канал PMCh выполняет обмен данными в режиме Master на PCI. Он настраивается и управляется как по шине CDB, так и из шины PCI (для целей тестирования). CPU с шиной PCI может выполнять программный ввод-вывод данных через окно размером 16 Мбайт. Периферийные устройства: 12 - канальный контроллер прямого доступа в память (DMA). 4 внешних запроса прямого доступа; Специальные режимы синхронизации. Поддержка 2-мерной и разрядно-инверсной адресации. Режим передачи Flyby, подобный реализованному в ADSP-TS201: внешнее устройство внешняя память; два порта обмена последовательным кодом (SPORT) совместимые с ADSP21160 (разработка фирмы ADI); четыре линковых порта (LPORT) совместимые с ADSP21160. Имеется режим работы в качестве портов ввода-вывода общего назначения (GPIO); универсальный асинхронный порт (UART) типа 16550; 32-разрядный интервальный таймер (IT); 32-разрядный таймер реального времени (RTT); 32разрядный сторожевой таймер (WDT). Дополнительные возможности и особенности: Узел фазовой автоподстройки частоты (PLL) c умножителем/делителем входной частоты; Встроенные средства отладки программ (OnCD); Порт JTAG в соответствии со стандартом IEEE 1149.1; Режимы энергосбережения; Поддержка операционной системы Linux; Возможные варианты корпуса: пластиковые - BGA-416 и металлокерамический (уточняется). 4. Эффективность микросхемы ЦПОС-02 при выполнении типовых процедур обработки сигналов. Прежде всего, следует отметить, что DSP - ядро имеет RISC-подобную архитектуру, с точки зрения реализованного в нем 3-уровневого конвейера. Это обеспечивает выполнение почти всех операций ядра за один такт, кроме двухтактных переходов. С этой точки зрения программирование на ассемблере для DSP-ядра выполняется достаточно быстро и эффективно, что подтверждено практически многими пользователями микросхемы. Конечно, это не исключает использования в перспективе полного C(С++) - компилятора, разрабатываемого для контроллеров «Мультикор». С другой стороны, и сама команда для DSP ядра достаточно емкая, имеет длину 32 или 64 бита и напоминает с этой точки зрения VLIW (Very long instruction word). Так, одна 64-разрядная инструкция для ELcore-26™ может выполнять две пары арифметических (логических) операций любой сложности и две пары пересылок типа регистр-память. Это обеспечивает высокую плотность кодов для различных программ, и позволяет реализовать различные функции обработки сигналов для МС-0226, потратив на это в несколько раз меньше команд (а, значит, и меньшее время), чем для многих DSP - процессоров с «мировым именем». Это обусловлено тем, что сравниваемые DSP имеют, к примеру, или огромную длину конвейера (10-12 уровней, как, к примеру, знаменитый процессор TigerSHARC T201, разработки ADI) , или низкую плотность кода. К примеру, длина кода для процедуры FFT- 256 (комплексные 16-разрядные форматы данных и коэффициентов) в 8 раз короче для SISD - ядра ELcore-16™ (менее 1000 тактов), чем, к примеру, для DSP - ядра C54, разработки TI (8542 такта). А ведь за то же время одно 2SIMD ядро ELcore-26™ может выполнять одновременно 2 таких преобразования, т.е. в эквиваленте выполняя эту процедуру в два раза быстрее по сравнению с микросхемой 1892ВМ3Т (МС-12), т.е. более чем в 16 раз быстрее по количеству тактов, чем ядро C54. 252 Сверх этого, ядро ELcore-26™ поддерживает дважды распараллеленную организацию потоков данных по 2SIMD - типу. Это достигается благодаря свойству масштабируемости DSP-ядра ELcore-х6, то есть возможности увеличения числа секций обработки данных (SIMD-секций) от одной (ELcore-14™ для микросхемы 1892ВМ3Т - МС-12) до двух (ELcore-24™ или ELcore-26™), оставаясь в рамках одной системы инструкций и одной среды разработки (платформа «МУЛЬТИКОР»). Таким образом, параллелизм обработки данных в ядре ELcore-26™ имеет два уровня: на уровне архитектуры DSP-ядра в целом он определяется наличием нескольких SIMD-секций; на уровне каждой из SIMD-секций он определяется возможностью выполнения в рамках одной инструкции (т.е. в течение одного командного цикла) нескольких вычислительных операций и пересылок. Система инструкций и гибкие адресные режимы DSP-ядра ELcore-26™ позволяют эффективно реализовать алгоритмы сигнальной обработки. Время выполнения минимизируется за счет использования программного конвейера и высокопроизводительных инструкций, реализующих параллельно несколько вычислительных операций и пересылок. И, наконец, DSP - ядро обрабатывает информацию с переменными форматами данных от битовых форматов до стандартных форматов данных с плавающей точкой в формате IEEE754. В табл.1 приведены результаты сравнения параметров быстродействия серийных микросхем 1892ВМ2Т (МС-24), перспективной микросхемы МС-0226 или ЦПОС-02 (ожидаемые тестовые образцы - первое полугодие 2005г.) и зарубежных микросхем ЦПОС. Таблица 1 Сравнительные характеристики сигнальных контроллеров серии “Мультикор”1892ВМ2Т (МС-24) («ЭЛВИС») и МС-0226 (ЦПОС-02) и наиболее высокопроизводительных зарубежных DSP-процессоров Фирма Процессор Тактовая частота, МГц Технология, мкм Пиковая производительность, форматы: 16-b фиксированная точка (в Mop/s) 32-b плавающая точка (в MFLOPs/s) 8-b фиксированная точка (в Mop/s) КИХ-фильтр, 35 отводов, 1024 входных отсчета (в мкс): фиксированная точка 16*16+32 фиксированная точка 8*8+32 32-b плавающая точка FFT-1024, комплексное (в мкс): блочная плавающая точка (16+j16) 32b плавающая точка FFT-256, комплексное (в мкс): блочная плавающая точка (16+j16) DCT-8x8, фиксированная точка 16b (в мкс): ACS-операции (в Mop/s): (для декодера Витерби, 16b) ЭЛВИС MC-24 MC-0226 100 120 0.25 0.25 TI C6701 166 0.18 C6416 600 0.13 ADI TS201 BF53 600 600 0.13 0.13 1600 600 3600 3840 1440 8640 4800 9600 3600 99.8 50.4 195.4 41.6 21 81.4 25.7 8.4 393 58 107 24.2 44.6 160 11 7.75 16.8 11.2 4.7 5.3 0.6 200 0.3 480 <0.5 1000 3360 На рис.1 приведена типовая схема применения ЦПОС-02. Использованы следующие обозначения: FLASH - постоянное запоминающее устройство типа FLASH; SDRAM - синхронное динамическое оперативное запоминающее устройство (ОЗУ); SRAM - статическое ОЗУ; Interrupt - запросы прерывания; DAC/ADC - цифро-аналоговые и аналого-цифровые преобразователи; LINK DEVICE- устройства, подключаемые к линковым портам; RS-232 Buffer - приемопередатчики RS-232; Config - схема задания конфигурации; RESET - узел формирования сигнала установки исходного состояния. Порт внешней памяти обеспечивает подключение без дополнительной логики статической оперативной памяти типа SRAM, динамической памяти типа SDRAM или Flash. Конфигурационные регистры порта внешней памяти позволяют гибко настраивать такие параметры, как число тактов ожидания, размер банка памяти и его базовый адрес, тип памяти, размер страницы SDRAM. Это позволяет проектировать компактные встроенные устройства. На базе типовой схемы применения разработан отладочный комплект MC-0226ЕМ, в состав которого входят: Отладочный модуль для микросхемы MC-0226 серии «Мультикор»; Кабель связи 253 отладочного модуля с параллельным портом IBM PC; кабель связи отладочного модуля с портом RS232 IBM PC; Сетевой адаптер с выходным напряжением +12 В; ответная часть для двух разъёмов типа IEEE 1386; CD c Интегрированной средой разработки и отладки программ MCStudio™ и технической документацией на микросхему и ПО; Библиотека прикладных программ для DSP процессора и МС-0226 в целом (лицензируется при поставке как опция). Config RESET JTAG D<63:0> nWRH<3:0> nWRL<3:0> nRDH,nRDL nCS<4:0> nACK XTI XTO RTCXTI PLL_EN BYTE nRST ADDR DATA nCS nRD ADDR DATA RAS CAS WE DQM CKE BA CLK nCS SRASH,SRASL SCASH,SCASL SWEH,SWEL DQM<7:0> SCLK BA<1:0> A10 CKE TCK TDI TDO TMS TRST LINK DEVICE0 LDAT0<7:0> LACK0 LCLK0 . . . . . . LINK DEVICE3 LDAT3<7:0> LACK3 LCLK3 ADDR DATA nWR nRD nCS nFLYBY<3:0> nOE<3:0> nWEH,nWEL nDMAR<7:0> FLASH SDRAM (128MB) SRAM (4MB) DATA nFLYBY nOE DAC/ADC nWE nRD nDMAR<3:0> Analog Input/output DATA<63:0> Real Time Clock 32kHz A<31:0> ADRESS<31:0> Cristall 10MHz ЦПОС-02 IRQ<3:0> NMI CONTROL 4 Interrupt SIN SOUT nCTS nRTS nDTR nDSR AD<31:0> nC/BE<3:0> nFRAME nTRDY nIRDY nSTOP PAR PERR nDEVSEL IDSEL nREQ nGNT RS-232 Buffer Interface RS-232 PCI BUS Рис. 1. Типовая схема применения ЦПОС-02 Следует отметить, что микросхемы МС-0226/0226G полностью комплексируются без дополнительного вспомогательного оборудования с другими сериями импортозамещающих и экспортнопригодных микросхем разработки НПЦ «ЭЛВИС». Среди них: Серия программируемых сигнальных контроллеров «Мультикор» для применений от мобильных систем связи до высокопроизводительных радарных и гидроакустических комплексов, а также криптографических систем; 254 Серия программируемых аналого - цифровых ИМС «Мультифлекс» для цифрового преобразования частоты в системах ввода и предобработки сигналов для фазированных антенных решеток, радаров и систем связи; Серия программируемых элементов системного сопряжения «Мультикор - конструктор» для ИМС серий «Мультикор», обеспечивающая новую концепцию реконфигурируемых встраиваемых систем; Серия аналого - цифровых микросхем «Мультимикст»; «ФлексРадио» - перспективная серия ИМС для СВЧ трактов широкополосных радарных и связных систем. 5. Средства отладки программного обеспечения. Для полного цикла разработки и отладки программ для микросхем ЦПОС-02/МЦОС разработчикам предлагается интегрированная среда проектирования программного обеспечения MCStudio™ [9,12-16], которая представляет собой интегрированную среду (IDE) разработки и отладки программного обеспечения для изделий, построенных на базе микросхем ЦПОС-02/МЦОС, а также отладочный модуль. MCS является кросс - системой и функционирует на инструментальной машине IBM PC в среде Linux. Концепция интегрированной среды и инструментального программного обеспечения для микросхем серии «Мультикор» представлена на сайте фирмы [1], а среда MCStudio™ вместе с документацией на микросхему поставляется компанией «ЭЛВИС». Инструментальное программное обеспечение ЦПОС-02 (MC-0226) базируется на архитектуре MIPS32. Вследствие этого, оно поддерживает большой объем свободно распространяемого программного обеспечения для этой архитектуры. Интегрированная среда проектирования включает: среду разработки программ для RISC - и DSP - ядер; среду отладки программ в исходных текстах, исполняемых на программном симуляторе, и отладчик для работы с платой отладочного модуля (МС-0226ЕМ) для микросхемы ЦПОС-02 или целевым устройством через JTAG; средства программного моделирования; возможность доступа пользователю ко всем инструментам через один интерфейс. Среда разработки программ для RISC - ядра включает: компилятор с языка Си с препроцессором; ассемблер с препроцессором; дисассемблер; линковщик; библиотекарь; утилиты подготовки исполняемого кода. Среда разработки программ для ЦПОС - ядра включает: ассемблер с препроцессором; дисассемблер; линковщик; библиотекарь; утилиты подготовки исполняемого кода. Микросхемы ЦПОС-02/МЦОС имеют встроенные аппаратные средства отладки OnCD (On Chip Debugger), доступ к которым производится через JTAG- порт, реализованный по стандарту IEEE Standard Test Access Port and Boundary-Scan Architecture IEEE Std 1149.1-2001. OnCD предоставляет возможность пользователю по заданным через JTAG-порт условиям остановить CPU, при этом по завершении выполнения текущей команды останавливаются все активные компоненты такие, как DMA. После останова CPU имеется возможность с помощью OnCD визуализировать (или изменить) состояние всех архитектурных элементов, которые проецируются во всём адресном пространстве памяти системы, и продолжить выполнение программы. Перечисленные условия останова CPU, возможность в режиме отладки выполнения команды CPU по одному такту продвижения команды в конвейере, а также доступность всего адресного пространства в состоянии останова, даёт возможность использовать OnCD и JTAG-порт для построения эффективных отладчиков программ и систем. OnCD имеет программный интерфейс (JTAG-отладчик) с интегрированной средой разработки и отладки программ. Это позволяет проводить разработку программного обеспечения в реальном масштабе времени. В качестве дополнительной опции для микросхемы МС-0226 в составе отладочного модуля МС-0226EM может быть портировано ядро операционной системы Linux версий 2.4.17, 2.4.25, 2.6.5, а также ОС реального времени (ОС РВ), совместимой с QNX 6.3. Предполагается, что данная микросхема будет также обеспечена сертифицированной отечественной ОС реального времени, типа ОС РВ «Багет», разработанной НИИСИ РАН. Для микросхем МС-0226/МС-0226G, входящих в серию «Мультикор», доступен большой объем прикладного программного обеспечения по выполнению вычислительных функций, обработке сигналов и изображений, связных и мультимедийных компонент. Библиотека прикладных программ (поставляется дополнительно) включает: элементарные математические функции; операции над матрицами; алгоритмы БПФ комплексных и действительных чисел; алгоритмы быстрой свертки и корреляции посредством БПФ (перекрытие с накоплением); рекурсивная и Нерекурсивная фильтрация; адаптивная фильтрация. Для разработчика РЭА обеспечивается возможность применения новых алгоритмов принятия решений в CPU на основе параллельно выполняемых процедур библиотеки адаптивного анализа и обработки сигналов в DSP, что реализуется в пределах одной и той же микросхемы. Для этих целей разработаны методы применения и библиотеки RLS/LNS алгоритмов на базе микросхем серий «МУЛЬТИКОР», в частности для адаптивных антенных решеток. Разработана графическая библиотека, содержащая около 50 функций OpenGL. 255 6. Заключение. Импортозамещающие и экспортопригодные микросхемы сигнальных контроллеров МС-0226(ЦПОС-02) и МС-0226(ЦПОС-02), реализованные как трехпроцессорные «системы на кристалле», на сегодняшний день являются самыми производительными и интегральными отечественными серийными микросхемами ЦПОС. Они легко интегрируются с другими микросхемами серий «Мультикор», «Мультифлекс», «Мультимикст» и «ФлексРадио» разработки НПЦ «ЭЛВИС ». Реализация серии данных микросхем позволит обеспечить элементной базой отечественную радиоэлектронную аппаратуру как для микроминиатюрных, так и для высокопроизводительных систем многоцелевого назначения обработки информации. Благодаря наличию высокоскоростных линков и встроенных PCI -контроллеров на базе данных микросхем будут реализованы распределенные и параллельные системы сбора и обработки информации самого широкого применения. ЛИТЕРАТУРА 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. http://www.elvees.ru Александров Ю.Н., Беляев А.А., Глушков А.В., Грибов Ю.Н., Никольский А.В., Петричкович Я.Я., Солохина Т.В. Новая отечественная платформа СБИС «МУЛЬТИКОР» для высокоточной скоростной обработки информации и управления объектами // Цифровая обработка сигналов. - 2001. - № 3. - С. 15-19. Петричкович Я.Я., Солохина Т.В. SoC серии «Мультикор»- первый шаг и положительная динамика развития // Компоненты и технологии. - 2003. - №5. - C. 104-106. Петричкович Я.Я., Солохина Т.В. Цифровые сигнальные контроллеры «МУЛЬТИКОР» - новые отечественные серии систем на кристалле // Доклады 6-й Международной конференции «Цифровая обработка сигналов и ее применения (DSPA-2004)». Москва. 31 марта - 2 апреля 2004. - Т. 1. - С. 8-15. Солохина Т.В., Петричкович Я.Я., Глушков А.В., Беляев А.А., Грибов Ю.И., Никольский В.Ф., Силин В.А., Алексеев М.Н., Александров Ю.Н. Время кентавров: Микросхемы серии Мультикор11хх (МС-11хх) для встраиваемых и мобильных применений // Chip News. - 2002. - № 8(71). С. 10-17. Солохина Т.В., Петричкович Я.Я., Глушков А.В., Александров Ю.Н., Глушков В.Д., Семенович А.М., Беляев А.А., Грибов Ю.И., Никольский В.Ф., Силин В.А., Алексеев М.Н., Бабичевский С.А., Федин В.А. Мультикор-12S - сигнальный контроллер с плавающей точкой для высокоточных встраиваемых применений // Chip News. - 2003. - № 8(81). - С. 4-15. Солохина Т.В., Петричкович Я.Я., Александров Ю.Н., Герасимов Ю.М., Заболотнов И.В., Алексеев М.Н., Беляев А.А., Грибов Ю.И., Глушков В.Д., Никольский В.Ф., Силин В.А., Крымов А.А., Тимофеев О.А., Миронова Ю.В., Перекин Р.Н., Кучинский А.В., Чупринов А.А., Грачев Р.А. Микросхемы базовых серий «МУЛЬТИКОР». Сигнальный микроконтроллер 1892ВМ2Т (МС-24). Часть1 // Chip News. - 2005. - № 2(95). - С. 20-31. Солохина Т.В., Петричкович Я.Я., Александров Ю.Н., Герасимов Ю.М., Заболотнов И.В., Алексеев М.Н., Беляев А.А., Грибов Ю.И., Глушков В.Д., Никольский В.Ф., Силин В.А., Крымов А.А., Тимофеев О.А., Миронова Ю.В., Перекин Р.Н., Кучинский А.В., Чупринов А.А., Грачев Р.А. Микросхемы базовых серий «МУЛЬТИКОР». Сигнальный микроконтроллер 1892ВМ2Т (МС-24). Часть 2 // Chip News. - 2005. - № 3(96). - С. 20-26. Солохина Т.В., Петричкович Я.Я., Глушков А.В., Крымов А.А., Никольский В.Ф., Александров Ю.Н. и др. Интегральная среда разработки и отладки программ для модулей сигнальных контроллеров на базе ИМС платформы МУЛЬТИКОР» // Chip News. - 2002. - № 9(72). - С. 46-55. Процессорное ядро RISCore32. Система команд // ГУП НПЦ «ЭЛВИС». - 2004. DSP-ядро ELcore_x6. Система инструкций // ГУП НПЦ «ЭЛВИС». - 2004. Интегрированная среда разработки и отладки программ MCStudio™. Установка среды MCStudio™. Руководство системного программиста // ГУП НПЦ «ЭЛВИС». - 2004. Интегрированная среда разработки и отладки программ MCStudio™. Описание пользовательского интерфейса. Руководство оператора // ГУП НПЦ «ЭЛВИС». - 2004. Интегрированная среда разработки и отладки программ MCStudio™. Руководство программиста // ГУП НПЦ «ЭЛВИС». - 2004. Интегрированная среда разработки и отладки программ MCStudio™. Инструменты ядра DSP. Руководство оператора // ГУП НПЦ «ЭЛВИС». - 2004. Интегрированная среда разработки и отладки программ MCStudio™. Инструменты ядра RISC. Руководство оператора // ГУП НПЦ «ЭЛВИС». - 2004. AMBA Specification (Rev 2.0) // http://www.arm.com. 256