Синтез комбинационных цифровых устройств

advertisement

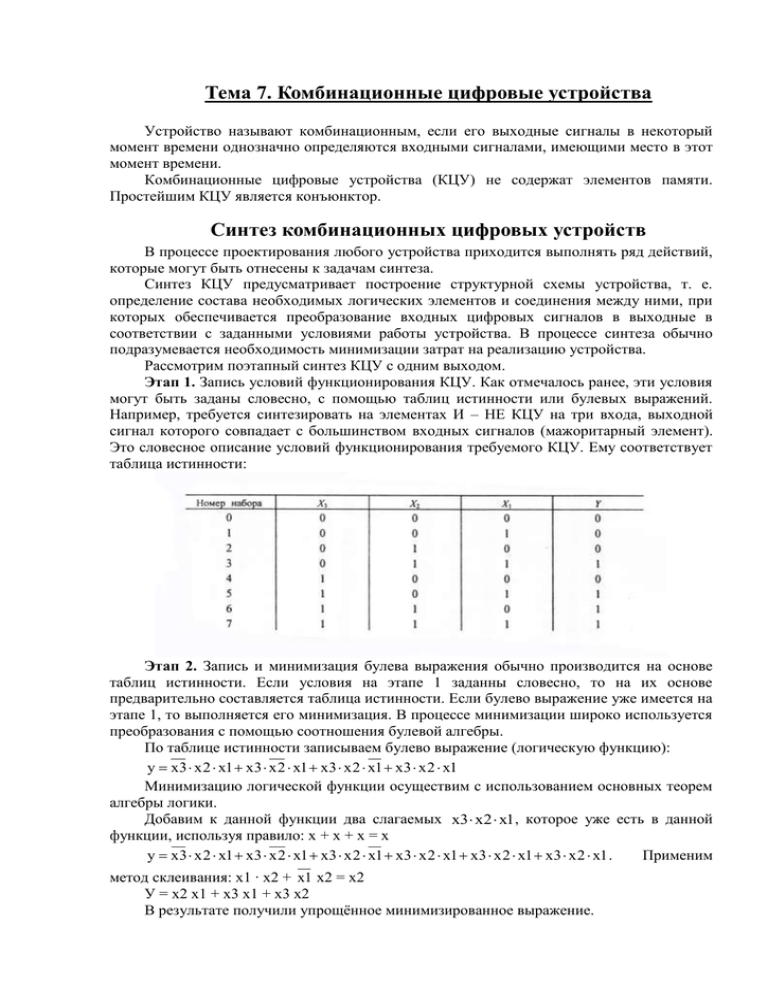

Тема 7. Комбинационные цифровые устройства Устройство называют комбинационным, если его выходные сигналы в некоторый момент времени однозначно определяются входными сигналами, имеющими место в этот момент времени. Комбинационные цифровые устройства (КЦУ) не содержат элементов памяти. Простейшим КЦУ является конъюнктор. Синтез комбинационных цифровых устройств В процессе проектирования любого устройства приходится выполнять ряд действий, которые могут быть отнесены к задачам синтеза. Синтез КЦУ предусматривает построение структурной схемы устройства, т. е. определение состава необходимых логических элементов и соединения между ними, при которых обеспечивается преобразование входных цифровых сигналов в выходные в соответствии с заданными условиями работы устройства. В процессе синтеза обычно подразумевается необходимость минимизации затрат на реализацию устройства. Рассмотрим поэтапный синтез КЦУ с одним выходом. Этап 1. Запись условий функционирования КЦУ. Как отмечалось ранее, эти условия могут быть заданы словесно, с помощью таблиц истинности или булевых выражений. Например, требуется синтезировать на элементах И – НЕ КЦУ на три входа, выходной сигнал которого совпадает с большинством входных сигналов (мажоритарный элемент). Это словесное описание условий функционирования требуемого КЦУ. Ему соответствует таблица истинности: Этап 2. Запись и минимизация булева выражения обычно производится на основе таблиц истинности. Если условия на этапе 1 заданны словесно, то на их основе предварительно составляется таблица истинности. Если булево выражение уже имеется на этапе 1, то выполняется его минимизация. В процессе минимизации широко используется преобразования с помощью соотношения булевой алгебры. По таблице истинности записываем булево выражение (логическую функцию): y x3 x2 x1 x3 x2 x1 x3 x2 x1 x3 x2 x1 Минимизацию логической функции осуществим с использованием основных теорем алгебры логики. Добавим к данной функции два слагаемых x3 x2 x1 , которое уже есть в данной функции, используя правило: х + х + х = х y x3 x2 x1 x3 x2 x1 x3 x2 x1 x3 x2 x1 x3 x2 x1 x3 x2 x1 . Применим метод склеивания: х1 ∙ x2 + x1 x2 = x2 У = x2 x1 + x3 x1 + x3 x2 В результате получили упрощённое минимизированное выражение. Этап 3. Запись минимизированной структурной формулы в заданном базисе. Так как реализация КЦУ на ИС предусматривает широкое использование элементов И – НЕ, ИЛИ – НЕ, И – ИЛИ – НЕ, то часто возникает необходимость соответствующих преобразований структурных формул с учётом заданной элементной базы. Для перехода к заданному базису И – НЕ поставим два знака инверсии над правой частью формулы и применим к ней правило де Моргана. В результате получим структурную формулу в следующем виде: Y X 2 X1 X3X1 X3X 2 Этап 4. составления структурной схемы, т. е. изображения нужных логических элементов и связей между ними. Структурная схема синтезированного КЦУ приведена на рисунке: Типовые комбинационные цифровые устройства. При построении сложных устройств широко применяются не только отдельные логические элементы, реализующие элементарные булевы функции, но и их комбинации в виде типовых структур, выполняемых как единое целое в виде интегральных микросхем. На входе таких структур могут подаваться информационные логические сигналы и сигналы управления. Последние могут определять, например, порядок передачи информационных входных сигналов на выход или играть роль сигналов синхронизации. Во многих случаях, особенно при использовании в устройствах выходных цепей с тремя состояниями, в качестве сигналов синхронизации выступают сигналы «Выбор микросхемы» (CS). Наличие активного значения такого сигнала управления (в одних микросхемах это логический нуль, в других – логическая единица) разрешает устройству выполнение заданных функций, отсутствие его переводит схему в «невыбранное» состояние, при котором она обрабатывает информацию, а её выходы отключены от нагрузки. Внутренняя структура КЦУ часто приводится в справочниках. Для разработчика важно знать таблицу истинности, принцип преобразования входных сигналов в выходные. Мультиплексоры и демультиплексоры Мультиплексором называются комбинационные устройство, обеспечивающее передачу в желаемом порядке цифровой информации, поступающей по нескольким входам на один выход. Мультиплексоры обозначают через MUX (от англ.multiplexor), а также через MS (от англ. Multiplexor selector). Схематически мультиплексор можно изобразить в виде коммутатора, обеспечивающего подключение одного из нескольких входов (их называют информационными) к одному выходу устройства. Кроме информационных входов в мультиплексоре имеются адресные входы и, как правило, разрешающие (стробирующие). Сигналы на адресных входах определяют, какой конкретно информационный канал подключен к выходу. Если между числом информационных входов n и число адресных входов m действуют соотношение n = 2m , то такой мультиплексор называют полным. Если n < 2m , то мультиплексор называют неполным. Рассмотрим функционирование двухвходового мультиплексора (2 → 1), который условно изображён в виде коммутатора, а состояние его входов Х1, Х2 и выхода Y приведено в таблице: Исходя из таблицы, можно записать следующее уравнение: Y = X1 ∙ A + X2 ∙ A, Реализация такого устройства и его УГО приведены ниже: Количество мультиплексируемых входов называется количеством каналов мультиплексора, а количество выходов называется числом разрядов мультиплексора. Число каналов мультиплексоров, входящих в стандартные серии, составляет от 2 до 16, а число разрядов – от 1 до 4, при чём чем больше каналов имеет мультиплексор, тем меньше у него разрядов. Управление работой мультиплексора (выбор номера канала) осуществляется с помощью входного кода адреса. Например, для 4 – канального мультиплексора необходим 2 – разрядный управляющий (адресный) код, а для 16 – канального - 4 разрядный код. Разряды кода обозначаются 1, 2, 4, 8 или А0, А1, A2, А3. Мультиплексоры бывают с выходом 2С и с выходом 3С. Выходы мультиплексоров бывают прямыми и инверсивными. Выход 3С позволяет объединить выходы мультиплексоров с выходами других микросхем, а также получать двунаправленные и мультиплексированные линии. УГО мультиплексора, имеющего 8 информационных входов, 3 адресных входа, вход разрешения V, и два выхода (прямой инверсный) показано на рисунке: При V = 1 мультиплексор блокируется. Вход разрешения V используется для расширения функциональных возможностей мультиплексора, например, позволяет увеличивать число коммутируемых информационных входов: Два 8 – канальных мультиплексора объединены в 16 – ти канальный. Старший разряд А3 выбирает один из 2 – ух мультиплексоров. Расширение разрядности мультиплексоров в общем случае реализуется их каскадным включением: Здесь «Мультиплексорное дерево» содержит четыре четырёхвходовых мультиплексора MUX1 – MUX4 c запараллеленными адресными входами А0, А1, которыми одновременно выбирается один из входов всех четырёх элементов, а мультиплексор MUX5 кодом на адресных входах А2, А3 выбирает один из выходов Y0 – Y3. Таким образом, четырёхразрядный код на входах А0 – А3соединяется с входом только один из 16 входов (16 = 2 4 ) D0 – D15. Демультиплексором называют устройство, в котором сигналы с одного информационного входа поступают в желаемой последовательности по нескольким выходам в зависимости от кода на адресных шинах. Таким образом, демультиплексор в функциональном отношении противоположен мультиплексору. Демультиплексоры обозначают через DMX или DMS: При использовании КМОП – технологии можно построить двунаправленные ключи, которые обладают возможностью пропускать ток в обоих направлениях и передавать не только цифровые, но и аналоговые сигналы. Благодаря этому можно строить мультиплексоры – демультиплексоры, которые могут использоваться либо как мультиплексоры, либо как демультиплексоры. Мультиплексоры – демультиплексоры обозначаются через MX. . Шифраторы (кодеры) и дешифраторы (декодеры) Шифратор – это комбинационное устройство, преобразующее десятичные числа в двоичную систему счисления, причём каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определённому двоичному коду. Шифратор иногда называют «кодером» (от англ. Coder) и используют, например, для перевода десятичных чисел, набранных на клавиатуре. Функции шифратора показаны на рисунке: УГО и таблица истинности шифратора приведены на рисунке: Из таблицы видно, что на выходах 1, 2, 4, 8, формируется двоичный код номера входной линии (x0, х1 …… x9), на которую приходит входной сигнал. Одновременное поступление нескольких входных сигналов приводит к неопределённости на выходах. Дешифратором называется комбинационное устройство, преобразующее n – разрядный двоичный код в логический сигнал, появляющийся на том выходе, десятичный номер которого соответствует двоичному коду. Функции дешифратора показан на рисунке: УГО и таблица истинности дешифратора показаны на рисунке: Активным всегда являются только один выход. Легко заметить, что активируется тот выход, адрес которого установлен на входах. Дешифраторы широко используются в цифровой аппаратуре. Аналоговый коммутатор с цифровым управлением Аналоговый коммутатор служит для последовательной обработки аналоговых сигналов. Схема и УГО аналогового коммутатора показаны на рисунке: Аналоговый коммутатор содержит ключи, на вход каждого из которых (Д0, Д1 …Д7) действует напряжение аналогового сигнала. Управление ключами производится дешифратором, на входы которого поступает цифровой код. Для коммутации на выход линии D0 на адресных входах устанавливают код À 0 = 0, À1 = 0, À 2 = 0, для аналогичного соединения линии D1 – код À 0 = 0, À1 = 0, À 2 = 0 и т. д. Для периодического опроса источников сигналов адресные входы коммутатора подключают к выходам счётчика, на которых циклически изменится код при поступлении входных импульсов. Мультиплексоры – демультиплексоры При использовании КМОП – технологии можно построить двунаправленные ключи, которые обладают возможностью пропускать ток в обоих направлениях: UУПР Сопротивление КМОП – транзистора в открытом состоянии составляет от 10 Ом до 1 кОм, сопротивление в закрытом состоянии ограничивается токами утечки, которые составляют 0,1 …. 100 нА, время включения ключа составляет 3 ….5 нс. Двунаправленные ключи могут передавать цифровые и аналоговые сигналы. Благодаря этому можно строить мультиплексоры – демультиплексоры: Показанная на рисунке микросхема содержит два четырёхвходовых мультиплексора, которые могут использоваться как демультиплексоры (МХ – ДМХ). На схемах они обозначаются буквами МХ. Микросхема содержит один общий инверсный вход Е разрешения (стробирования) и два общих адресных входа 1 и 2. При логической 1 на входе разрешения выходы отключаются от информационных входов и переходят в высокоипедансное состояние. При активизации входа разрешения, т. е. при подаче на него логического 0, происходит соединение одного из информационных входов (в соответствии с кодом на адресных входах) с выходом микросхемы. Поскольку это состояние происходит при помощи двунаправленных ключей на КМОП – транзисторах, то сигнал может передаваться как со входов на выход (режим мультиплексора), так и с выхода на входы ( режим демультиплексора). Кроме того, передаваемый сигнал может быть как аналоговым, так и цифровым. Преобразователи кодов Преобразователи кодов служат для преобразования входных двоичных кодов в выходные двоично–десятичные и наоборот. Находят применение в схемах многоразрядной десятичной индикации. На схемах обозначаются буквами X/Y. Например, микросхема к155пп5 представляет преобразователь двоично-десятичного кода, в код семисегментного индексатора: 1, 2, 4, 8 – информационные входы. 1, 2, 3, 4, 5, 6, 7 – выходы для управления светодиодной матрицей (показана справа) Вход Е используется либо для осуществления индикации (подачей на него логического 0), либо для гашения индикатора (подачей на него логической 1). Микросхема имеет выход ОК. Работа преобразователя осуществляется в соответствии с таблицей истинности: Сегмент светится, если на него подаётся логическая 1. Цифровые компараторы (компараторы кодов) Цифровые компараторы выполняют сравнение двух чисел, заданных в двоичном коде. Они могут определять равенство двух двоичных чисел А и В с одинаковым количеством разрядов либо вид неравенства А > В или А < В. Цифровые компараторы имеют три выхода: Fa > b, Fa = b, Fa < b. Таблица истинности одноразрядного компаратора приведены ниже: По известным правилам можно записать логические функции, характеризующие соотношение одноразрядных чисел а и в: Fa > b = а ∙ b Fa = b = аb + a b Fa < b = a b Схема одноразрядного компаратора, реализующая приведённые функции, показана ниже: Цифровые компараторы выпускают в виде микросхем. Код микросхем в отечественных сериях – СП. На схемах компараторы кодов обозначаются символами равенства: «= =» Например, четырёхразрядный компаратор кодов имеет два варианта обозначения: Помимо восьми входов для сравниваемых кодов (двух четырёхразрядных кодов, обозначаемых А0…A3 и В0 …В3) компаратор имеет три управляющих входа для наращивания разрядности (А > В, А < В, А = В) и три выхода результирующих сигналов (А > В, А < В, А = В). Для удобства на схемах управляющие входы и выходы иногда обозначают просто «>», «<» и «=». Нулевые разряды кодов (А0 и В0) – младшие, третьи разряды (А3 и В3) – старшие. Если используется одиночная микросхема, то для её правильной работы достаточно подать единицу на вход А = В, а состояния входов А < В и А > В не важны: на них можно подать как нуль, так и единицу. Назначение выходов понятно из их названия, а полярность выходных сигналов положительная (активный уровень – единица). Если микросхема компараторов кодов каскадируются (объединяются) для увеличения числа разрядов сравниваемых кодов, то выходные сигналы микросхемы, обрабатывающей младшие разряды кода, нужно подать на одноимённые входы микросхемы, обрабатывающей старшие разряды кода: Сумматоры Сумматоры – это комбинационные устройства, предназначенные для сложения двух входных двоичных кодов. Например, арифметическая сумма кодов 0111 (число 7) и 0101 (число 5) равна 1100 (число 12). Арифметическая сумма кодов 1101 (число 13) и 0110 (число 6) равна 10011 (число 19), т. е. сумма двух двоичных чисел с числом разрядов n может иметь результат с числом разрядов n + 1. Этот дополнительный (старший) разряд называется выходом переноса (Р). На схемах сумматоры обозначаются буквами SM. Микросхемы сумматоров кодируются буквами ИМ. Рассмотрим таблицу истинности сложения двух одноразрядных двоичных чисел без учёта переноса: Запишем логическую функцию: S = AB AB Устройство, реализующее эту функцию, называется «исключающее ИЛИ»: Схема не информирует о бите переноса. Рассмотрим сложение двух одноразрядных двоичных чисел, для чего составим таблицу сложения (таблицу истинности), в которой отразим значение входных чисел А и В, значение результата суммирования S и значения переноса в старший разряд Р: Работа устройства, реализующего таблицу истинности, описывается следующими уравнениями: S = AB AB и Р = АВ Устройство, реализующего таблицу истинности, содержит «исключающие ИЛИ» и конъюнктор «И» Это устройство называется полусумматором и изображается в виде: Устройства называются полусумматором, т. к. имеет только два входа и не воспринимается сигнал переноса от других микросхем. Он используется только в младшем разряде. Рассмотрим сложение двух одноразрядных двоичных чисел с учётом бита переноса от других микросхем: Работа устройства, реализующего таблицу истинности, описывается следующими S ABPn 1 ABPn 1 ABPn 1 ABPn 1 уравнениями: Pn ABPn 1 ABPn 1 ABPn 1 ABPn 1 Устройство, реализующие таблицу, содержит два полусумматора и дизъюнктор «ИЛИ»: Это устройство называется одноразрядным сумматором и имеет следующее условное графическое обозначение: Сумматоры бывают одноразрядные (для суммирования двух одноразрядных чисел) двухразрядные (суммируют двухразрядные числа) и четырёхразрядные (суммируют четырёхразрядные числа). Чаще всего применяют 4 – х разрядные: Вход С (вход расширения) для объединения нескольких сумматоров с целью увеличения разрядности: