1 Основные архитектурные принципы построения компьютера

advertisement

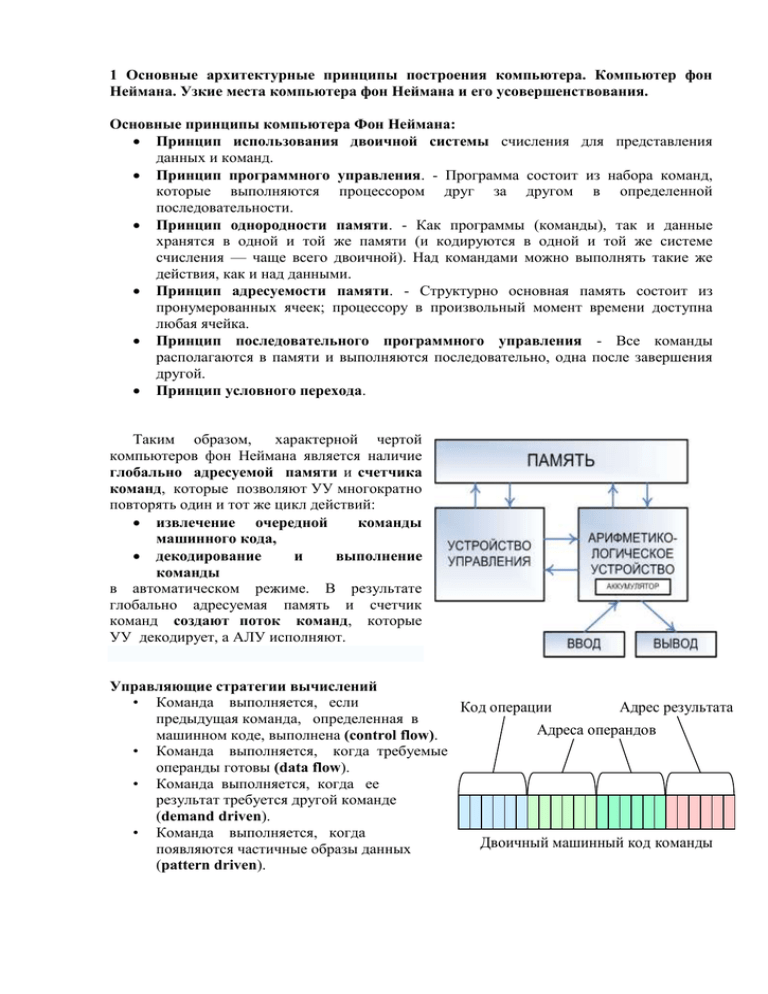

1 Основные архитектурные принципы построения компьютера. Компьютер фон Неймана. Узкие места компьютера фон Неймана и его усовершенствования. Основные принципы компьютера Фон Неймана: Принцип использования двоичной системы счисления для представления данных и команд. Принцип программного управления. - Программа состоит из набора команд, которые выполняются процессором друг за другом в определенной последовательности. Принцип однородности памяти. - Как программы (команды), так и данные хранятся в одной и той же памяти (и кодируются в одной и той же системе счисления — чаще всего двоичной). Над командами можно выполнять такие же действия, как и над данными. Принцип адресуемости памяти. - Структурно основная память состоит из пронумерованных ячеек; процессору в произвольный момент времени доступна любая ячейка. Принцип последовательного программного управления - Все команды располагаются в памяти и выполняются последовательно, одна после завершения другой. Принцип условного перехода. Таким образом, характерной чертой компьютеров фон Неймана является наличие глобально адресуемой памяти и счетчика команд, которые позволяют УУ многократно повторять один и тот же цикл действий: извлечение очередной команды машинного кода, декодирование и выполнение команды в автоматическом режиме. В результате глобально адресуемая память и счетчик команд создают поток команд, которые УУ декодирует, а АЛУ исполняют. Управляющие стратегии вычислений • Команда выполняется, если Код операции Адрес результата предыдущая команда, определенная в Адреса операндов машинном коде, выполнена (control flow). • Команда выполняется, когда требуемые операнды готовы (data flow). • Команда выполняется, когда ее результат требуется другой команде (demand driven). • Команда выполняется, когда Двоичный машинный код команды появляются частичные образы данных (pattern driven). Узкие места архитектуры фон Неймана • Последовательное выполнение команд • Хранение данных и программы в одном ОЗУ • Один канал связи Архитектурные усовершенствования Оптимизация подсистемы памяти • Контроллер памяти • Высокоскоростная шина • Кэш и иерархия памяти • Виртуальная память • Аппаратная предвыборка данных и команд Оптимизация выполнения команд • Конвейеризация • Упрощение набора команд • Истинный параллелизм – Данные (SIMD) – Инструкции – Потоки – Программы 2 Иерархия памяти. Основной принцип построения иерархической памяти. Типичная схема иерархии памяти. Идея иерархической (многоуровневой) организации памяти заключается в использовании на одном компьютере нескольких уровней памяти, которые характеризуются разным временем доступа к памяти и объемом памяти. (Время доступа к памяти это время между операциями чтения/записи, которые выполняются по случайным адресам.) Основой для иерархической организации памяти служит принцип локальности ссылок во времени и в пространстве. • Локальность во времени состоит в том, что процессор многократно использует одни и те же команды и данные. • Локальность в пространстве состоит в том, что если программе нужен доступ к слову с адресом A, то скорее всего, следующие ссылки будут к адресам, расположенным по близости с адресом A. Из свойства локальности ссылок следует, что в типичном вычислении обращения к памяти концентрируются вокруг небольшой области адресного пространства и более того, выборка идет по последовательным адресам. Время доступа к иерархически организованной памяти уменьшается благодаря следующему • сокращению количества обращений к оперативной памяти • совмещению обработки текущего фрагмента программы и пересылки данных из основной памяти в буферную память. Схема: Регистровая память – 1 такт Кэш 1-го уровня – 1-2 такта Кэш 2-го уровня – 3-5 тактов Кэш 3-го уровня – 6-11 тактов Основная память – 12-55 тактов Внешняя память - 106 тактов интерливингом — расслоением адресов ячеек памяти — весь объем памяти делится на несколько банков. Двойные слова с последовательными адресами располагаются в разных банках. Во время считывания информации из оперативной памяти за один цикл можно организовать параллельное извлечение информации из разных блоков, что уменьшает количество циклов ожидания. 3 Определение кэш-памяти. Параметры кэш-памяти. Типы кэш-памяти (по содержимому, инклюзивная/эксклюзивная). Временные характеристики. Кэш-память это высокоскоростная память небольшого размера с прямым доступом. Она предназначена для временного хранения фрагментов кода и данных. Кэш-память охватывает все адресное пространство памяти, но в отличие от оперативной памяти, она не адресуема и невидима для программиста. Схема построения кэш-памяти • Кэш-память построена на принципе локальности ссылок во времени и в пространстве. • Кэш-контроллер загружает копии программного кода и данных из ОП в кэшпамять блоками, равными размеру строки за один цикл чтения. Процессор читает из кэш-памяти по словам. • Кэш-контроллер перехватывает запросы процессора к основной памяти и проверяет, есть ли действительная копия информации в кэш-памяти. Когда контроллер помещает данные в кэш- память? • Загрузка по требованию (on demand). • Спекулятивная загрузка (speculative load). Алгоритм предполагает помещать данные в кэш-память задолго до того, как к ним произойдет реальное обращение. У кэш-контроллера есть несколько алгоритмов, которые указывают, какие ячейки памяти потребуются процессору в ближайшее время. Когда контроллер выполняет поиск данных в памяти? • после фиксации промаха (сквозной просмотр). • одновременно с поиском блока в кэш-памяти, в случае кэш-попадания, обращение к оперативной памяти прерывается (отложенный просмотр). Самой быстрой памятью является кэш первого уровня — L1-cache. Она является частью процессора, расположена на одном с ним кристалле. Состоит из кэша команд и кэша данных. L1 кэш работает на частоте процессора, обращение к нему может производиться каждый такт. Латентность доступа обычно равна 2−4 такта. Объём обычно невелик. Вторым по быстродействию L2-cache — кэш второго уровня. Обычно он расположен в непосредственной близости от ядра. Обычно латентность L2 кэша составляет от 8 до 20 тактов ядра. Кэш третьего уровня наименее быстродействующий и обычно расположен отдельно от ядра, но он может быть очень внушительного размера — более 32 Мбайт. L3 кэш медленнее предыдущих кэшей, но всё равно значительно быстрее, чем оперативная память. Характеристик кэш-памяти — уровень ассоциативности — отображает её логическую сегментацию. Дело в том, что последовательный перебор всех строк кэша в поисках необходимых данных потребовал бы десятков тактов и свёл бы на нет весь выигрыш. Поэтому ячейки ОЗУ жёстко привязываются к строкам кэш-памяти, что значительно сокращает время поиска. С каждой ячейкой ОЗУ может быть связано более одной строки кэш-памяти: например, n-канальная ассоциативность обозначает, что информация по некоторому адресу оперативной памяти может храниться в n местах кэш-памяти. При одинаковом объеме кэша схема с большей ассоциативностью будет наименее быстрой, но наиболее эффективной. Элементы данных, имеющих одинаковые номера множеств, т.е. отстоящие на определенное расстояние в памяти, помещаются в одно и то же множество строк, вытесняя друг друга. Число элементов в каждом множестве (равное числу банков кэшпамяти) называется степенью ассоциативности кэш-памяти • • • Размер кэша – Большой, чтобы вместить рабочие данные – Маленький, для быстрого доступа Степень ассоциативности кэша – Большая, чтобы избегать пробуксовки – Маленькая, для быстрого доступа Размер строки кэша – Большой, чтобы использовать локальность – Большой, чтобы уменьшить теги – Маленький (много блоков меньше промахов, меньше задержки при промахе) В иерархии памяти обычно более быстрые уровни хранят избранные копии содержимого более медленных уровней. Например, в L2 КЭШе хранятся области из оперативной памяти, а в L1 хранятся области из L2. Такая архитектура называется инклюзивной (Inclusive). Места на кристалле процессора мало. Расточительно хранить на этом пространстве две копии одних и тех же данных. Поэтому в эксклюзивной (Exclusive) архитектуре КЭШ после того как данные переданы из L2 в L1, их копия в L2 уничтожается. То есть в эксклюзивном КЭШе мы можем хранить объем информации больше чем в инклюзивном только. Хотя в таком случае скорость КЭШа может уменьшаться, но эффективность увеличивается. 4 Алгоритмы отображения данных в кэш-память. Алгоритмы замещения строк в кэш-памяти. Сравнительный анализ алгоритмов. Пространство памяти отображения данных в кэше разбивается на строки - блоки фиксированной длины (например, 32, 64 или 128 байт). Каждая строка кэша может содержать непрерывный выровненный блок байт из оперативной памяти. Какой именно блок оперативной памяти отображен на данную строку кэша, определяется тегом строки и алгоритмом отображения. По алгоритмам отображения оперативной памяти в кэш выделяют три типа кэш-памяти: • Прямой – 1 блок – 1 строка – Плюс: быстрый поиск, маленькие теги, простая реализация – Минус: пробуксовка КЭШа В этом случае адрес памяти (номер блока) однозначно определяет строку кэша, в которую будет помещен данный блок. Физический адрес разбивается на три части: смещение в блоке (строке кэша), номер строки кэша и тег. Тот или иной блок будет всегда помещаться в строго определенную строку кэша, при необходимости заменяя собой хранящийся там другой блок. Когда ЦП обращается к кэшу за необходимым блоком, для определения удачного обращения или кэш-промаха достаточно проверить тег лишь одной строки. Очевидными преимуществами данного алгоритма являются простота и дешевизна реализации. К недостаткам следует отнести низкую эффективность такого кэша из-за вероятных частых перезагрузок строк. • (Полностью) ассоциативный – 1 блок – любая строка – Плюс: нет пробуксовки кэша – Минус: медленный поиск, большие теги, сложная реализация Кэш-контроллер может поместить любой блок оперативной памяти в любую строку кэшпамяти. В этом случае физический адрес разбивается на две части: смещение в блоке (строке кэша) и номер блока. При помещении блока в кэш номер блока сохраняется в теге соответствующей строки. Когда ЦП обращается к кэшу за необходимым блоком, кэшпромах будет обнаружен только после сравнения тегов всех строк с номером блока. Одно из основных достоинств данного способа отображения - хорошая утилизация оперативной памяти, т.к. нет ограничений на то, какой блок может быть отображен на ту или иную строку кэш-памяти. Недостаток - сложная аппаратная реализация этого способа, что приводит к увеличению времени доступа к такому кэшу и увеличению его стоимости. • Множественно-ассоциативный – 1 блок – несколько строк – Компромиссный вариант При этом способе организации кэш-памяти строки объединяются в группы, в которые могут входить 2, 4… строк. В соответствии с количеством строк в таких группах различают 2, 4… ассоциативный кэш. При обращении к памяти физический адрес разбивается на три части: смещение в блоке (строке кэша), номер группы (набора) и тег. Блок памяти, адрес которого соответствует определенной группе, может быть размещен в любой строке этой группы, и в теге строки размещается соответствующее значение. Для того чтобы процессор смог идентифицировать кэш-промах, ему надо будет проверить теги лишь одной группы Алгоритмы замещения • Least Recently Used (LRU) - вытесняется буфер, неиспользованный дольше всех • Most Recently Used (MRU) - вытесняется последний использованный буфер • Least Frequently Used (LFU) - вытесняется буфер, использованный реже всех 5 Алгоритмы записи данных в оперативную память. Сравнительный анализ алгоритмов. Работая с кэш-памятью, необходимо помнить, что одновременно могут существовать две копии одних и тех же данных: одна в кэш-памяти, а другая в основной памяти. Если изменяется только одна из этих копий, то по одному и тому же адресу будут существовать два набора информации. Кэш-память должна содержать систему обновления для предотвращения использования устаревших данных в качестве достоверных. Для согласования содержимого кэш-памяти с основной памятью используются три общих метода: сквозная запись, буферизованная сквозная запись и обратная запись. Сквозная запись. При обновлении кэш-памяти методом сквозной записи кэшконтроллер одновременно обновляет содержимое основной памяти. Иначе говоря, основная память отражает текущее содержимое кэш-памяти. Быстрое обновление позволяет перезаписывать любой блок в кэш-памяти в любое время без потери данных. Система со сквозной записью проста, но время, требуемое для записи в основную память, снижает производительность. Буферизованная сквозная запись. В схеме обновления в буферизованной сквозной записью любая запись в основную память буферизуется, т.е. информация задерживается в кэш-памяти перед записью в основную память. Затем процессор начинает новый цикл до завершения цикла записи в основную память. Если за записью следует чтение, то это кэш-попадание, так как чтение может быть выполнено в то время, когда кэш-контроллер занят обновлением основной памяти. Эта буферизация позволяет избежать снижения производительности, характерного для системы со сквозной записью. У этого метода есть один существенный недостаток. Так как обычно буферизуется только одиночная запись, то две последовательные записи в основную память требуют цикла ожидания процессора. В схеме обновления с обратной записью используется бит «изменения» в поле тега. Этот бит устанавливается, если блок был обновлен новыми данными и является более поздним, чем его оригинальная копия в основной памяти. Перед тем как перезаписать блок в кэш-памяти, контроллер проверяет состояние этого бита. Если он установлен, то контроллер переписывает данный блок в основную память перед загрузкой новых данных в кэш-память. Обратная запись быстрее сквозной, так как обычно число случаев, когда блок изменяется и должен быть переписан в основную память, меньше числа случаев, когда эти блоки считываются и перезаписываются. Однако обратная запись имеет несколько недостатков. Вопервых, все измененные блоки должны быть переписаны в основную память перед тем, как другое устройство сможет получить к ним доступ. Во-вторых, в случае, когда содержимое кэш-памяти теряется, но содержимое основной памяти сохраняется, нельзя определить, какие места в основной памяти содержат устаревшие данные. 6 Проблемы поддержания когерентности данных. Способы их решения. Когерентность кэша — свойство кэшей, означающее целостность данных, хранящихся в локальных кэшах для разделяемого ресурса. Когерентность определяет поведение чтений и записей в одно и то же место памяти. Протоколы поддержки когерентности отвечают за поддержание корректности данных между всеми кэшами в системе. Протокол поддерживает когерентность памяти согласно выбранной модели. Главная трудность заключается в том, что данные в двух различных кэш-устройствах должны быть согласованными. Это означает, что каждый запрос к определенному адресу в памяти должен всегда предоставлять наиболее поздние данные, относящиеся к этому адресу. Поэтому наиболее часто проблема согласованности памяти возникает в многопроцессорных системах. Для поддержки согласованности кэш-памяти на аппаратном уровне был разработан протокол MESI. Протокол MESI приписывает каждой кэш-строке одно из четырех состояний, которые контролируются двумя битами MESI. Modified (модифицированная), Exclusive (эксклюзивная), Shared (разделяемая), Invalid (недействительная). Эти четыре термина определяют четыре возможных состояния кэш-строки. Состояние кэш-строки может быть изменено процессором (посредством операций чтения, записи или внутренней проверки), другими процессорами. В любой заданный момент времени кэш-строка находится в одном из четырех состояний: • M (Модифицированная)– данные в строке модифицированы, но не переписаны в ОП. Данные достоверны только в данной кэш-памяти. • E (Эксклюзивная)-- данные в строке совпадают с аналогичной строкой в ОП, но отсутствуют в других кэшах. • S (Разделяемая) – данные строки кэш-памяти не совпадают с данными аналогичной строкой в ОП и могут присутствовать в другой кэш-памяти. • I (Недействительная) – строка не содержит достоверных данных. MESI был разработан для кэш-памяти с отложенной записью, в которой запись с размещением для случаев кэш-промаха не выполняется. Согласно протоколу MESI, все запросы на запись должны переключаться на внешнюю шину. Иными словами, так кэшпамять реализует стратегию сквозной записи. Рисунок 8.5. Переходы из одного состояния MESI в другое Запрос на чтение М в М (R1): запрос на чтение приводит к кэш-попаданию, данные находятся в кэш-памяти и передаются в процессор. Е в Е (R2): как и в предыдущем случае, запрос на чтение приводит к кэш-попаданию, данные находятся в кэш-памяти и передаются в процессор. S в S (R3): запрос на чтение приводит к кэш-попаданию, данные находятся в кэш-памяти и передаются в процессор. I в E (R4): запрос на чтение приводит к кэш-промаху, данных в кэш-памяти нет. Кэшконтроллер запускает внешний цикл чтения для того, чтобы прочитать информацию и переходит в эксклюзивное состояние I в S (R5): как и в предыдущем случае I в I (R6): запрос на чтение приводит к кэш-промаху, данных в кэш-памяти нет. Однако заполнение кэш-строки не может быть выполнено кэш-контроллером. Таким образом, строка остается недействительной. Запрос на запись М в М (W1): запрос на запись приводит к кэш-попаданию, данные находятся в кэшпамяти и перезаписываются. Это соответствует стратегии кэш-памяти с отложенной записью Е в М (W2): запрос на запись приводит к кэш-попаданию. Кэш-контроллер перезаписывает кэш-строку и отмечает ее как модифицированную. Этот случай также соответствует стратегии кэш-памяти с отложенной записью. S в E (W3): запрос на запись приводит к кэш-попаданию. Поскольку исходная строка помечена как разделяемая, она может храниться и в других кэш-блоках. Согласно протоколу MESI, этот элемент должен быть объявлен недействительным, и кэшконтроллер поэтому запускает цикл записи через внешнюю шину. Таким образом, после этого строка будет находиться только в локальной кэш-памяти; в соответствии с циклом сквозной записи, элемент в основной памяти также обновляется. После этого кэш-строка объявляется эксклюзивной. S в S (W4): в этом случае запрос на запись тоже приводит к кэш-попаданию. Однако W4 соответствует стратегии кэш-памяти со сквозной записью. По этой причине все последующие запросы на запись передаются на шину, что обеспечивает соблюдение стратегии сквозной записи; кэш-строка остается помеченной как разделяемая. I в I (W5): запрос на запись приводит к кэш-промаху, данных в кэш-памяти нет. Нужный отсутствующий элемент данных из основной памяти в кэш-память не загружается. Кэшстрока остается недействительной. Просмотр M в S (S1): цикл проверки обнаруживает модифицированную кэш-строку, поэтому недействительной она не объявляется. Соответствующая кэш-строка перезаписывается в основную память. M в I (S2): цикл проверки обнаруживает модифицированную кэш-строку; на этот раз она объявляется недействительной. Соответствующая кэш-строка перезаписывается в основную память. E в S (S3): цикл проверки обнаруживает кэш-строку, помеченную как эксклюзивная. Она не изменялась и поэтому не должна перезаписываться в основную память. Эта операция служит для пересылки строки, которая вначале находилась только в одной кэш-памяти, во вторую. E в I (S4): в цикле проверки была обнаружена кэш-строка, помеченная как эксклюзивная. Она не изменялась, поэтому ее также не надо перезаписывать в основную память. В противоположность предыдущему случаю, кэш-строка должна быть объявлена недействительной, S в S (S5): в цикле проверки была обнаружена кэш-строка, помеченная как разделяемая. S в I (S6): в цикле проверки была обнаружена кэш-строка, помеченная как разделяемая. Она не изменялась и поэтому не должна перезаписываться в основную память при последующем объявлении ее недействительной. I в I (S7): в цикле проверки была обнаружена кэш-строка, помеченная как недействительная, т.е. не содержащая достоверной информации. 7 Понятие виртуальной памяти. Способы управления виртуальной памятью. Их сравнение. Виртуальная память представляет собой совокупность всех ячеек памяти – оперативной и внешней. (Наличие ВЗУ обязательно.) Она имеет сквозную нумерацию от нуля до предельного значения адреса. Принцип виртуальной памяти предполагает, что пользователь имеет дело с кажущейся одноуровневой памятью, объем которой равен всему адресному пространству системы независимо от объема ОЗУ и объема памяти, необходимой для других программ, участвующих в мультипрограммной обработке. Использование ВЗУ очень удобно, так как в это время пользователь оперирует с общим адресным пространством и ему безразлично, какая физическая память при этом используется внешняя или внутренняя. При работе ВП всего лишь подразумевается различие между виртуальными адресами и физическими. Способы управления виртуальной памятью Страничный Виртуальная память разбивается на страницы, которые содержат определённое фиксированное количество ячеек памяти. Все страницы одинаковы по количеству ячеек. Передача информации между памятью и диском всегда осуществляется целыми страницами. Страницы, имеют фиксированную длину, обычно являющуюся степенью числа 2. Процесс обращается к памяти с помощью адреса виртуальной памяти, который содержит в себе номер страницы и смещение внутри страницы. Операционная система преобразует виртуальный адрес в физический. Система отображения виртуальных адресов в физические сводится к системе отображения виртуальных страниц в физические и представляет собой таблицу страниц, которая адресуется при помощи специального регистра процессора и позволяет определить номер кадра по виртуальному адресу. В большинстве современных компьютеров со страничной организацией виртуальной памяти все таблицы страниц хранятся в основной памяти, а быстрота доступа к элементам таблицы текущей виртуальной памяти достигается за счет наличия сверхбыстродействующей буферной памяти (кэша). Во-первых, одним из преимуществ ВП с СО является достаточно большой объём прямо адресуемой памяти. Размер виртуальной памяти целиком зависит от объёма жесткого диске. Еще одним преимуществом ВП с СО является то, что программы могут размещаться в любых свободных страницах. И одним из важнейших преимуществ ВП с СО повышение уровня мультипрограммной работы. Основным недостатком виртуальной памяти, пожалуй, является то количество времени, которое машина тратит на обращение к внешней памяти. И недостатком является внутренняя фрагментация страниц. сегментный Механизм организации виртуальной памяти, при котором виртуальное пространство делится на части произвольного размера — сегменты. Этот механизм позволяет разбить данные процесса на логические блоки. При загрузке процесса часть сегментов помещается в оперативную память, а часть сегментов размещается в дисковой памяти. Сегменты одной программы могут занимать в оперативной памяти несмежные участки. Во время загрузки система создает таблицу сегментов процесса (аналогичную таблице страниц), в которой для каждого сегмента указывается начальный физический адрес сегмента в оперативной памяти, размер сегмента. Если виртуальные адресные пространства нескольких процессов включают один и тот же сегмент, то в таблицах сегментов этих процессов делаются ссылки на один и тот же участок оперативной памяти, в который данный сегмент загружается в единственном экземпляре. Система с сегментной организацией функционирует аналогично системе со страничной организацией: время от времени происходят прерывания, связанные с отсутствием нужных сегментов в памяти, при необходимости освобождения памяти некоторые сегменты выгружаются, при каждом обращении к оперативной памяти выполняется преобразование виртуального адреса в физический. Виртуальный адрес при сегментной организации памяти состоит из номера сегмента и смещение в сегменте. Физический адрес получается путем сложения начального физического адреса сегмента, найденного в таблице сегментов по номеру, и смещения. Недостатком данного метода распределения памяти является фрагментация на уровне сегментов и более медленное по сравнению со страничной организацией преобразование адреса. странично-сегментный Отличие сегмента от страницы состоит в том, что длина сегмента может изменяться в процессе работы. Сегментно-страничная организация виртуальной памяти позволяет совместно использовать одни и те же сегменты данных и программного кода в виртуальной памяти разных задач. Адрес ячейки в данном случае складывается из 3х частей: первая содержит номер самого сегмента, по этому номеру машина обращается к сегментной таблице. Вторая часть адреса содержит номер искомой страницы, которая находится внутри выбранного сегмента и третья смещение, по которому находится требуемый адрес. Сначала берется некоторый начальный адрес сегментной таблицы и номер сегмента S из регистра математического адреса. Оба этих адреса складываются в сумматоре. Получившийся адрес является входом в сегментную таблицу. Далее, благодаря этому адресу, отыскивается соответствующий адрес страничной таблицы, который в свою очередь суммируется с номером искомой страницы в сумматоре. Результирующая сумма есть вход в страничную таблицу. Два варианта реализации таблицы страниц: Двухуровневая таблица преобразования адресов Буфер быстрого преобразования адресов (буфер ассоциативной трансляции (TLB)) Однако, ходить по страничным таблицам при каждом запросе физического адреса очень неэффективно. Следует изобрести некое подобие кэш-памяти для хранения записей из страничных таблиц. Собственно, для этой цели и существуют буфера преобразования. При каждом промахе TLB генерируется соответствующий исключительная ситуация, которая обрабатывается операционной системой. Она сохраняет состояние запущенной задачи, проходит по таблицам страниц, заполняет TLB и восстанавливает состояние приостановленной задачи. 9 Способы оптимизации программ, используемые компиляторами. Компилятор - это программа, которая преобразует текст на одном языке в текст на другом языке. Переводит программу на одном языке в коды процессора, которые затем могут быть непосредственно исполнены. Исполняемый код, который компилятор должен сгенерировать, зависит от архитектуры процессора. Некоторые компиляторы могут создавать код для большого числа различных архитектур, некоторые предназначены только для конкретной архитектуры Для задания параметров работы компиляторы имеют набор специальных опций (ключей), которые указываются в командной строке. Любой компилятор имеет много вариантов генерации исполняемого кода. В простейшем случае он просто заменяет каждую операцию входного языка на несколько инструкций процессора, выполняющих нужное действие. При этом программа компилируется очень быстро, но получающийся код выполняется довольно медленно. Для улучшения качества кода компилятор может выполнить его оптимизацию. Результатом оптимизации является более эффективный код (т.е. более быстрый или меньший по объему), дающий при выполнении такой же результат. Программа, оптимизированная для работы на конкретном процессоре, использующая все предоставляемые им вычислительные возможности, будут работать быстрее, чем некоторая общая версия. Поэтому, если известно, на процессоре какой именно архитектуры будет выполняться код, можно требовать от компилятора соответствующей оптимизации 10 Процессор, его состав и функционирование. Техника конвейеризации. Передача данных на конвейере. Временные оценки сложности. Большинство современных процессоров для персональных компьютеров в общем основаны на той или иной версии циклического процесса последовательной обработки информации, изобретённого Джоном фон Нейманом. Таким образом, характерной чертой компьютеров фон Неймана является наличие глобально адресуемой памяти и счетчика команд, которые позволяют УУ многократно повторять один и тот же цикл действий: извлечение очередной команды машинного кода, декодирование и выполнение команды в автоматическом режиме. В результате глобально адресуемая память и счетчик команд создают поток команд, которые УУ декодирует, а АЛУ исполняют. Конве́йер — это способ организации вычислений, с целью ускорения выполнения инструкций. Идея состоит в разделении обработки машинной инструкции на последовательность независимых стадий. Таким образом, в каждый момент времени в разных стадиях обработки находятся несколько инструкций. Применительно к процессорам принцип конвейера означает, что если мы сумеем разбить выполнение машинной инструкции на несколько этапов, то тактовая частота (а вернее, скорость, с которой процессор забирает данные на исполнение и выдает результаты) будет обратно пропорциональна времени выполнения самого медленного этапа. Если это время удастся сделать достаточно малым, то мы сумеем повысить тактовую частоту, значит производительность процессора. Процедуру выполнения практически любой инструкции можно разбить как минимум на пять непересекающихся этапов: Выборка команды Декодирование команды Выборка операндов Вычисление операции Запись результата Ступени Все ступени конвейера активны Латентность конвейера 1 1 Выборка команды 1 2 1 2 2 3 4 5 3 4 5 6 6 21 3 4 5 2 3 4 5 6 3 4 5 6 8 8 7 7 7 7 7 6 8 8 8 9 9 9 9 9 Время Что тормозит работу конвейера? • Зависимости по данным. Время исполнения операций Load и Store, которые могут обращаться к разным уровням кэш-памяти или к оперативной памяти не определено. • Конфликты по ресурсам. Если в программе идет зависимая цепочка инструкций (когда инструкция-2, следующая за инструкцией-1, использует для своих вычислений данные, только что вычисленные инструкцией-1), а время исполнения одной инструкции превосходит один такт, то мы вынуждены придержать выполнение очередной инструкции до тех пор, пока не будет полностью выполнена ее предшественница. • Зависимости по управлению, вызванные командами перехода. Обычно используется очень простой способ: в процессоре ведется табличка ранее совершенных переходов - для каждого условного перехода подсчитывается, сколько раз он "сработал", а сколько - "был проигнорирован". При неправильном предсказании конвейер обычно приходится "сбрасывать", восстанавливая состояние процессора, предшествующее моменту неправильного перехода. Решения: • • • Спекулятивное исполнение с предсказанием переходов Использование условных команд Использование предикатных регистров 11 Командный конвейер. Пример командного конвейера. Способы увеличения производительности конвейера. Причины приостановки конвейера и техника их преодоления. Конве́йер — это способ организации вычислений, с целью ускорения выполнения инструкций. Идея состоит в разделении обработки машинной инструкции на последовательность независимых стадий. Таким образом, в каждый момент времени в разных стадиях обработки находятся несколько инструкций. Применительно к процессорам принцип конвейера означает, что если мы сумеем разбить выполнение машинной инструкции на несколько этапов, то тактовая частота (а вернее, скорость, с которой процессор забирает данные на исполнение и выдает результаты) будет обратно пропорциональна времени выполнения самого медленного этапа. Если это время удастся сделать достаточно малым, то мы сумеем повысить тактовую частоту, значит производительность процессора. Процедуру выполнения практически любой инструкции можно разбить как минимум на пять непересекающихся этапов: Выборка команды Декодирование команды Выборка операндов Вычисление операции Запись результата Ступени Все ступени конвейера активны Латентность конвейера 1 1 Выборка команды 1 2 1 2 2 3 4 5 3 4 5 6 6 21 3 4 5 2 3 4 5 6 3 4 5 6 8 8 7 7 7 7 7 6 8 8 8 9 9 9 9 9 Время Что тормозит работу конвейера? • Зависимости по данным. Время исполнения операций Load и Store, которые могут обращаться к разным уровням кэш-памяти или к оперативной памяти не определено. • Конфликты по ресурсам. Если в программе идет зависимая цепочка инструкций (когда инструкция-2, следующая за инструкцией-1, использует для своих вычислений данные, только что вычисленные инструкцией-1), а время исполнения одной инструкции превосходит один такт, то мы вынуждены придержать выполнение очередной инструкции до тех пор, пока не будет полностью выполнена ее предшественница. • Зависимости по управлению, вызванные командами перехода. Обычно используется очень простой способ: в процессоре ведется табличка ранее совершенных переходов - для каждого условного перехода подсчитывается, сколько раз он "сработал", а сколько - "был проигнорирован". При неправильном предсказании конвейер обычно приходится "сбрасывать", восстанавливая состояние процессора, предшествующее моменту неправильного перехода. Решения: • • • Спекулятивное исполнение с предсказанием переходов Использование условных команд Использование предикатных регистров 12 CISC и RISC архитектуры. Основные характеристики. Сравнение. Реализация в современных микропроцессорах. CISC – архитектура (Типичными представителями являются процессоры на основе x86 команд, исключая современные) В основе архитектуры CISC лежит эффективное использование памяти и относительная простота ассемблерного программирования. Каждая команда CISCпроцессора включает в себя несколько операций. Это уменьшает количество операторов, требующихся для реализации конкретной программы, и предоставляет для программиста удобный и быстрый набор команд. Для CISC-процессоров характерны следующие черты: • Большое число машинных команд и выполняющихся за много тактов. • Большое количество методов адресации памяти. • Формат команд: операция и два операнда: источник и адрес результата. • • • • • • Команды переменной длины, длина часто меняется в зависимости от способа адресации. Команды обмена типа Р-П, П-Р, Р-Р. Небольшое количество (8-12) РОН. Это результат наличия команд, оперирующих непосредственно с памятью. Различным командам для выполнения требуется разное количество машинных тактов. Многоформатность команд. Многие специализированные команды используются недостаточно часто. В обычной программе используется около 20% наиболее употребительных команд. RISC-архитектуры Основная идея RISC-архитектуры состояла в том, что последовательность простых команд, давая тот же результат, что и последовательность составных команд, может выполняться на более простой физической архитектуре процессора при условии, что память так же не будет отставать. Это потребовалось для увеличения скорости обработки CISC-команд, так как известно, что любой CISC-процессор уступает RISC-процессорам по количеству выполняемых операций в секунду. CISC-процессоры проектировались под нужды asm-программистов, RISCпроцессоры проектировались в расчете на типовой код, генерируемый компилятором. Результаты глубокого анализа показали, что основные усилия должны быть направлены на • упрощение набора команд, • эффективную реализацию конвейерной обработки путем тщательного планирования компилятором его загрузки -- отделение медленной памяти от быстрой памяти (высокоскоростных регистров) (две инструкции Load/Store). Характеристики RISC-архитектур • Время выполнения большинства команд составляет один машинный такт. • Простые команды. • Все команды имеют одинаковую длину так, что каждая команда может быть исполнена за один такт применения микропрограмм. • Набор команд обычно включает в среднем 128 наиболее часто используемых команд. • Операнды располагаются в регистрах. Стек памяти редко используется для передачи параметров процедур, вместо этого используются регистры. • Формат чаще трехадресный: команда берет операнды из двух регистров и помещает результат в третий регистр. • Доступ к памяти только посредством команд Чтение и Запись. • Все операции, кроме Чтения и Записи, имеют тип Р-Р. • Большой файл регистров общего назначения. 13 Виды параллелизма в микропроцессорах. Классификация архитектур с точки зрения параллелизма. Примеры микропроцессоров. Уровни параллелизма в процессорах • Параллелизм данных (DLP – Data Level Parallelism) • Параллелизм команд • • (ILP – Instruction Level Parallelism) Параллелизм потоков (TLP – Thread Level Parallelism) Многоядерность Параллельные вычислительные системы — это физические компьютерные, а также программные системы, реализующие тем или иным способом параллельную обработку данных на многих вычислительных узлах. Идея распараллеливания вычислений базируется на том, что большинство задач может быть разделено на набор меньших задач, которые могут быть решены одновременно. Обычно параллельные вычисления требуют координации действий. Параллельные вычисления существуют в нескольких формах: параллелизм на уровне инструкций, параллелизм данных. К ним возрос интерес вследствие существования физических ограничений на рост тактовой частоты процессоров DLP • Векторные вычисления (SIMD) – SIMD расширения были введены в архитектуру x86 с целью повышения скорости обработки потоковых данных. Основная идея заключается в одновременной обработке нескольких элементов данных за одну инструкцию. • Единообразная обработка массивов данных Pentiumы II, III, IV ILP-процессоры • Имеют несколько исполнительных устройств • Исполняют несколько команд одновременно Окно команд Классификация ILP-архитектур • Суперскалярные – Процессор ищет независимые команды и планирует поток вычислений • VLIW / EPIC – Компилятор ищет независимые команды и планирует поток вычислений Itanium2 Эльбрус 2000 – VLIW/EPIC Alpha Power – RISC суперскаляр INT FP MEM TLP Многопоточность – это свойство платформы или программы, позволяющее процессу состоять из нескольких потоков команд, исполняющихся параллельно, без предписанного порядка во времени. Крупнозернистая многопоточность (Coarse-grained MT) ALU • 2 и более аппаратных контекстов – Регистры общего назначения ALU FPU – Счетчик команд MEM – Буфер выборки инструкций Такты • Одновременно не более 1 нити Cache miss Cache miss Cache miss • Аппаратное переключение контекстов при прерывании BR Мелкозернистая многопоточность (Fine-grained MT) • 2 и более аппаратных контекстов ALU – Регистры общего ALU назначения FPU – Счетчик команд MEM • Одновременно не более 1 нити • Аппаратное переключение на каждом Такты Одновременная многопоточность (Simultaneous MT) • 2 и более аппаратных контекстов ALU ALU – Регистры общего назначения FPU – Буфер выборки инструкций MEM – Буфер переупорядочивания Такты – Стек возврата • Привязка команд и нитей Поток 1 • До нескольких нитей одновременно Поток 2 • Контексты активны, переключения не происходит такте Поток 3 Операционная система CMP • • • • POWER 4 Barcelona Clovertown Opteron • • • Alpha 21464 Pentium 4 Itanium 2 SMT 14 Архитектуры с параллелизмом на уровне команд (ILP). Способы выявления и реализации ILP. Примеры микропроцессоров. ILP-процессоры • Имеют несколько исполнительных устройств • Исполняют несколько команд одновременно Классификация ILP-архитектур • Суперскалярные – Процессор ищет независимые команды и планирует поток вычислений • VLIW / EPIC – Компилятор ищет независимые команды и планирует поток вычислений Способы повышения производительности • Повышение темпа исполнения команд требует повышения темпа их доставки. Средства: – Спекулятивное исполнение команд • SS: автоматический выбор способа предсказания перехода • EPIC: способ предсказания перехода задает компилятор – Спекулятивная загрузка данных • SS: проверка корректности автоматическая • EPIC: проверка корректности по спец. команде – – Разрешение ложных зависимостей по данным • SS: переименование регистров • EPIC: компилятор не допускает ненужных зависимостей Оптимизация вызовов подпрограмм • SS: регистровый стек управляется процессоров автоматически • EPIC: регистровый стек управляется компилятором Суперскалярные • Сложный конвейер • Простой компилятор • Меньше ресурсов процессора – Регистры – Исп. устройства – Кэш • Меньше команд за такт: 3, 4, 5 (<50%) Окно команд INT FP MEM BR VLIW / EPIC • Простой конвейер • Сложный компилятор • Больше ресурсов процессора – Регистры – Исп. устройства – Кэш • Больше команд за такт: 6 (>50%) Itanium2 Эльбрус 2000 – VLIW/EPIC Alpha Power – RISC суперскаляр 15 Архитектуры с параллелизмом на уровне данных (DLP). Способы выявления и реализации DLP. Примеры микропроцессоров. Параллельные вычислительные системы — это физические компьютерные, а также программные системы, реализующие тем или иным способом параллельную обработку данных на многих вычислительных узлах. Идея распараллеливания вычислений базируется на том, что большинство задач может быть разделено на набор меньших задач, которые могут быть решены одновременно. Обычно параллельные вычисления требуют координации действий. Параллельные вычисления существуют в нескольких формах: параллелизм на уровне инструкций, параллелизм данных. К ним возрос интерес вследствие существования физических ограничений на рост тактовой частоты процессоров Параллелизм данных Основная идея подхода, основанного на параллелизме данных, заключается в том, что одна операция выполняется сразу над всеми элементами массива данных. Различные фрагменты такого массива обрабатываются на векторном процессоре или на разных процессорах параллельной машины. Распределением данных между процессорами занимается программа. Векторизация или распараллеливание в этом случае чаще всего выполняется уже на этапе компиляции – перевода исходного текста программы в машинные команды. Роль программиста в этом случае обычно сводится к заданию опций векторной или параллельной оптимизации компилятору, директив параллельной компиляции, использованию специализированных языков для параллельных вычислений. • • Векторные вычисления (SIMD) Единообразная обработка массивов данных SIMD-расширения были введены в архитектуру x86 с целью повышения скорости обработки потоковых данных. Основная идея заключается в одновременной обработке нескольких элементов данных за одну инструкцию. • • • Векторно-конвейерные процессоры – Cray – Fujitsu VX/VP – NEC SX Векторные расширения – x86: MMX, 3DNow!, SSE, SSE2, … – PowerPC: AltiVec Перспективные векторные процессоры – STI Cell – Intel Larabee Первой SIMD-расширение ввела фирма Intel - это расширение MMX. Оно стало использоваться в процессорах Pentium MMX и Pentium II. Расширение MMX работает с 64-битными регистрами MM0-MM7, физически расположенными на регистрах сопроцессора, и включает 57 новых инструкций для работы с ними. 64-битные регистры логически могут представляться как одно 64-битное, два 32-битных, четыре 16-битных или восемь 8-битных упакованных целых Расширение 3DNow! - Технология 3DNow! была введена фирмой AMD в процессорах K6. Расширение работает с регистрами 64-битными MMX, которые представляются как два 32-битных вещественных числа с одинарной точностью. Система команд расширена 21 новой инструкцией, среди которых есть команда выборки данных в кэш L1. Расширение SSE С процессором Intel Pentium III впервые появилось расширение SSE. Это расширение работает с независимым блоком из восьми 128-битных регистров XMM0-XMM7. Каждый регистр XMM представляет собой четыре упакованных 32-битных вещественных числа с одинарной точностью. Команды блока XMM позволяют выполнять как векторные, так и скалярные операции. Кроме инструкций с блоком XMM в расширение SSE входят и дополнительные целочисленные инструкции с регистрами MMX, а также инструкции управления кэшированием. Расширение SSE2 В процессоре Intel Pentium 4 набор инструкций получил очередное расширение - SSE2. Оно позволяет работать с 128-битными регистрами XMM как с парой упакованных 64битных вещественных чисел двойной точности, а также с упакованными целыми числами: 16 байт, 8 слов, 4 двойных слова или 2 учетверенных (64-битных) слова. Введены новые инструкции вещественной арифметики двойной точности, инструкции целочисленной арифметики, 128-разрядные для регистров XMM и 64-разрядные для регистров MMX. Ряд старых инструкций MMX распространили и на XMM (в 128-битном варианте). 4-я лаба 17 Структура процессоров VLIW/EPIC. Причины, ограничивающие производительность процессоров VLIW, и средства их преодоления. Примеры микропроцессоров. На вход процессора подается последовательность больших команд, состоящих из нескольких простых операций, которые могут исполняться параллельно. Преимущество перед суперскалярами Меньше места на процессоре тратится на управление, больше остается на ресурсы: регистры, исполнительные устройства, кэш-память. Более тщательное планирование дает лучшее заполнение исполнительные устройств Недостатки Долгое время планирования потока команд. Невозможность учесть динамику исполнения программы. Примеров данной архитектуры является Itanium Явный ILP (параллелизм на уровне команд) Компилятор объединяет команды процессора в связки по три, которые могут быть выполнены параллельно. Процессор обеспечивает большое число ресурсов для реализации ILP. Способы увеличения ILP Явная спекуляция по данным и управлению (уменьшает задержки по памяти). Предикатное исполнение команд (устраняет ветвления). Аппаратная поддержка программной конвейеризации циклов. Предсказание ветвлений. Специальные способы увеличения производительности программ Специальная поддержка модульности программ (регистровый стек, вращающиеся регистры) Высокопроизводительная вещественная арифметика. Простой широкий конвейер Много команд за такт (до 6) Большие вычислительные ресурсы Много исполнительных устройств (11) Большой объем (до 12 MB) кэш-памяти Большое число регистров (264) 128 целочисленных регистра 128 вещественных регистра 64 предикатных регистра 8 регистров ветвлений 128 прикладных регистра Первые несколько регистров подпрограммы, начиная с r32 для целочисленных, f32 для вещественных и p16 для предикатных, могут быть обозначены как вращающиеся. При выполнении специальных команд ветвления виртуальные номера вращающихся регистров циклически сдвигаются вправо на один. Команды архитектуры Itanium объединяются в связки по три независимые инструкции, которые затем исполняются параллельно. Связка содержит 3 команды и поле шаблона. Шаблон указывает типы команд в связке. Он определяет, какие исполнительные устройства будут задействованы при исполнении. Формат команды (qp) ops[.comp1] [.comp2] r1 = r2, r3 Средства повышения производительности в IA-64 Предикатное исполнение команд - для каждой инструкции в программе указан предикатный регистр, значение которого определяет, будет ли вы данная инструкция выполнена. Аппаратные счетчики циклов Спекуляция по данным и управлению - предварительная загрузка (и использование) данных до того, как стало ясно, что они понадобятся, устраняет простой из-за ожидания данных. Регистровый стек, RSE Аппаратная поддержка программной конвейеризации циклов – при программной конвейеризации выполнение цикла организуется в виде конвейера, так что отдельные операции на каждой итерации цикла работают независимо, т.к. соответствуют разным итерациям исходного цикла. 18 Средства повышения производительности в архитектуре Itanium. Средства повышения производительности в IA-64 Предикатное исполнение команд - для каждой инструкции в программе указан предикатный регистр, значение которого определяет, будет ли вы данная инструкция выполнена. Аппаратные счетчики циклов Спекуляция по данным и управлению - предварительная загрузка (и использование) данных до того, как стало ясно, что они понадобятся, устраняет простой из-за ожидания данных. Регистровый стек, RSE Аппаратная поддержка программной конвейеризации циклов – при программной конвейеризации выполнение цикла организуется в виде конвейера, так что отдельные операции на каждой итерации цикла работают независимо, т.к. соответствуют разным итерациям исходного цикла. Явный ILP (параллелизм на уровне команд) Компилятор объединяет команды процессора в связки по три, которые могут быть выполнены параллельно. Процессор обеспечивает большое число ресурсов для реализации ILP. Способы увеличения ILP Явная спекуляция по данным и управлению (уменьшает задержки по памяти). Предикатное исполнение команд (устраняет ветвления). Аппаратная поддержка программной конвейеризации циклов. Предсказание ветвлений. Специальные способы увеличения производительности программ Специальная поддержка модульности программ (регистровый стек, вращающиеся регистры) Высокопроизводительная вещественная арифметика. Простой широкий конвейер Много команд за такт (до 6) Большие вычислительные ресурсы Много исполнительных устройств (11) Большой объем (до 12 MB) кэш-памяти Большое число регистров (264) 128 целочисленных регистра 128 вещественных регистра 64 предикатных регистра 8 регистров ветвлений 128 прикладных регистра Первые несколько регистров подпрограммы, начиная с r32 для целочисленных, f32 для вещественных и p16 для предикатных, могут быть обозначены как вращающиеся. При выполнении специальных команд ветвления виртуальные номера вращающихся регистров циклически сдвигаются вправо на один. Команды архитектуры Itanium объединяются в связки по три независимые инструкции, которые затем исполняются параллельно. Связка содержит 3 команды и поле шаблона. Шаблон указывает типы команд в связке. Он определяет, какие исполнительные устройства будут задействованы при исполнении. Формат команды (qp) ops[.comp1] [.comp2] r1 = r2, r3 19 Понятие многопоточности. Средства синхронизации потоков. Многопоточность – это свойство платформы или программы, позволяющее процессу состоять из нескольких потоков команд, исполняющихся параллельно, без предписанного порядка во времени. Цель – более эффективное использование ресурсов компьютера К достоинствам многопоточности в программировании можно отнести следующее: Упрощение программы в некоторых случаях, за счет использования общего адресного пространства. Меньшие относительно процесса временны́е затраты на создание потока. Повышение производительности процесса за счет распараллеливания процессорных вычислений и операций ввода/вывода. Все потоки находятся в едином адресном пространстве процесса, т.е. имеют общую память Создание потока и переключение между ними менее трудоемко, чем аналогичные операции над процессами Исключение некорректной работы с памятью обеспечивается использованием средств синхронизации В многопоточной среде часто возникают проблемы, связанные с использованием параллельно исполняемыми потоками одних и тех же данных или устройств. Для решения подобных проблем используются такие методы взаимодействия потоков, как взаимоисключения (мьютексы), семафоры, события. Взаимоисключения — это объект синхронизации. Только один поток владеет этим объектом в любой момент времени — одновременный доступ к общему ресурсу исключается. После всех необходимых действий мьютекс освобождается, предоставляя другим потокам доступ к общему ресурсу. Семафоры представляют собой доступные ресурсы, которые могут быть приобретены несколькими потоками в одно и то же время. Тогда дополнительные потоки должны ждать, пока требуемое количество ресурсов не будет снова доступно. Семафоры очень эффективны, поскольку они позволяют одновременный доступ к ресурсам. События объект, хранящий в себе 1 бит информации, над которым определены операции «просигнализировать», «сбросить» и «ожидать». Ожидание на просигнализированном событии есть отсутствие операции с немедленным продолжением исполнения потока. Ожидание на непросигнализированном событии приводит к приостановке исполнения потока до тех пор, пока другой поток не просигнализирует событие. 20 Способы реализации аппаратной многопоточности и их особенности. Примеры микропроцессоров. Многопоточность – это свойство платформы или программы, позволяющее процессу состоять из нескольких потоков команд, исполняющихся параллельно, без предписанного порядка во времени. Цель – более эффективное использование ресурсов компьютера Аппаратная поддержка многопоточности • Coarse-grained MT (крупнозернистая многопоточность) • Fine-grained MT (мелкозернистая многопоточность) • SMT (Одновременная многопоточность) Крупнозернистая многопоточность (Coarse-grained MT) • 2 и более аппаратных контекстов – Регистры общего назначения ALU ALU – Счетчик команд FPU – Буфер выборки инструкций MEM • Одновременно не более 1 нити • Аппаратное переключение контекстов Такты Cache miss при прерывании Мелкозернистая многопоточность (Fine-grained MT) • 2 и более аппаратных контекстов ALU – Регистры общего ALU назначения FPU – Счетчик команд MEM • Одновременно не более 1 нити Такты Cache miss Cache miss • Аппаратное переключение на каждом такте Одновременная многопоточность (Simultaneous MT) • 2 и более аппаратных контекстов ALU ALU – Регистры общего назначения FPU – Буфер выборки инструкций MEM – Буфер переупорядочивания Такты – Стек возврата • Привязка команд и нитей Поток 1 • До нескольких нитей одновременно Поток 2 • Контексты активны, переключения не происходит Ядро А Многоядерность vs многопроцессорность ALU • Меньше стоимость при той же ALU FPU производительности MEM • Выше скорость обмена между ядрами • Меньше места, меньше выделяемого тепла, меньше потребляемая мощность Поток 3 Операционная система Ядро Б ALU ALU FPU MEM Такты Ядро А Ядро Б ALU ALU ALU ALU Многопоточность на основе CMP FPU FPU • Простая логика, один поток на ядро MEM MEM • Масштабируемость за счет локальности • Условная многопоточность (Speculative MultiThreading) для ускорения последовательного кода CMP • • • • POWER 4 Barcelona Clovertown Opteron SMT • Alpha 21464 • Pentium 4 • Itanium 2 CMP + SMT • POWER 5 • UltraSPARC T2 • Keifer Такты