Контроллер прерываний К1810ВН59А - Кафедра

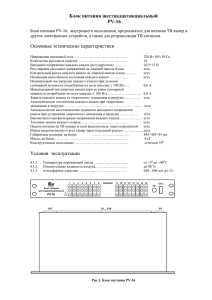

advertisement