Два варианта модернизации Системы измерения орбиты ВЭПП-4

advertisement

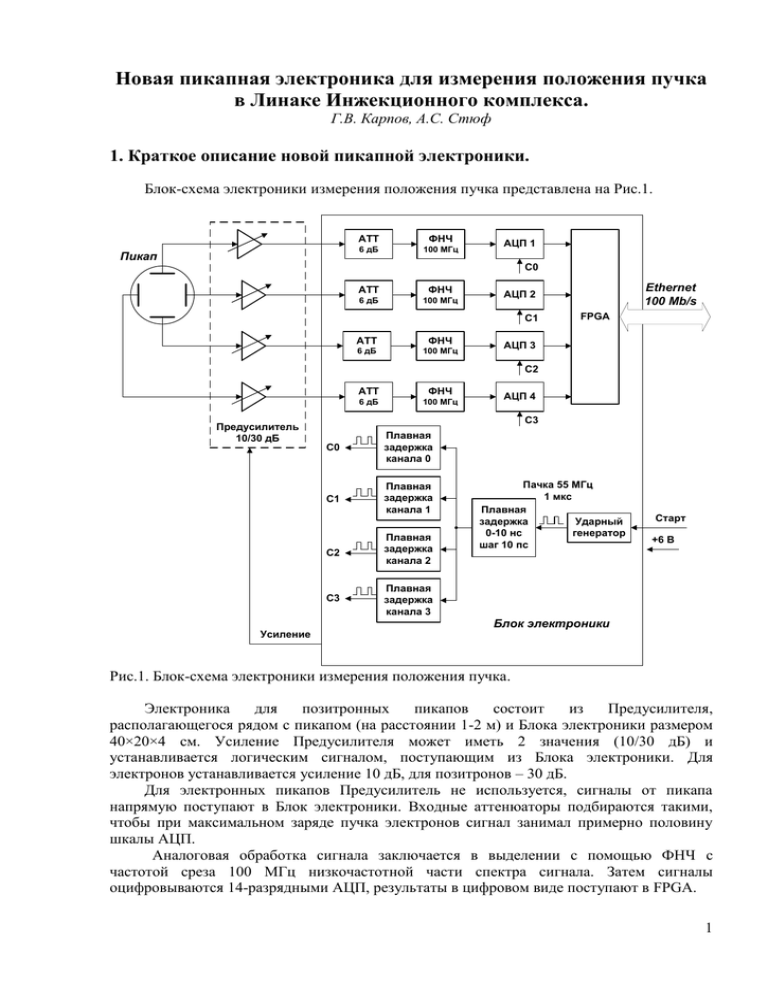

Новая пикапная электроника для измерения положения пучка в Линаке Инжекционного комплекса. Г.В. Карпов, А.С. Стюф 1. Краткое описание новой пикапной электроники. Блок-схема электроники измерения положения пучка представлена на Рис.1. Пикап ATT ФНЧ 6 дБ 100 МГц АЦП 1 С0 ATT ФНЧ 6 дБ 100 МГц С1 ATT ФНЧ 6 дБ 100 МГц Ethernet 100 Mb/s АЦП 2 FPGA АЦП 3 С2 Предусилитель 10/30 дБ Усиление ATT ФНЧ 6 дБ 100 МГц АЦП 4 С3 С0 Плавная задержка канала 0 С1 Плавная задержка канала 1 С2 Плавная задержка канала 2 С3 Плавная задержка канала 3 Пачка 55 МГц 1 мкс Плавная задержка Ударный 0-10 нс генератор шаг 10 пс Старт +6 В Блок электроники Рис.1. Блок-схема электроники измерения положения пучка. Электроника для позитронных пикапов состоит из Предусилителя, располагающегося рядом с пикапом (на расстоянии 1-2 м) и Блока электроники размером 40×20×4 см. Усиление Предусилителя может иметь 2 значения (10/30 дБ) и устанавливается логическим сигналом, поступающим из Блока электроники. Для электронов устанавливается усиление 10 дБ, для позитронов – 30 дБ. Для электронных пикапов Предусилитель не используется, сигналы от пикапа напрямую поступают в Блок электроники. Входные аттенюаторы подбираются такими, чтобы при максимальном заряде пучка электронов сигнал занимал примерно половину шкалы АЦП. Аналоговая обработка сигнала заключается в выделении с помощью ФНЧ с частотой среза 100 МГц низкочастотной части спектра сигнала. Затем сигналы оцифровываются 14-разрядными АЦП, результаты в цифровом виде поступают в FPGA. 1 Схема таймирования АЦП включает в себя Ударный генератор, общую схему плавной задержки и 4 индивидуальные схемы плавной задержки – по одной для каждого канала. Ударный генератор запускается от импульса запуска, привязанного к выстрелу пушки, и выдает в качестве CLOCK АЦП пачку импульсов частотой ~55 МГц (с периодом ~18 нс). Длительность пачки около 1 мкс. Таким образом, после выстрела пушки мы для каждого канала получаем массив из 32 точек, содержащий оцифрованный сигнал. Из этого массива выбирается 1 точка, соответствующая максимуму сигнала (его вершине). Для того, чтобы точно попасть на вершину сигнала, в блоке использована двухступенчатая плавная задержка. Первая ступень имеет диапазон задержки 10 нс, шаг регулировки 10 пс и является общей для всех каналов. Вторая ступень содержит 4 аналогичных схемы задержки, каждая из которых является своей для данного канала. Наличие индивидуальной задержки с шагом 10 пикосекунд по каждому из 4-х каналов (обрабатывающих сигналы с 4-х электродов пикапа) позволяет точно встать на вершину сигнала в каждом из каналов и не зависеть от разности длин кабелей от пикапа до Блока электроники. Временной шум схемы задержки (“джиттер”) составляет около 0.015 нс (измеренная величина). Если встать на вершину сигнала, то такой “джиттер” практически никак не сказывается на общем шуме электроники. Временная диаграмма цикла измерения показана на Рис.2. Старт Съем сигнала t0 t2 t1 t3 t4 TИ = 2 мс t5 TП = 20 - 1000 ms Рис.2. Временная диаграмма цикла измерения: - интервал времени t0-t1 – регистрация сигнала - интервал времени t2-t3 – измерение “нуля” АЦП - интервал времени t3-t4 – обработка сигнала (нахождение максимума, вычитание “нуля” и т.д.) - интервал времени t0-t4 – время измерения ТИ = 2 мс - интервал времени t4-t5 – передача данных из Блока электроники в компьютер. Примерно через 1.8 мс после прихода импульса запуска в Блоке запускается измерение нулевых уровней АЦП. Он длится около 20 мкс. Нули АЦП затем вычитаются из сигналов. Сразу после окончания цикла измерения результаты измерения (максимумы сигналов за вычетом нулей) в течение интервала времени t4-t5 посылаются в компьютер. Независимо от момента прихода в Блок электроники команды запроса на чтение данных, передаваться они будут только после окончания цикла измерения (в течение интервала времени t4-t5). 2 В Блоке электроники предусмотрена возможность накопления данных. Результаты измерения накапливаются в течение NAV циклов измерения (величина NAV программируется). В компьютер передаются уже накопленные данные. Одновременно результаты каждого цикла измерения записываются в буфер памяти емкостью 128 точек. По окончании полного цикла измерения (NAV элементарных циклов измерения) можно прочитать как накопленные данные, так и содержимое буфера. При поступлении в Блок электроники команды запроса на чтение данных, передаваться они будут только после окончания всех NAV элементарных циклов измерения. Примечание: накопления происходят без управления из вне, т.е. как только начли поступать сигналы «Start» начинают накапливаться данные. Передача результатов измерения из Блока электроники в компьютер возможна как по запросу от компьютера, так и в автоматическом режиме после каждого полного цикла измерения. Выбор режима передачи данных определяется битом 2 статусного регистра. Блок электроники содержит: 1) 7 16-битных рабочих регистра, содержащих параметры измерений; 2) 4 блока памяти по 32 16-битных ячейки, содержащих оцифрованные сигналы с электродов пикапа; 3) 4 32-битных регистра результата, содержащих максимальные коды АЦП (соответствующих вершинам сигналов), с вычетом нулевых уровней АЦП – накопленный сигнал; 4) 4 24-битных регистра нулей, содержащих нулевые уровни АЦП; 5) 4 блока памяти по 64 32-битных ячеек, содержащих результаты измерений. Примечание: в отсутствии сигналов «Start» блок будет работать только с командами на чтение и запись в регистры данных. Остальным командам требуются события, связанные с сигналом «Start» для создания ответов. Для индикации состояния блока электроники используется три светодиода: зеленый (I) – при успешной инициализации FPGA светодиод загорается. желтый (C) – загорается в случае прихода внешнего сигнала запуска («Start»). Работа по внешнему запуску должна быть разрешена, внутренний запуск – отключен. красный (R) – загорается в случае отправки блоком данных через порт Ethernet. 2. Программирование Блока электроники. Блок электроники связывается с управляющим компьютером через сеть Ethernet 100Mb/sec. Протокол в сети – UDP, но может быть и TCP IP. Каждому блоку соответствует свой IP-адрес(из диапазона 192.168.6.50-62). Порт общий у всех блоков: 2195. Стандарт работы с передаваемыми данными – big-endian. Все данные в формате integer. Минимальное отдельное слово – 16 бит или 2 байта. Команды: Управление блоками ведется с помощью команд. Команды 6-ти байтные. Посылка начинается с нулевого байта Распределение байтов в команде показано в таблице 1. Распределение битов команды: Байты команды 0-1 3-4 4-5 Поле Поле 1 Поле 2 Поле 3 Поле 4 Номера битов 15-0 15-8 7-0 15-0 Назначение Идентифик Код Адрес регистров Данные для записи ационное команды параметров иди адрес в регистры слово канала параметров 3 Поле 1: Идентификационное слово 0x2413. Используется для определения корректности пришедшей команды. В случае несовпадения идентификационного слова с маской 0x2413, команда игнорируется. Поле 2: В командах с передачей данных от FPGA 2-х байтный пакет-подтверждение приходит в начале пакета с данными. Существует 4-е варианта пакетов подтверждений (0xСС – код команды): 0xССGG – подтверждение корректной команды, где 0хGG – код с номером регистра или канала, к которому происходит обращение; 0x0011 – неверный формат команды (неправильное количество байт в полях команды); 0xСС12 – неверный идентификационный номер команды (поле 1); 0xСС14 – несуществующая команда; В конце каждой дейтаграммы присылается «хвост» 0х7FFF. Он необходим для обозначения конца информационной посылки (будь то подтверждение команды или подтверждение команды вместе с данными), который однозначно воспринимается XPortом. По приходу данных 2-х байт XPort отправляет данные в отдельной UDP-посылке (про это недавно говорил Дима). Типы команд: 1) 0x00 - запись в регистры параметров; 2) 0x01 - чтение массива данных АЦП (пакет из 4х массивов по 32 4х байтных слова). Единица измерения – квант АЦП /210; В ответ приходит 4*1024 бита данных. (4*32 4-х байтных слова). 3) 0x02 – однократно производится внутренний сигнал «Start», запускающий рабочий цикл измерения, после чего приходит передача 4х массивов данных АЦП (пакет из 128 4х байтных слов). Единица измерения – квант АЦП /210; 4) 0x04 - чтение регистров параметров; В ответ приходит 16-ти битное слово со значением регистра параметров. 5) 0x06 - чтение максимумов массивов или минимумов (в зависимости от бита 1 Register_6) АЦП (4 32-битных слова) . Единица измерения – квант АЦП /210; В ответ приходит 128 бит данных (4 32-х битных слова). 6) 0x08 - запись в регистры данных с последующим чтением (номер регистра указывается в поле 3 (адрес регистра)); В ответ приходит 2-х байтное слово со значением регистра параметров. 7) 0х09 – запуск калибровки нуля; Примечание: В рабочем режиме калибровка нуля происходит автоматически по завершению рабочего цикла измерения. В случае переконфигурации FPGA внутренние регистры со значениями ошибки нуля обнуляются, что приводит к ошибочным результатам первого рабочего цикла. Для избежания этого эффекта необходимо 4 использовать данную команду до начала измерений. Начало измерения – это первый сигнал старт после перезагрузки блока. 8) 0x0A – чтение 4-х буферов накопленных данных по завершению накопления (4*(NAV ) 4х байтных слова, где NAV – количество данных для накопления). Единица измерения – квант АЦП /210;** В ответ приходит 4*(Nav) 4-x байтных слова. 9) 0х0B – чтение 4-x буферов накопленных данных (4*(NAV) 4-x байтных слова, где NAV – количество данных для накопления). Единица измерения – квант АЦП /210. Отправка данных происходит сразу после обработки команды;** В ответ приходит 4*(Nav) 4-x байтных слова. 10) 0х0C – чтение накопленных данных по завершению накопления (4-e 4-x байтных, сумма данных, накопленных в буфере за NAV циклов измерения значений максимумов массива АЦП). Единица измерения – квант АЦП /210;** В ответ приходит 4 32-x битных слова. 11) 0х0D – чтение накопленных данных(4-e 32-х битных слова, сумма данных накопленных в буфере за NAV циклов измерения). Единица измерения – квант АЦП /210. Отправка данных происходит сразу после обработки команды;** В ответ приходит 4 32-x битных слова. Поле 3: Адрес каналов для команд с кодом 0х01, 0x07, 0x0A, 0x0B. 0-й канал имеет адрес 0х00, 1-й канал – 0х01, 2-й канал – 0х02, 3-й канал – 0х03. Адрес регистров параметров для команд с кодом 0х00, 0х04, 0х08. Используется 7 16-ти битных регистра для хранения параметров блока «BPM Processor». Адреса и значения приведены в таблице 2. Название Адрес Распределение битов регистров параметров регист ра Register_ 0 0х00 Register_ 1 0х01 Register_ 2 0х02 Register_ 3 0х03 Register_ 4 0х04 Register_ 0х05 15 ÷ 8 7÷0 Не используется Под использование юзером 15 ÷ 10 9÷0 Не используется Код общей задержки* 15 ÷ 10 9÷0 Не используется Код задержки канала 0* 15 ÷ 10 9÷0 Не используется Код задержки канала 1* 15 ÷ 10 9÷0 Не используется Код задержки канала 2* 15 ÷ 10 9÷0 5 Не используется 5 Register_ 6 0х06 Register_ 7 0x07 Register_ 8 0x08 Код задержки канала 3* 5 4 3 2 1 0 Режим передачи накоплен ных буферов: «0» - по команда м, «1» автомати чески. Разрешен ие внутренн ей генераци и стартовы х импульсо в Запреще ние внешних стартовы х импульсо в Режим передачи накопленн ых данных: «0» - по командам, «1» автоматич ески. «1» работа с электро нами, «0» работа с позитро нами. Переключе ние режима усиления сигнала: «0» усиление отключено, «1» усиление включено. 15÷7 6÷0 Не используется Количество накоплений NAV. 15÷6 5÷0 Не используется Граница массива данных АЦП, после которого ищется максимум сигнала. Значения регистров вступают в действие немедленно. При записи в регистр 0x07 происходит сброс накопления данных. Поля которые не используются при чтении всегда заполнены нулями. * Полная шкала задержки для одной микросхемы 10,24 наносекунды. Шаг – 10 пикосекунд. **Команды 0x0A, 0x0C – это синхронное чтение данных по запросу клиента. Посылка данных клиенту привязано к циклу накопления, а, именно, начинается сразу после окончания полного цикла накопления. Команды 0x0B, 0x0D – это асинхронное чтение данных по запросу клиента. Посылка данных клиенту начинается сразу после получения команды на чтение. Так, например, если при синхронном чтении пришли некорректные данные, цикл чтения можно повторить, используя команды 0x0B, 0x0D. Отличие этих команд в том, что по командам 0x0A, 0x0C посылаются данные за последний цикл накопления данных (т.е. не смотря на то, что в данный момент идет новое накопление, данные по предыдущему хранятся в памяти FPGA и их можно прочитать в любой момент по запросу от клиента). По командам 0x0B, 0x0D данные отправятся сразу по приходу команды на чтение. Поле 4: 16-ть бит данных для записи в регистры согласно таблице 2. Используются для команд с кодом 0х00 и 0х08. В остальных случаях заполнять нулями. 6 Автоматическая посылка. При записи “1” в бит 2 регистра 6 начинается автоматическая посылка мгновенных данных. После каждого цикла измерения происходит передача 20-ти байт данных согласно таблице 3. 1 1 4 4 4 4 2 0x0E Seq_NumМгновенные Мгновенные Мгновенные Мгновенные 0x7FFF порядковый данные данные данные данные номер канала 1 канала 2 канала 3 канала 4 пакета Для выключения автоматической посылки необходимо записать в бит 2 регистра 6 «0». При записи “1” в бит 5 регистра 6 начинается автоматическая посылка буферов накопления. После каждого цикла измерения происходит передача 2+4*(Nav*4)+2 байт данных согласно таблице 3. 1 1 4 4*Nav 4*Nav 4*Nav 4*Nav 2 0x0F Seq_NumNav Буфер Буфер Буфер Буфер 0x7FFF порядковый накопленны накопленн накопленн накопленн номер х данных ых данных ых данных ых данных пакета канала 1 канала 2 канала 3 канала 4 Для выключения автоматической посылки необходимо записать в бит 5 регистра 6 «0». После выключения необходимо вычитать некоторое количество пакетов до полной остановки автоматической посылки. По завершению автоматической посылки будут посылаться вместо данных байты «0х0E» либо «0х0F», соответственно. Комментарий: Лишние пакеты берутся из задержки распространения команды от программы на ПК до FPGA. Учитывая, что минимальное время повторения сигнала "START" составляет 20 мс, соответственно при нескольких сотнях миллисекунд задержки T между отключением автоматической посылки в клиентской программе и изменением состояние бита номер 2 в регистре 6, FPGA успеет послать какое-то количество пакетов с данными, где количество прямо пропорционально T обратно пропорционально периоду повторения сигнала "START". Сценарий работы с блоком. 1) При включении блока необходимо произвести инициализацию рабочих регистров, т.е. записать в них необходимые параметры (команда 0x00). 2) При первом включении после установки блоков в стойку и подключения необходимых кабелей необходимо произвести сканирование необходимых задержек для каждого блока в отдельности. Сканирование можно проводить только при наличии пучка. Для этого необходимо последовательно изменять задержку всех каналов (по одному кванту, величина которого 10 пс) используя команду записи в регистры Register_1 – Register_5 (0х00). При каждом изменении задержки читать максимумы АЦП ( команда 0х06). Максимумы из полученных 4х массивов по 2048 слов будет соответствовать задержке, при которой максимум сигнала приходится на момент оцифровки АЦП. Далее эти значения запоминаются и используются при последующей инициализации блоков после перезагрузки/выключении питания. 7 3) После инициализации блоков можно начинать их опрашивать с помощь команд 0x0A, 0х0B, 0x0C, 0x0D, 0x06. И по полученным данным считать координату. 8