1.6. Автоматизация проектирования в радиоэлектронике

advertisement

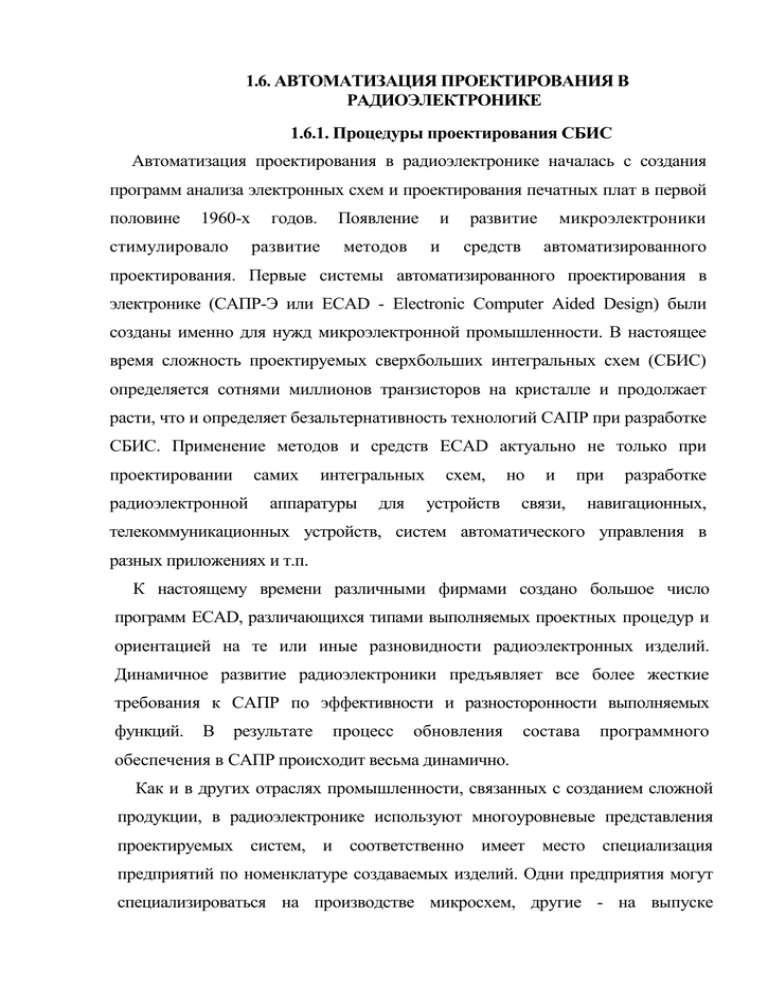

1.6. АВТОМАТИЗАЦИЯ ПРОЕКТИРОВАНИЯ В РАДИОЭЛЕКТРОНИКЕ 1.6.1. Процедуры проектирования СБИС Автоматизация проектирования в радиоэлектронике началась с создания программ анализа электронных схем и проектирования печатных плат в первой половине 1960-х стимулировало годов. Появление развитие методов и и развитие средств микроэлектроники автоматизированного проектирования. Первые системы автоматизированного проектирования в электронике (САПР-Э или ECAD - Electronic Computer Aided Design) были созданы именно для нужд микроэлектронной промышленности. В настоящее время сложность проектируемых сверхбольших интегральных схем (СБИС) определяется сотнями миллионов транзисторов на кристалле и продолжает расти, что и определяет безальтернативность технологий САПР при разработке СБИС. Применение методов и средств ECAD актуально не только при проектировании самих радиоэлектронной интегральных аппаратуры для схем, но устройств и при связи, разработке навигационных, телекоммуникационных устройств, систем автоматического управления в разных приложениях и т.п. К настоящему времени различными фирмами создано большое число программ ECAD, различающихся типами выполняемых проектных процедур и ориентацией на те или иные разновидности радиоэлектронных изделий. Динамичное развитие радиоэлектроники предъявляет все более жесткие требования к САПР по эффективности и разносторонности выполняемых функций. В результате процесс обновления состава программного обеспечения в САПР происходит весьма динамично. Как и в других отраслях промышленности, связанных с созданием сложной продукции, в радиоэлектронике используют многоуровневые представления проектируемых систем, и соответственно имеет место специализация предприятий по номенклатуре создаваемых изделий. Одни предприятия могут специализироваться на производстве микросхем, другие - на выпуске процессорных и интерфейсных плат, третьи занимаются сборкой приборов или их встраиванием в технологические, транспортные и другие системы. Очевидно, что использование продукции одного предприятия в изделиях другого, не зависимого от первого, требует, чтобы модели изделий и языки их представления соответствовали принятым стандартам. Основными HDL (Hardware Design Language) языками, используемыми в современных ECAD при функционально-логическом проектировании, начиная с описания алгоритмов и кончая представлениями логических схем, являются VHDL [10] и Verilog. Эти языки предназначены для моделирования электронных схем на уровнях вентильном, регистровых передач, корпусов микросхем. Поэтому эти языки можно назвать языками сквозного функционально-логического проектирования. Кроме языков VHDL и Verilog в ECAD находит применение ряд других языков. Среди них прежде всего следует назвать форматы EDIF (Electronic Design Interchange Format) и GIF (Caltech Intermediate Format). EDIF используют для описания топологии СБИС или списков цепей печатных плат. Он удобен для передачи данных, включающих списки соединений, параметры СБИС или печатных плат, спецификации тестовых наборов, результаты моделирования и т.п. Формат CIF применяют при передаче проекта, представленного на уровне геометрических примитивов и управляющих данных, в производство. Проектирование СБИС является многоуровневым, каждый уровень характеризуется своим математическим обеспечением, используемым для моделирования и анализа схем. Выделяют уровни системный, регистровый (RTL - Register Transfer Level), называемый также уровнем регистровых передач, логический, схемотехнический, приборно-технологический (компонентный). Общее название для регистрового и логического уровней - уровень функционально-логический. Преобладает нисходящий стиль функциональнологического проектирования, при котором последовательно выполняются процедуры уровней системного, RTL и логического. В этих процедурах широко используются ранее принятые унифицированные решения, закрепленные в библиотеках функциональных компонентов, например сумматоров, мультиплексоров, регистров и т.п. Эти библиотеки разрабатываются с помощью процедур схемотехнического и компонентного проектирования вне маршрутов проектирования конкретных СБИС. После получения результатов схемного проектирования приступают к конструкторско-технологическому проектированию, синтезу тестов и окончательной верификации принятых проектных решений. Укрупненная типичная последовательность проектных процедур на маршруте проектирования СБИС показана на рис. 1.87. Рис. 1.87. Типичный маршрут проектирования СБИС Верхний иерархический уровень называют системным, архитектурным или поведенческим. Последнее название связано с тем, что на этом уровне оперируют алгоритмами, подлежащими реализации в СБИС, которые выражают поведенческий аспект проектируемого изделия. Алгоритмы, как правило, представляются на языках проектирования аппаратуры (HDL). Далее на системном уровне формулируют требования к функциональным и схемным характеристикам, определяют общую архитектуру построения СБИС, выделяют операционные (datapath) и управляющие (FSM - Finite State Machine) блоки. Составляют расписание операций заданного алгоритма, т.е. распределяют операции по временным тактам (scheduling) и функциональным блокам (allocation). Тем самым принимают решения по распараллеливанию и/или конвейеризации операций. На уровне регистровых передач выполняют синтез и верификацию схем операционных и управляющих блоков, получают функциональные схемы СБИС. На логическом уровне, иначе называемом вентильным (gate level), преобразуют RTL-спецификации в схемы вентильного уровня с помощью программ компиляторов - логики; здесь используются библиотеки логических элементов И, ИЛИ, И-НЕ и т.п. Типичный маршрут проектирования СБИС включает в себя следующие процедуры. 1. Проверка корректности исходного алгоритма функционирования СБИС. 2. Формирование абстрактного описания проекта для перехода и функциональных к составлению расписания операций. 3. Выбор базовой технологии типов блоков из имеющейся библиотеки функциональных компонентов, которыми могут быть регистры, сумматоры, мультиплексоры и т.п. 4. Составление расписания операций, т.е. распределение операций по временным определяются тактам типы и функциональным операционных блокам. блоков При этом (комбинационные или последовательностные) и исходные данные для синтеза управляющих блоков. 5. Разработка модели устройства на уровне RTL, т.е. синтез схем операционных и управляющих блоков. 6. Верификация выбранного решения, представленного на уровне RTL. 7. Разработка модель логических вентильного схем путем с помощью уровня перевода RTL-модели компиляторов логики в и библиотек логических элементов. 8. Оптимизация и верификация логических схем. 9. Синтез схем тестирования и тестовых наборов. 10.Конструкторско-технологическое проектирование, включающее процедуры планирования кристалла, размещения компонентов и трассировки межсоединений. 11.Верификация динамических параметров схемы с учетом задержек в проведенных межсоединениях. 12.Синтез файлов с управляющей информацией для генераторов изображений. Обычно учет физических характеристик, таких, как задержки в элементах и их соединениях, осуществляют на заключительных этапах. Если быстродействие схемы оказывается неудовлетворительным, приходится выполнять дополнительные витки в итерационном цикле проектирования, что заметно удлиняет сроки разработки. Чтобы избежать этого, стараются учитывать физические характеристики (в основном это задержки) на возможно более ранних этапах нисходящего проектирования. В частности, такой учет возможен при планировании кристалла (floorplanning) уже на системном уровне. Он заключается в определении ориентировочного взаимного расположения блоков структурной схемы на кристалле (при многокристальном исполнении блоки предварительно распределяются между кристаллами) и внешних выводов блоков. Это позволяет приблизительно оценить длины связей и, следовательно, задержки в передаче данных уже в самом начале разработки. К процедурам конструкторского проектирования относят планирование кристалла, размещение компонентов и трассировку межсоединений. Расчет задержек в межсоединениях и их использование в процедуре верификации позволяют уточнить параметры быстродействия схемы. Результаты конструкторского проектирования передаются на этап синтеза файлов с управляющей информацией для генераторов изображений. В современных системах структурного синтеза на функционально-логическом уровне стремятся получить не просто работоспособное решение, но решение с оптимальным компромиссным удовлетворением требований к площади кристалла, быстродействию, рассеиваемой мощности, а в ряде случаев и к тестируемости схемы [11]. Формализация процедур структурного синтеза в общем случае затруднительна, поэтому для их эффективного выполнения обычно используют специализированные программы, ориентированные на ограниченный класс проектируемых схем. Характерные особенности технологии изготовления и проектирования имеются у микропроцессоров и схем памяти, у заказных и полузаказных СБИС (ASIC - Application-Specific Integrated Circuits), в том числе у программируемых логических интегральных схем (ПЛИС). Эти особенности обусловливают различия в методах проектирования схем и требуют их отражения в применяемом математическом и программном обеспечении ECAD. В качестве ПЛИС широко используют программируемые логические схемы CPLD (Complex Programmable Logic Device) и программируемые вентильные матрицы FPGA (Field Programmable Gate Array). В случае CPLD для отражения структуры конкретной схемы в инвариантном по отношению к приложению множестве функциональных ячеек требуется выполнить заключительные технологические операции металлизации. В случае FPGA программатор по заданной программе просто расплавляет имеющиеся перемычки (fuse) или, наоборот, создает их, локально ликвидируя тонкий изолирующий слой (antifuse). Следовательно, при использовании CPLD и FPGA необходимо с помощью САПР выбрать систему связей между ячейками программируемого прибора в соответствии с реализуемыми в схеме алгоритмами и синтезировать программы управления программатором или заключительной операцией металлизации. Ячейки могут быть достаточно сложными логическими схемами, вентилями или даже отдельными транзисторами. На производстве кристаллов ПЛИС специализируется ряд фирм, например Xilinx, Altera, Actel и другие, зачастую эти же фирмы поставляют программное обеспечение для синтеза схем на производимых ими ПЛИС. В последнее время значительное внимание уделяется процедурам совмещенного проектирования программной и аппаратной частей СБИС (SW/HW - Software/Hardware codesign). Если в традиционных маршрутах проектирования разделение алгоритмов на части, реализуемые программно и аппаратно, происходит на самых ранних шагах, то в технологии совмещенного проектирования эта процедура фактически переносится на уровень RTL и тем самым входит в итерационный проектный цикл и может привести к более обоснованным проектным решениям. Примером подхода к совмещенному проектированию может служить методика моделирования на уровне исполнения системы команд, в соответствии с которой моделируются события, происходящие на внешних выводах таких устройств, как арифметикологическое, встроенная и внешняя память, системная шина и т.п. Благодаря совмещенному проектированию удается не только на ранних стадиях проектирования найти и исправить возможные ошибки в аппаратной и программной частях проекта, но и отладить контролирующие тесты [12]. Совмещенное проектирование аппаратных и программных частей успешно применяется при проектировании систем на кристалле (SoC - System-on-Chip) для встроенной аппаратуры. При этом аппаратная часть целевого процессора представляется моделью уровня системы команд. Модель может быть описанием архитектуры процессора или расписанием работы шины процессора на языке VHDL, но возможно использование и аппаратного тестера. При этом скорость моделирования сравнительно невелика. Повышения производительности достигают в том случае, если моделирование операций обращения к памяти выполняют не в аппаратном, а в логическом симуляторе. Для проверки работоспособности и оценки параметров синтезированных схем применяют процедуры анализа (верификации) функциональных и логических схем. Чаще всего их верифицируют с помощью программ моделирования, ориентированных на уровни системный, RTL или вентильный. В итерационном цикле проектирования моделирование должно осуществляться многократно: сначала оно выполняется с сугубо ориентировочными значениями задержек, затем после этапа топологического проектирования повторяется уже с учетом уточненных задержек, обусловленных паразитными параметрами межсоединений. Следует отметить, что в СБИС проводники имеют малые площади поперечных сечений и, следовательно, увеличенное сопротивление, это приводит к тому, что по мере уменьшения проектных норм начинают доминировать задержки в межсоединениях (например, 60...70 % общей задержки в схеме в случае 0,5 мкм технологии и 80...90 % в случае 0,25 мкм технологии приходится на межсоединения). Эти задержки имеют заметный разброс и существенно влияют на быстродействие схемы. Поэтому во многих программах логического моделирования имеются модели проводников, с их помощью рассчитываются задержки в зависимости от результатов трассировки. Чтобы определить значения параметров схемы, полученные после топологического проектирования, используют специальные программы уточнения задержек (экстракция параметров). Для этих целей возможно применение и программ схемотехнического моделирования. Вследствие разнообразия типов схем и проектных процедур в современных развитых САПР можно увидеть большое число программ различного назначения. В программах временного анализа на функционально-логическом уровне преимущественно используют событийное (event-driven) асинхронное логическое моделирование с многозначной логикой. Наряду с асинхронным находит применение синхронное моделирование, быстродействие которого на один-два порядка выше, чем у событийного временного анализа [13]. Синхронное моделирование отличается тем, что на каждом такте синхросигналов определяется установившееся состояние схемы, а переходные процессы не рассматриваются. При этом обычно используется двузначная логика, реже четырехзначная. Но синхронное моделирование не позволяет верифицировать схему в достаточной мере. Поэтому принимаются меры к повышению эффективности асинхронного событийного анализа. Еще более высокое быстродействие верификации можно получить в системах эмуляции логики, в которых по исходному описанию схемы на уровнях вентильном или RTL происходит ее параллельная эмуляция на аппаратных ускорителях. Другое направление сокращения времени на проверку корректности решений, принимаемых при функционально-логическом проектировании, связано с методами формальной верификации. В этих методах вместо многократного моделирования схемы при различных тестовых воздействиях выполняют сопоставление проектного решения с некоторым эталоном методами, развиваемыми в теории дедуктивных систем [14]. Различают два подхода к формальной верификации [15]. Первый из них применяют для установления соответствия описаний схемы на разных иерархических уровнях. Этот подход называют проверкой эквивалентности (equivalence checking). Обычно с его помощью проверяют корректность синтезированной вентильной схемы, а в качестве эталона используют исходное RTL-описание. Второй подход называют верификацией моделей (model checking). Он характерен тем, что сопоставляются функции, выполняемые объектами, представленными своими моделями. Применение этого подхода, относящегося к более высоким уровням абстракции, требует хорошей математической подготовки пользователей. Результаты логического синтеза в виде VHDL- или Verilog-описания используются далее для синтеза тестов и поступают на этап конструкторского проектирования СБИС. Актуальность проблемы тестирования обусловлена ограниченными управляемостью и наблюдаемостью СБИС, поскольку при десятках-сотнях миллионов транзисторов на кристалле имеется лишь несколько сотен внешних выводов. Синтез и анализ тестов занимают до 35 % времени в цикле проектирования СБИС, и, несмотря на такие затраты, удается разрабатывать тесты с приемлемой полнотой обнаружения константных неисправностей только для комбинационных схем. Поэтому проблема тестируемости СБИС сохраняет постоянную актуальность. Для решения проблем тестирования в СБИС используют специальные методы проектирования сканирования, самих микросхем. преобразующие в Это, во-первых, режиме методы тестирования последовательностные схемы в комбинационные. Методы сканирования основаны на объединении триггеров, имеющихся в схеме или специально вводимых в нее, в один или несколько сдвигающих регистров, управляющих состоянием схемы и управляемых через последовательный вход. Во-вторых, это методы самотестирования (BIST - Built-in Self-Test), основанные на встраивании в кристалл генераторов тестовых наборов [16] и схем, сжимающих результаты проверки основной части СБИС при этих тестовых наборах. Среди методов сканирования значительное внимание уделено методу граничного сканирования (BS - Boundary-Scan) [17], предназначенному преимущественно для проверки межсоединений на печатных платах и в многокристальных СБИС. Для этого в каждый чип вводятся сдвигающие регистры, состоящие из ячеек по одной на каждый внешний вывод. Благодаря ячейкам можно при проверке межсоединений отключать внутрикристальные цепи, а при проверке логической схемы подключать или внутренние сканирующие регистры, или (в случае BIST) генераторы тестовых наборов и схемы компрессии результатов [18]. Для подключения платы к тестирующему по BS прибору достаточно пяти проводов. Для целей проектирования схем с граничным сканированием разработаны специальный стандарт ШЕЕ 1149.1 и языки BSDL и HSDL (Boundary and Hierarchical Scan Description Languages), являющиеся подмножеством VHDL. Язык HSDL расширяет возможности BSDL на более высокие иерархические уровни. Очевидно, что проектирование схем тестирования целесообразно вьшолнять совместно с синтезом основных схем, т.е. на уровнях RTL и вентильном. Основой программного обеспечения конструкторского проектирования в ECAD являются средства топологического проектирования, среди которых выделяют программы разработки топологии (layout) кристаллов СБИС, многокристальных СБИС и печатных плат. Конструкторское проектирование СБИС включает ряд процедур. Разрезание (partitioning или компоновка) заключается в группировании компонентов по критерию связности, что нужно или для размещения формируемых групп в отдельных чипах при многокристальной реализации, или для определения их взаимного расположения в одном кристалле в процессе выполнения последующей процедуры планировки (floorplanning) кристалла. Группы при планировании представляются в виде прямоугольников, их расположение обычно определяется в интерактивном режиме, но находят применение также генетические алгоритмы. Далее следуют процедуры размещения (placement) компонентов, трассировки (routing) соединений, сжатия (compaction) топологической схемы, проверки соответствия топологической и принципиальной схем, подготовки информации для генераторов изображений. Ответственность процедуры размещения определяется доминирующим влиянием на быстродействие задержек именно в межсоединениях. Трассировка состоит из фаз глобальной, во время которой намечается положение трасс, и детальной, которая, в свою очередь, делится на канальную (channel) и локальную (switchbox). Канальная трассировка служит для конкретизации положения трасс в каналах, а локальная - для проведения соединений между каналами и контактами компонентов. Сжатие топологии выполняется во всех направлениях и позволяет уменьшать занимаемую схемой площадь. После исполнения операций размещения и трассировки следует оценка задержек и занимаемой площади, и если требования к этим параметрам не удовлетворены, то нужны дополнительные итерации для приближения к оптимальным результатам. При нисходящем проектировании в предшествующих процедурах приходится задаваться ориентировочными значениями данных, истинные значения которых становятся известными только после выполнения последующих процедур. Это обстоятельство обусловливает итерационный характер процесса проектирования с возвратами от последующих этапов к предыдущим, что, естественно, существенно увеличивает затраты на проектирование. Поэтому усилия разработчиков системных вопросов ECAD направлены на поиск методов сокращения числа итераций в цикле проектирования СБИС. Такой поиск привел к положительным результатам, по крайней мере, в следующих двух направлениях. Во-первых, это технологии так называемого физического проектирования, в которых стараются уже на ранних архитектурном и регистровом этапах проектирования учесть физические параметры (задержки, рассеиваемые мощности). Осуществляется такой учет благодаря разработке методов совместного решения задач, ранее выполнявшихся раздельно (например, задач синтеза RTL-схем и схем граничного сканирования). Во-вторых, это разумное сочетание элементов нисходящего и восходящего проектирования, при котором на ранних этапах проектирования ориентировочно распределяются задержки и мощности между блоками, что позволяет далее проектировать эти блоки независимо друг от друга. И если принятые ранее значения параметров блоков оказываются выполнимыми, то дополнительные итерации не требуются. При проектировании интегральных схем процедуры схемотехнического проектирования применяют в основном в процессе отработки библиотек функциональных компонентов СБИС. Но при проектировании принципиальных электрических схем радиоэлектронных устройств в различных приложениях эти процедуры могут стать основными, наряду с процедурами конструкторского проектирования печатных плат. Схемотехнический анализ может потребоваться также и внутри маршрута проектирования СБИС. Так, в случае МОП-схем появляется промежуточный уровень абстракции (switch level) между схемотехническим и вентильным уровнями, на котором элементами моделей являются не вентили, а МОПтранзисторы. Благодаря представлению последних в виде переключателей удается отобразить процессы в схеме более детально, чем с помощью программ логического моделирования. Имеются также предложения по распространению возможностей схемотехнического моделирования на схемы с десятками тысяч транзисторов [19]. Математическое обеспечение схемотехнического анализа (анализа электронных схем) составляют модели электронных компонентов, методы формирования математических моделей схем в виде систем обыкновенных дифференциальных уравнений и методы численного интегрирования этих систем. Схемотехническое проектирование радиотехнических (RF) схем отличается рядом особенностей математических моделей и используемых методов, прежде всего в области СВЧ-диапазона. Для анализа линейных схем обычно применяют методы расчета полюсов и нулей передаточных характеристик. Моделирование стационарных режимов нелинейных схем чаще всего выполняют с помощью метода гармонического баланса, основанного на разложении неизвестного решения в ряд Фурье, подстановкой разложения в систему дифференциальных уравнений с группированием членов с одинаковыми частотами тригонометрических функций, в результате получаются системы нелинейных алгебраических уравнений, подлежащие решению. Сокращение времени в случае слабо нелинейных схем достигается при моделировании СВЧ-устройств с помощью рядов Вольтерра. Анализ во временной области для ряда типов схем выполняют с помощью программ типа Spice путем интегрирования систем обыкновенных дифференциальных уравнений. Приборно-технологическое (компонентное) проектирование предназначено для проектирования приборов (компонентов) интегральных схем. Обычно выделяют вертикальное проектирование, касающееся диффузионного профиля (формирования областей в направлении, перпендикулярном поверхности кристалла), и горизонтальное (формирование вида интегрального прибора в поверхностной плоскости). Компонентное проектирование называют также физическим, относя к нему спроектированных межсоединений. процедуры экстракции параметров Моделирование технологических процессов изготовления СБИС относят к технологическому проектированию, поддерживаемому соответствующими программами ECAD. Технологическое проектирование печатных плат заключается в преобразовании результатов конструкторского проектирования в файлы управляющей информации для фотоплоттеров и сверлильных станков с ЧПУ.