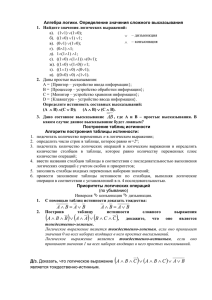

Основы цифровой техники, издание 1-е -

advertisement