Генераторы импульсов с электронной перестройкой частоты

advertisement

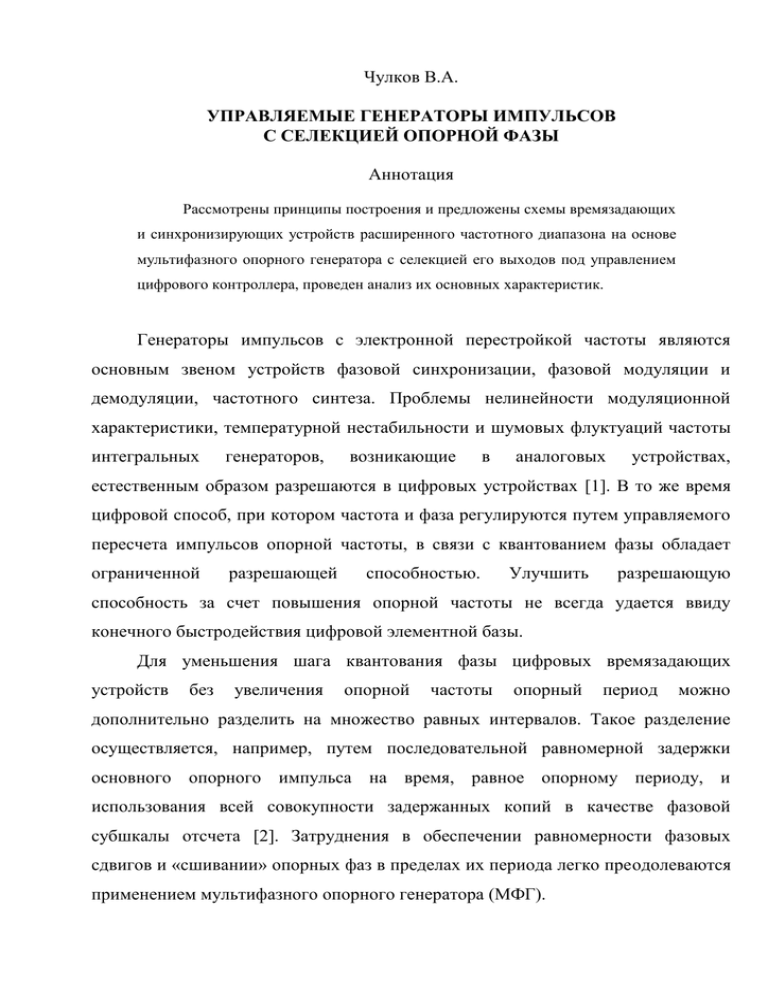

Чулков В.А. УПРАВЛЯЕМЫЕ ГЕНЕРАТОРЫ ИМПУЛЬСОВ С СЕЛЕКЦИЕЙ ОПОРНОЙ ФАЗЫ Аннотация Рассмотрены принципы построения и предложены схемы времязадающих и синхронизирующих устройств расширенного частотного диапазона на основе мультифазного опорного генератора с селекцией его выходов под управлением цифрового контроллера, проведен анализ их основных характеристик. Генераторы импульсов с электронной перестройкой частоты являются основным звеном устройств фазовой синхронизации, фазовой модуляции и демодуляции, частотного синтеза. Проблемы нелинейности модуляционной характеристики, температурной нестабильности и шумовых флуктуаций частоты интегральных генераторов, возникающие в аналоговых устройствах, естественным образом разрешаются в цифровых устройствах [1]. В то же время цифровой способ, при котором частота и фаза регулируются путем управляемого пересчета импульсов опорной частоты, в связи с квантованием фазы обладает ограниченной разрешающей способностью. Улучшить разрешающую способность за счет повышения опорной частоты не всегда удается ввиду конечного быстродействия цифровой элементной базы. Для уменьшения шага квантования фазы цифровых времязадающих устройств без увеличения опорной частоты опорный период можно дополнительно разделить на множество равных интервалов. Такое разделение осуществляется, например, путем последовательной равномерной задержки основного опорного импульса на время, равное опорному периоду, и использования всей совокупности задержанных копий в качестве фазовой субшкалы отсчета [2]. Затруднения в обеспечении равномерности фазовых сдвигов и «сшивании» опорных фаз в пределах их периода легко преодолеваются применением мультифазного опорного генератора (МФГ). Ц е л ь р а б о т ы - установление схемных принципов и выяснение основных свойств управляемых генераторов импульсов с селекцией опорной фазы МФГ при их применении в качестве типовых радиотехнических устройств. МФГ в общем случае представляет собой секционированную линию задержки (ЛЗ) с инверсной обратной связью (рис.1), на промежуточных отводах которой образуется множество опорных фаз от 0 до . Для получения группы выходов с фазами в диапазоне от до 2 и обеспечения надлежащей нагрузочной способности схема снабжена буферными фазорасщепителями. Число секций ЛЗ выбирается таким, чтобы получить необходимый шаг квантования фазы 2 / N , причем N для удобства цифровой селекции опорной фазы берется равным целой степени двойки ( N 2 a ). Линия задержки может использовать разные физические принципы задержки импульса, однако практически целесообразно строить ее секции в виде электронных элементов задержки. В таком исполнении при достаточной идентичности секций (отсутствуют явления затухания и растягивания фронта импульса по мере его распространения по ЛЗ) появляется возможность электронного управления временем задержки. На рис.2 показан вариант реализации электронной ЛЗ на дифференциальных приемниках с линии ЭСЛ типа, обладающей одинаковой задержкой при передаче как положительного, так и отрицательного фронтов импульса. Время задержки каждой секции ЛЗ задается значениями R и C и зависит от управляющего напряжения UУПР, выбираемого в пределах -(2,6...5,2)В, в соответствии с выражением t U 0 U1 , RC ln 1 3 0 1 U U 2UУПР где U0 и U1 - высокий и низкий уровни напряжения ЭСЛ сигналов. Возможность электронной перестройки t позволяет известными средствами стабилизировать частоту МФГ или подстроить ее к частоте внешнего источника. Обобщенная структура управляемого генератора с селекцией опорной фазы (рис.3) включает МФГ, мультиплексор и цифровой контроллер, осуществляющий выбор той или иной фазы МФГ в соответствии с назначением устройства. Выходы МФГ общим количеством 2а соединены с соответствующими информационными входами мультиплексора, а выходы контроллера общим числом а - с его адресными входами. Цифровой отсчет фазы входных Х и выходных Y импульсов осуществляется контроллером по субшкале МФГ, причем значение текущей фазы выходных импульсов отражается адресным кодом мультиплексора, а входных - кодом состояний выходов МФГ, зафиксированным в момент поступления входных импульсов. В простейшем случае контроллер отсутствует и входной цифровой сигнал Х поступает непосредственно на адресный вход мультиплексора (А = Х). Так как число Х задает в двоичном коде порядковый номер опорной фазы МФГ, подключаемой мультиплексором к выходу Y, то устройство выполняет функции фазового модулятора с цифровым управлением. Коэффициент преобразования числа Х в фазу импульса Y составляет 2 /2a рад/ед. В ряде применений фаза генерируемых импульсов должна модулироваться по заданной программе, например при имитации в измерительных целях фазоманипулированных сигналов данных. В таких генераторах импульсов может осуществляться автономное регулирование фазы без подачи входного воздействия Х. Контроллер в этом случае представляет собой формирователь последовательности адресных кодов и выполняется на основе счетчика и комбинационной схемы (КС) (рис.4а). Модуль счетчика выбирается равным длине цикла повторения кодового образца, а тактовый вход его подключается к выходу Y с тем, чтобы исключить дребезг фронтов генерируемых импульсов в момент изменения адресного кода. На рис.4б представлена структурная схема генератора фазового шума [3], в котором выходные импульсы подвергаются случайному фазовому дрожанию с заданными статистическими характеристиками. Здесь для модуляции фазы импульсов Y используется генератор псевдослучайных чисел (ГПСЧ), у которого, как известно [4], сумма содержимого группы смежных разрядов базового регистра сдвига обладает близким к нормальному распределением. Мультиплексор, соединенный адресными входами с выходом комбинационного сумматора группы одноразрядных чисел, преобразует псевдослучайное число в фазовый сдвиг выходного импульса. Степень «случайности» фазовых сдвигов тем выше, чем большее количество разрядов ГПСЧ участвует в суммировании. Если число разрядов в сдвигающем регистре ГПСЧ равно n и используется mразрядный сумматор, то фазовое дрожание генерируемых импульсов характеризуется среднеквадратическим отклонением 1 /( 2n lbm 3 и шириной энергетического спектра от f O /( 2 Электронная перестройка частоты n fO ) 1 ) до 0 ,6 f O . в управляемом генераторе рассматриваемого типа производится косвенным способом за счет нарастающего приращения фазы выходных импульсов. С этой целью контроллер выполняется в виде накапливающего сумматора (цифрового интегратора), который образован с помощью обратной связи одного из цифровых входов сумматора через регистр (рис.5). Если входной код Х = 0, то адрес А мультиплексора остается неизменным и он подключает к своему выходу Y один и тот же выход МФГ. Поэтому частота выходных импульсов fY оказывается точно равной опорной частоте fO МФГ. Если код Х отличается от нуля, то после выработки очередного выходного импульса код адреса А мультиплексора получает приращение, в результате чего он выбирает в качестве Y выход МФГ с порядковым номером на Х больше. При этом период выходных импульсов становится больше (или меньше при отрицательном Х) опорного периода МФГ на величину Х t, а частота при Х t << 1/fO составит fY Соотношение N (1 X / 2a ) f O . 2 a , связывающее количество фаз МФГ с числом адресных входов мультиплексора, равным разрядности накапливающего сумматора, обеспечивает суммирование по модулю N (2 ), что отвечает периодическому характеру процессов в схеме: переполнению разрядной сетки сумматора с отбрасыванием переноса соответствует выбор надлежащей фазы МФГ в следующем его периоде. Для того, чтобы генератор мог работать с управляющим кодом Х произвольного знака, суммирование производят в дополнительном коде. Добавлением ко входу аналого-цифрового преобразователя можно получить генератор, управляемый напряжением [5]. Принцип селекции опорной фазы позволяет достаточно просто осуществить синтез частот или образовать сетку связанных с опорной частот. На рис.6 показана схема управляемого генератора, в котором к опорной частоте fO МФГ прибавляется (или вычитается из нее) часть, пропорциональная частоте внешнего источника fX. В этой схеме контроллер представляет собой реверсивный счетчик импульсов, на тактовый вход С которого поступают импульсы управляющей частоты, а на вход V реверса - логический уровень, определяющий знак добавки к опорной частоте. С каждым входным импульсом Х в зависимости от направления счета счетчик изменяет адрес мультиплексора на 1, что приводит к последовательному перебору мультиплексором опорных фаз МФГ в порядке нарастания или уменьшения их номеров. Частота выходных импульсов Y благодаря монотонному приращению фазы оказывается равной fY fO f X / 2a , где знак «+» соответствует режиму вычитания счетчика, а «-» - режиму суммирования. Коррекция периода выходных импульсов на происходит в каждом i-ом периоде, где i t 1 / 2n fO f O / f X . В частном случае, когда fX = fO и тактовый вход счетчика соединен либо с одним из выходов МФГ, либо с основным выходом Y, коррекция выполняется в каждом периоде и выходная частота равна f Y f O ( 1 1 / 2 n ). Для образования сетки частот общие МФГ и счетчик снабжаются множеством мультиплексоров по одному на каждую выходную частоту, причем адресные входы мультиплексоров подключаются к разным смежным группам выходов счетчика, разрядность которого для данного применения может быть увеличена. В устройствах фазовой синхронизации генераторов с селекцией опорной фазы в отличие от способа фазовой автоподстройки частоты (ФАПЧ) осуществляется непосредственное воздействие на фазу генератора. В качестве сигнала обратной связи берется либо выходной импульс генератора, либо цифровой эквивалент его фазы - адрес мультиплексора. В первом случае контроллер фиксирует лишь знак фазовой разности входного и выходного дискриминационной сигналов и, характеристикой. следовательно, Контроллером обладает релейной может служить реверсивный счетчик, который совмещает функции фазового компаратора и интегрирующего цифрового фильтра [6]. Заметим, что по меньшей мере один интегратор необходим в любом исполнении контроллера для придания системе астатизма как условия слежения за частотой входных сигналов. Схема устройства синхронизации с поясняющими диаграммами показана на рис.7. Если при поступлении очередного входного сигнала Х его фронт приходится на низкий уровень сигнала Y , то фиксируется отставание выходного сигнала и от содержимого счетчика отнимается 1. Уменьшившийся адрес мультиплексора обусловливает в следующем периоде регулирования передачу на выход фазы МФГ с меньшим порядковым номером. Это означает коррекцию фазы выходного импульса в направлении компенсации фазовой ошибки. Так продолжается до тех пор, пока знак фазовой ошибки не изменится на противоположный и счетчик перейдет в режим суммирования. В дальнейшем фаза сигнала Y отслеживает изменения фазы сигнала Х с погрешностью, не превышающей с = 2 /N. Как и в системе ФАПЧ первого порядка полоса захвата совпадает с полосой синхронизации (удержания), которая в относительных единицах достигает fc Max fX fO fO 1 N 1 . В процессе установления синхронизма происходит линейное приближение фазы Y к фазе Х со скоростью, зависящей от начальной расстройки по частоте fH ( fX f O ) / f O . Время установления синхронизма tC H / 2 fO ( fC fH ) возрастает с увеличением начальных расстроек по частоте fН и по фазе максимальное значение имеет место при Н Н, его = . Если tС можно сократить за счет записи исходного адреса в счетчик по первому же входному сигналу, то повысить точность удается только в ущерб частотной полосе синхронизации. Поэтому предпочтительной оказывается пилообразная форма дискриминационной характеристики, которая в условиях значительной дисперсии входной фазы обеспечивает также меньшую вероятность срыва синхронизации. Пилообразная форма характеристики предполагает пропорциональное преобразование фазовой ошибки в число. В системе с селекцией опорной фазы такое преобразование выполняется цифровым отсчетом по субшкале МФГ фаз входного и опорного сигналов с последующим вычислением их разности по модулю 2 [7]. Контроллер в схеме такого устройства фазовой синхронизации (рис.8) состоит из параллельного регистра (RG), шифратора (CD), вычитателя (SB) и аккумулятора (накапливающего сумматора АС). Шифратор совместно с Nразрядным регистром образует двоичный код фазы каждого входного сигнала как порядковый номер выхода МФГ, импульс на котором синфазен входному сигналу. Вычитатель SB выполняет фазовое сравнение, вычисляя разность фаз (ФХФY) по модулю 2 по известным кодам шифратора и адреса мультиплексора. Вычитание как процедура суммирования в дополнительном коде дает результат также в дополнительном коде, что удобно для его последующей обработки аккумулятором АС. Выход заема вычитателя игнорируется, а старший разряд разности считается знаковым, что ограничивает апертуру дискриминационной характеристики участком Чтобы обеспечить и устраняет эффект частотной дискриминации. фильтрацию фазовых девиаций количество разрядов аккумулятора должно быть больше числа адресных входов мультиплексора, соединенными с группой старших его выходов. Тогда в коррекции адреса участвует определенная часть фазовой разности. Форсированный захват можно осуществить путем кратковременного сдвига кода разности в разрядной сетке аккумулятора в сторону старших разрядов. Анализ линеаризованной модели устройства синхронизации с пилообразной характеристикой фазового сравнения дает общее решение для полной фазы выходного сигнала ФY ( s ) где О и Х s O 2 F( s ) s Н X 2 [ 1 F ( s )], s - угловые опорная и входная частоты, F(s) - коэффициент передачи цифрового фильтра. В рассматриваемом устройстве с одним интегратором (аккумулятором) F(s) = K1/s и решение в области оригиналов ФY ( t ) X t ( X O K1 H )(1 e K1t ) носит характер апериодического приближения. Установившаяся фазовая ошибка тем меньше, чем выше коэффициент K1 интегратора. Повышение порядка системы при введении второго интегратора ( F(s) = K1(s+K2)/s2) приводит к астатизму в отношении фазы с устранением фазовой ошибки при постоянной входной частоте. Решение в этом случае содержит затухающую гармоническую составляющую ФY ( t ) ФX ( t ) A где коэффициенты A, и He K1t / 2 sin( t ), определяются частотной расстройкой ( Х - О) и значениями К1, К2. Таким образом, характеристики устройства фазовой синхронизации аналогичны характеристикам устройства ФАПЧ с меньшим на единицу порядком фильтра [1], поскольку при ФАПЧ функцию одного из интеграторов выполняет сам управляемый генератор. Система с селекцией опорной фазы подобна цифровой системе ФАПЧ с повышенной в N раз опорной частотой, поэтому в ней в N раз снижаются требования к быстродействию элементов. Возможная ввиду технологического разброса секций МФГ неравномерность распределения опорных фаз практически не отражается на фазовом шуме квантования 2 выходного сигнала, оцениваемом дисперсией 4 2 / 12 N 2 . Принцип синхронизации с фазовой селекцией следует рассматривать как альтернативу цифровой ФАПЧ при проектировании систем обработки информации повышенного быстродействия или точности. Благодаря уменьшению шага квантования фазы при сохранении цифрового способа регулирования с возможностью электронной стабилизации опорной частоты рассмотренные устройства на управляемых генераторах с селекцией опорной фазы обладают повышенной точностью и расширенным диапазоном рабочих частот. Предложенный принцип построения радиотехнических времязадающих и синхронизирующих устройств может оказаться полезным в различных областях радиоэлектроники, в частности в системах передачи и декодирования фазо- и частотно-модулированных данных, при формировании и цифровом измерении интервалов времени, фазовых сдвигов и частоты, обработке псевдошумовых сигналов. Литература 1. Цифровые системы фазовой синхронизации/М.И. Жодзишский, С.Ю. Сила-Новицкий, В.А. Прасолов и др.; Под ред. М.И. Жодзишского. - М.: Сов.радио, 1980. 2. Патент №0240232 (ЕПВ) Цифровая петля фазовой автоподстройки. Изобретения стран мира, вып.133, 1988, №11. 3. Чулков В.А. - Приборы и техника эксперимента, 1996, № 2. 4. Хоровиц П., Хилл У. Искусство схемотехники: В 2-х т. Т.2. - М.: Мир, 1986. 5. Патент №2103816 (РФ) Управляемый напряжением генератор импульсов /Чулков В.А.. 6. Чулков В.А. - Вопросы радиоэлектроники, сер.ЭВТ, 1990, вып.13. 7. Патент №2119717 (РФ) Устройство фазовой синхронизации /Чулков В.А. t 1 Ф0 ФN/2 t 1 Ф1 ФN/2+1 > t 1 Ф2 ФN/2+2 1 > Фi+1 ФN/2+i+1 C C R ФN/2-1 ФN-1 R R UУПР Рис.2. Вариант электронной ЛЗ на ЭСЛ приемниках с линии Рис.1. Структура МФГ МФГ D MX Y X Фi ФN/2+i > R t > Контроллер A Рис.3. Обобщенная структура управляемого генератора с селекцией опорной фазы МФГ D MX Y A SM D RG A X B C Рис.5. Управляемый кодом генератор МФГ МФГ D MX Y D MX Y С fX «+/-» СТ С X A СТ2 A +/- V Рис.6. Управляемый частотой генератор Рис.7. Устройство синхронизации с релейной дискриминационной характеристикой МФГ D MX Y D RG CD A SВ D АС A B C C X Рис.8. Устройство синхронизации с пилообразной дискриминационной характеристикой