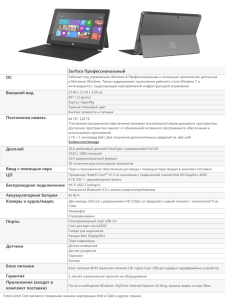

Память программ

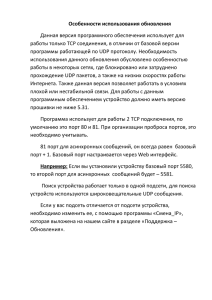

advertisement