Архитектура и система команд ЦСП семейства ADSP-21XX

advertisement

Министерство образования и науки Российской Федерации

ФГАОУ ВПО «УрФУ имени первого Президента России Б.Н.Ельцина»

А. А. Дурнаков, Н. А. Дядьков

АРХИТЕКТУРА И СИСТЕМА КОМАНД

ЦИФРОВЫХ СИГНАЛЬНЫХ ПРОЦЕССОРОВ

СЕМЕЙСТВА ADSP - 21XX

Учебное электронное текстовое издание

Подготовлено кафедрой «Радиоэлектроника информационных систем

Научный редактор доц., канд. техн. наук В. А. Добряк

Методические указания к лабораторной работе по курсу

«Электроника и схемотехника» для студентов всех форм обучения

специальностей 090106 – Информационная безопасность

телекоммуникационных систем; 230201 – Информационные

системы и технологии; направления 230400 − Информационные

системы и технологии, направления 210400 − Радиотехника

Предназначены для выполнения лабораторного практикума.

Содержат описание архитектуры цифровых сигнальных

процессоров семейства ADSP-21XX фирмы Analog Devices,

систему команд, введение в интегрированную среду разработки

VisualDSP++, пояснения к разработке учебной программы, задания

для самостоятельной работы.

УрФУ, 2012

Екатеринбург

ОГЛАВЛЕНИЕ

ЦЕЛЬ И СОДЕРЖАНИЕ РАБОТЫ ...........................................................................3

БАЗОВАЯ АРХИТЕКТУРА СЕМЕЙСТВА ADSP-21XX ......................................3

2.1. Особенности структуры ...................................................................................3

2.2. Вычислительные модули .................................................................................6

2.3. Генераторы адресов данных. Программный автомат ...................................9

2.4. Оперативная память .......................................................................................10

2.5. Шины ...............................................................................................................11

2.6. Внутренние периферийные устройства........................................................11

2.7. Программно-логическая модель ...................................................................14

3.

СИСТЕМА КОМАНД ...............................................................................................17

3.1. Команды АЛУ .................................................................................................18

3.2. Команды умножителя-накопителя ................................................................20

3.3. Команды устройства сдвига ..........................................................................21

3.4. Команды пересылки данных .........................................................................22

3.5. Команды передачи управления в программе ...............................................23

3.6. Многофункциональные команды..................................................................24

3.7. Другие команды ..............................................................................................25

4.

ФОРМАТЫ ПРЕДСТАВЛЕНИЯ ЧИСЕЛ ..............................................................26

5.

ЗАПУСК СРЕДЫ РАЗРАБОТКИ ПРОГРАММ ....................................................31

5.1. Создание проекта ............................................................................................33

5.2. Создание файлов кода программы ................................................................35

5.3. Компиляция и компоновка ............................................................................36

5.4. Тестирование и отладка .................................................................................37

6.

ЛАБОРАТОРНОЕ ЗАДАНИЕ .................................................................................42

КОНТРОЛЬНЫЕ ВОПРОСЫ .............................................................................................43

1.

2.

1. ЦЕЛЬ И СОДЕРЖАНИЕ РАБОТЫ

Целью работы является изучение архитектуры и системы команд

цифрового сигнального процессора фирмы Analog Devices ADSP-2181, а также

интегрированной среды разработки VisualDSP++, предназначенной для

разработки и отладки программного обеспечения всего семейства процессоров

ADSP-21xx. Работа рассчитана на 4 часа занятий в лаборатории и 8 часов

домашней подготовки.

При подготовке к работе изучается структура и система команд

процессора фирмы Analog Devices ADSP-2181. В работе по приведенному

примеру необходимо создать программу генерации гармонического сигнала.

Самостоятельно создать и отладить программы, реализующие различные виды

модуляции гармонических сигналов.

В лаборатории на простом примере изучаются этапы технологии

разработки и отладки программ, основные приёмы работы со средой

VisualDSP++.

2. БАЗОВАЯ АРХИТЕКТУРА СЕМЕЙСТВА ADSP-21XX

2.1. Особенности структуры

Лидирующее положение в области разработки и производства цифровых

сигнальных процессоров (ЦСП) занимают фирмы Analog Devices, Texas

Instruments, Motorola, AT&T Microelectronics и ST Microelectronics. Отличия

заключаются в арифметических блоках, производительности, разрядности шин

данных,

в

структуре

внутренних

регистров,

во

встроенных

модулях

интерфейсов и модулях предварительной обработки.

Несмотря на многообразие процессоров, все они спроектированы так,

чтобы оптимизировать выполнение наиболее часто встречающейся операции

цифровой

обработки

сигналов

(ЦОС)

−

умножения

с

накоплением

(суммированием) результатов. Можно выделить пять основных требований,

которым должны удовлетворять современные ЦСП:

1) быстрое выполнение арифметических операций;

3

2) повышенная точность представления операндов;

3) возможность одновременной выборки двух операндов;

4) поддержка циклических буферов;

5) организация

циклов

с

автоматической

проверкой

условия

их

завершения.

Семейство процессоров ADSP-21xx представляет собой совокупность

16-разрядных программируемых микропроцессоров с общей структурой,

оптимизированную для обработки аналогового сигнала в цифровой форме, а

также для других прикладных целей. Различные микропроцессоры отличаются

друг от друга преимущественно типом периферийных устройств, которые

дополняют основную структуру. Различные члены семейства могут иметь

память, таймер, последовательный и параллельный порты.

В настоящее время серийно выпускаются сигнальные процессоры,

относящиеся к третьему поколению семейства, − ADSP-218x. Процессоры

второго

поколения

(ADSP-2101/2104/2105/2111/2115)

с

максимальной

производительностью 25 MIPS (миллионов инструкций в секунду) также

продолжают серийно выпускаться. Но их применение в новых изделиях

становится экономически невыгодным, так как они значительно проигрывают

третьему

поколению

как

в

объеме

внутренних

ресурсов,

так

и

в

производительности. Сохраняя программную совместимость с процессорами

ADSP-2101/2104/2105/2115, процессоры семейства ADSP-218x имеют полную

программную и частичную аппаратную совместимость между собой. Все они

используют гарвардскую архитектуру с разделением как внутренней памяти,

так и шин доступа к внутренней памяти программ и данных.

Необходимо отметить одну черту, отличающую процессоры ADSP-2181/2183

от остальных. Исторически эти процессоры были базовыми моделями, на основе

которых создано все семейство. Они отличаются от остальных большим

количеством выводов и менее компактным корпусом. Это обусловлено тем

фактом, что у данных процессоров оба интерфейса прямого доступа к

4

ГЕНЕРАТОР

АДРЕСОВ

ДАННЫХ #1

РЕГИСТР

КОМАНД

ГЕНЕРАТОР

АДРЕСОВ

ДАННЫХ #2

СЧЕТЧИК

КОМАНД

ПАМЯТЬ

ПРОГРАММ

SRAM

(ROM)

ГЕНЕРАТОР

АДРЕСА

ЗАГРУЗКИ

SRAM

24

PMA

14

ФЛАГИ

(только для

ADSP-2111)

ПАМЯТЬ

ДАННЫХ

ТАЙМЕР

16

Шина PMA

MUX

24

16

24

ВНЕШНЯЯ

ШИНА

АДРЕСА

14

ВНЕШНЯЯ

ШИНА

ДАННЫХ

Шина DMA

DMA

14

3

PMD

Шина PMD

устройство

обмена между

шинами

DMD

ВХОДНЫЕ

РЕГИСТРЫ

ВХОДНЫЕ

РЕГИСТРЫ

входные регистры

ALU

MAC

SHIFTER

ВЫХОДНЫЕ

РЕГИСТРЫ

ВЫХОДНЫЕ

РЕГИСТРЫ

выходные

регистры

16

MUX

Шина DMD

схема

паковки

распаковки

передающий регистр

передающий регистр

принимающий регистр

принимающий регистр

SPORT 0

(нет в ADSP 2105)

SPORT 1

Шина R

5

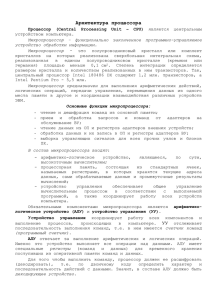

Рис. 1. Базовая архитектура семейства ADSP-21xx

5

5

памяти выведены непосредственно наружу и могут быть задействованы

одновременно, в то время как у остальных выводы интерфейсов прямого

доступа мультиплексированы, и выбор того или иного типа интерфейса (IDMA

или BDMA) происходит при включении питания или при общем аппаратном

сбросе процессора. Таким образом, модели ADSP-2181/2183 аппаратно

совместимы между собой, но несовместимы с остальными процессорами

семейства. Программная совместимость при этом обеспечивается полностью.

Архитектура ADSP-2181 приведена на рис. 1.

2.2.Вычислительные модули

Процессор

семейства

ADSP-21xx

содержит

три

независимых

вычислительных модуля:

арифметико-логический модуль(ALU);

модуль умножения с накоплением (MAC);

устройство сдвига (shifter).

Эти устройства работают с 16-разрядными данными и обеспечивают

аппаратную поддержку мультиточности.

Арифметико-логическое устройство (АЛУ) обеспечивает выполнение

стандартного набора арифметических и логических операций. К первым относятся

сложение, вычитание, инвертирование (отрицание), инкремент, декремент и

нахождение абсолютного значения. Эти операции дополнены двумя примитивами

деления, при помощи которых операция деления может выполняться за несколько

циклов. К логическим операциям относятся логическое И (AND), ИЛИ (OR),

исключающее ИЛИ (XOR) и НЕ (NOT). АЛУ (рис. 2) разрядностью 16 бит имеет

два 16-битовых порта ввода − Х и Y и один порт вывода R. АЛУ принимает

сигнал переноса (CI), который является битом переноса из арифметического

регистра состояния (ASTAT). В АЛУ генерируется 6 сигналов состояния:

нулевой результат (AZ), отрицания (AN), переноса (АС), переполнения (AV),

ввода знака через порт X (AS) и состояние частного (AQ). Все сигналы

арифметического

состояния

фиксируются

состояний (ASTAT) в конце цикла.

6

в

арифметическом

регистре

Шина PMD

24

Шина DMD

16

16 (старшие)

Мультиплексор

Регистры

АХ

2 Х 16

Регистры

AY

2 X 16

16

16

Мультиплексор

Мультиплексор

X

AZ

AN

AC

AV

AS

AQ

Y

АЛУ

CI

Регистры

АF

R

16

16

Мультиплексор

Регистры

АR

16

R-шина

Рис. 2. Структура АЛУ

Порт ввода X АЛУ может принимать данные из двух источников:

регистров АХ или шины результатов (R-шина). R-шина соединяет регистры вывода

всех вычислительных устройств, позволяя использовать их как операнды ввода.

Имеется два регистра АХ: АХ0 и АХ1. Считывание из этих регистров и запись в

них может производиться с шины данных памяти данных DMD. В наборе команд

предусматривается также считывание этих регистров на шину данных памяти

программ PMD, но в данном случае нет прямого соединения. В этой операции

используется устройство обмена данными между шинами PMD и DMD.

Два выхода регистров АХ позволяют осуществлять ввод с одного регистра в

АЛУ, в то время как другой передает данные на шину DMD. Порт ввода Y АЛУ

также может принимать данные из двух источников: регистров AY и регистра

обратной связи AF АЛУ. Имеется два регистра AY: AY0 и AY1. Считывание из

этих регистров и запись в них производится с шины DMD, запись может также

7

производиться из шины PMD. В наборе команд предусматривается считывание

из этих регистров на шину PMD, но в данном случае нет прямого соединения; в

этой операции используется устройство обмена данными между шинами PMD и

DMD. Два выхода регистров AY могут обеспечить ввод данных в АЛУ

одновременно с передачей данных на шину DMD.

Выходные данные АЛУ загружаются либо в регистр обратной связи АЛУ

(AF), либо в регистр результатов АЛУ (AR). Регистр AF является внутренним

регистром АЛУ и позволяет использовать результат АЛУ прямо в качестве

входного значения для порта Y АЛУ. Регистр AR может передавать данные как

на шину DMD, так и на шину результатов. Этот регистр может прямо

загружаться с шины DMD. В наборе команд предусматривается также считывание

с AR на шину PMD, но в данном случае нет прямого соединения. Для этой

операции используется устройство обмена данными между шинами PMD и DMD.

В любой из регистров, связанных с АЛУ, может производиться запись и

считывание в течение одного и того же цикла. Считывание с регистров

производится в начале цикла, а запись в регистры − в конце цикла.

Следовательно,

при

считывании

из

регистра

считывается

значение,

загруженное в этот регистр в конце предшествовавшего цикла. Новое значение,

записанное в регистр, не может быть считано до начала последующего цикла.

Это позволяет регистрам ввода АЛУ обеспечивать АЛУ операндом в начале цикла

и обновляться следующим операндом из памяти в конце того же цикла, а также

позволяет сохранять содержимое регистра результатов в памяти и обновлять этот

регистр новым значением результата в течение одного и того же цикла.

В АЛУ содержится двойной ряд регистров (рис. 2) за основными

регистрами. В действительности имеется два набора регистров (AR), (AF), (АХ)

и (AY). В любой определенный момент времени доступным является только

один ряд регистров. Дополнительный ряд регистров может быть активизирован

для чрезвычайно быстрого контекстного переключения (например, во время

подпрограммы обслуживания прерывания). В таком случае новая задача (т.е.

8

обслуживание прерывания в примере) может быть выполнена без передачи

текущих состояний в запоминающее устройство.

Выбор основного или альтернативного ряда регистров управляется битом в

регистре состояния режима процессора (MSTAT). Если этот бит принимает значение

0, выбирается основной ряд; если он равен 1, выбирается теневой ряд регистров.

Умножитель-накопитель выполняет одноцикловые операции умножения,

умножения/сложения, умножения/вычитания. Сумматор разрядностью в 40 бит

обеспечивает 8 бит защиты от переполнения при последовательном сложении и

тем самым гарантирует, что не произойдет ни потери данных, ни их диапазона:

чтобы произошла потеря старшего разряда, требуется 256 переполнений.

Имеются специальные команды для выполнения масштабирования данных с

блочной плавающей точкой.

Устройство сдвига осуществляет логические и арифметические сдвиги,

нормализацию, денормализацию и операцию получения порядка, а также

управление форматом данных, разрешая работу с плавающей точкой.

Вычислительные модули размещаются последовательно друг за другом

таким образом, чтобы выход одного мог стать входом другого в следующем

цикле. Результаты работы модулей собираются на 16-разрядную шину R.

Все три модуля содержат входные и выходные регистры, которые доступны

через 16-разрядную шину DMD. Команды, выполняемые в модулях, берут в

качестве операндов данные, находящиеся в регистрах ввода, и после

выполнения записывают результат в регистры вывода. Эти регистры являются

промежуточным хранилищем между памятью и вычислительной схемой.

R-шина позволяет результату одного вычисления стать операндом для другой

операции. Это позволяет сэкономить время, обходясь без лишних пересылок из

вычислительного модуля в память и обратно.

2.3.Генераторы адресов данных. Программный автомат

Два специализированных генератора адресов данных (DAG) и мощная

программа

«sequencer»

гарантируют

эффективное

использование

вычислительных модулей. Генераторы обеспечивают адреса памяти, когда

9

необходимо поместить данные из памяти в регистры ввода вычислительных

модулей либо сохранить результат из выходных регистров. Каждый генератор

отвечает за четыре указателя адреса. Если указатель используется для

косвенной адресации, то изменится значение некоторого регистра. С двумя

генераторами процессор может выдавать два адреса одновременно для выборки

из памяти двух операндов.

Генератор адресов данных #1 обеспечивает адреса только для данных,

генератор адресов #2 – для данных и программ. Когда в регистре состояния

(MSTAT) установлен соответствующий бит режима, адрес вывода генератора

#1, прежде чем попасть на шину адреса, инвертируется. Эта особенность

облегчает работу в двоичной системе.

Программа «sequencer» обеспечивает последовательность команд и

адресацию памяти программы. «Sequencer» управляется регистром команд,

указывающим на команду, которая в данный момент выполняется. Выбранные

команды записываются в регистр команд за один такт процессора и

выполняются в течение следующего такта. Чтобы уменьшить количество

циклов, «sequencer» поддерживает работу с условными переходами.

Программный автомат состоит из счетчика, регистра команд и генератора

адреса загрузки команд. Осуществляет поддержку операций с условными

переходами, вызов подпрограмм и возврат в основную программу.

2.4.Оперативная память

Оперативная память разделена на память данных (16 килослов) и память

программ (16 килослов), однако система команд поддерживает использование

памяти программ также и для хранения данных (модифицированная

гарвардская архитектура). Разделение основных шин процессора на четыре

(шины данных памяти программ, данных памяти данных, адресов памяти и

адресов данных) позволяет распараллеливать процессы и одновременно

выполнять операции обработки.

10

2.5.Шины

Процессоры семейства имеют пять внутренних шин. Шины адреса

программы (PMA) и адреса данных (DMA) связаны с адресами памяти данных

и программы.

Шина данных памяти программ (PMD) и шина данных памяти данных

(DMD) используются для передачи информации, связанной с областями

памяти. Шины мультиплексированы в одну внешнюю шину адреса и одну

внешнюю шину данных.

R-шина

предназначена

для

передачи

промежуточных

результатов

непосредственно между вычислительными модулями.

Адресная шина (PMA) имеет разрядность 14 бит обеспечивает доступ к 16

килобайтам смешанной системы команд и данных. Шина (PMD) предназначена

для работы с 24-битными командами.

Адресная шина (DMA) разрядностью 14 бит обеспечивает прямой доступ к

16

килобайтам

области

данных.

Шестнадцатиразрядная

шина

(DMD)

предназначена для внутренних пересылок между любыми регистрами

процессора и регистров с памятью в одиночном цикле. Адрес памяти данных

исходит из двух источников: абсолютное значение, определенное в системе

команд (прямая адресация), или вывод данных адресует генератор (косвенная

адресация). Воспользоваться данными, расположенными в памяти программ,

можно лишь с помощью косвенной адресации.

Шина данных памяти программы (PMD) предназначена для передачи

данных в вычислительные модули и считывания результата вычислений через

модуль обмена между шинами (PMD) и (DMD). Этот модуль позволяет

передавать данные от одной шины к другой. Он имеет аппаратные средства для

преодоления разницы в 8 бит между разрядностью этих двух шин.

2.6.Внутренние периферийные устройства

Этот раздел описывает дополнительные функциональные модули, которые

включены в различные процессоры семейства ADSP-21xx.

11

Последовательные порты

Большинство

процессоров

семейства

ADSP-2100

имеют

по

два

последовательных двунаправленных порта. Порты являются синхронными и

используют кадровые сигналы для контроля приема-передачи данных. Каждый

порт имеет внутренний генератор частоты, но в то же время может

использовать

внешний

генератор.

Сигналы

синхронизации

могут

вырабатываться как самим портом, так и внешним устройством. Длина кадра

обмена может меняться от 3 до 6 бит. Последовательный порт SPRT0 имеет

многоканальные возможности и позволяет обмен данными произвольной

длины от 24 до 32 байт. Второй порт SPORT1 может быть сконфигурирован с

помощью внешних прерываний IRQ0 и IRQ1.

Таймер

Программируемый таймер может генерировать периодические прерывания

с интервалом, кратным циклам процессора. После инициализации содержимое

16-разрядного регистра счетчика TCOUNT декрементируется через каждые n

циклов, причем n – 1 является коэффициентом масштабирования, значение

которого хранится в 8-разрядном регистре TSCALE. Когда значение в регистре

счетчика становится равным нулю, генерируется прерывание, а затем в регистр

счетчика снова загружается значением из 16-разрядного регистра периода

TPERIOD. Наличие у таймера коэффициента масштабирования позволяет

16-разрядному счетчику генерировать прерывания в широком диапазоне

возможных периодов. При времени цикла процессора, равном 80 нс, таймер

может генерировать прерывания с периодами от 80 нс до 5,24 мс. При

использовании масштабирования временной период может достигать 1,34 с.

Прерывания таймера могут при необходимости маскироваться, сбрасываться и

принудительно устанавливаться при помощи программных средств.

Главный интерфейсный порт (HIP)

Главный интерфейсный порт – параллельный порт ввода-вывода осуществляет

прямое соединение с процессором. Через него производится обмен между ADSP21xx и памятью главной ЭВМ. HIP состоит из регистров, через которые ADSP-21xx

12

и главный процессор обмениваются информацией о своем состоянии и данными.

HIP может быть сконфигурирован следующим образом:

8-разрядная или 16-разрядная шина;

мультиплексная шина данных/шина адреса или отдельно шина

данных и шина адреса;

чтение стробирующих сигналов READ/WRITE.

Порты прямого доступа к памяти (ADSP-2181)

ADSP-2181 имеет два DMA порта прямого доступа к памяти. Порт

прямого доступа к внутренней памяти (IDMA) и порт прямого побайтового

доступа к памяти (BDMA).

IDMA порт представляет собой параллельный порт ввода/вывода, который

позволяет хост-машине осуществлять запись/считывание внутренней памяти

процессора. IDMA порт имеет 16-разрядную мультиплексированную шину

адреса и данных, с помощью которых можно осуществлять доступ как к

16-разрядной памяти данных, так и 24-разрядной памяти программ. IDMA порт

полностью асинхронный относительно работы процессора. Таким образом,

хост-машина может обратиться к внутренней памяти сигнального процессора,

не влияя на быстродействие ADSP-2181.

Порт BDMA позволяет загружать и хранить команды программ и данные,

из (в) памяти с байтовой организацией с минимальными непроизводительными

потерями. Пока процессор выполняет команды программы, порт BDMA

осуществляет считывание или запись кода команд или данных из памяти (в

память) с байтовой организацией, с потерей одного цикла процессора за

переданное слово в случаях считывания из (записи во) внутренней памяти.

Аналоговый интерфейс

Входной аналоговый интерфейс состоит из входных усилителей и

16-разрядного аналого-цифрового преобразователя (ADC). Аналогично на

выходе

находится

цифроаналоговый

дифференциальный усилитель.

13

преобразователь

и

выходной

2.7.Программно-логическая модель

Для программирования процессора следует представлять его программнологическую модель. Ядро процессоров семейства ADSP-21xx, с точки зрения

программиста, состоит из трех вычислительных устройств, двух генераторов

адреса и программного автомата (рис. 3). На рисунке возле регистров указана

их разрядность. Обращение к регистрам этих устройств из программы

производится по их логическим именам.

У каждого из регистров вычислителя есть теневой регистр-двойник.

Переключение между основными и теневыми регистрами производится

программно с помощью команд ENA SEG_REG (выбрать вторичный набор

регистров, т.е. установить в 1 соответствующий бит в регистре статуса MSTAT)

и DIS SEG_REG (сбросить этот бит).

Регистры ASTAT, SSTAT, MSTAT содержат информацию о состоянии

процессора. Регистр ASTAT содержит флаги арифметических условий.

Значения этих флагов приведены в табл. 1.

Таблица 1

Флаги регистра ASTAT

Номер бита

0

1

2

3

4

5

6

7

Флаг

AZ

AN

AV

AC

AS

AQ

MV

SS

Назначение

Нулевой результат АЛУ

Отрицательный результат АЛУ

Переполнение АЛУ

Перенос АЛУ

Знак входа Х АЛУ

Признак частного от деления

Переполнение умножителя

Знак сдвига данных

Таблица 2

Назначение битов регистра SSTAT

Номер бита

0

1

2

3

4

5

6

7

Назначение

Стек счетчика команд пуст

Стек счетчика команд переполнен

Стек счетчика пуст

Стек счетчика переполнен

Стек состояний пуст

Стек состояний переполнен

Стек циклов пуст

Стек циклов переполнен

14

Рис. 3. Регистры процессоров ADSP-218x, доступные для программирования

Регистр SSTAT служит для хранения состояний 4 внутренних стеков

программного автомата (табл. 2).

Регистр MSTAT (табл. 3) содержит информацию о модификации режима

работы процессора.

Таблица 3

Назначение битов регистра MSTAT

Номер бита

0

1

2

3

4

Назначение

Выбор ряда регистров данных: 0 – главный, 1 − теневой

Разрешение бит-реверсной адресации (генератор адреса данных 1)

Разрешение режима фиксации состояния переполнения в АЛУ

Разрешение режима насыщения регистра AR

Представление результата умножителя: 0 – режим умножения дробных

чисел, 1 – режим умножения целых чисел

15

Окончание табл. 3

Номер бита

5

Разблокирование таймера

6

Разрешение режима GO

Назначение

Для выбора конфигурации прерываний в процессоре задействованы

регистры IMASK, ICNTL, IFC. Регистр IMASK (табл. 4) предназначен для

маскирования или разрешения каждого отдельного вида прерывания процессора.

Таблица 4

Назначение битов регистра IMASK

Номер бита

0

1

2

3

4

5

6

7

8

9

Назначение

Разрешение прерываний от таймера: 1 − разрешено, 0 − запрещено

Прием SPORT1 или IRQ0

Передача SPORT1 или IRQ1

Прерывание BDMA

IRQE

Прием SPORT0

Передача SPORT0

IRQL0

IRQL1

IRQ2

Регистр ICNTL (табл. 5) конфигурирует внешние прерывания по фронту

либо по уровню сигнала. Кроме того, определяется возможность использования

вложенных прерываний.

Таблица 5

Назначение битов регистра ICNTL

Номер бита

0

1

2

4

Назначение

Прерывания IRQ0: 1 – по фронту, 0 – по уровню

Прерывания IRQ1: 1 – по фронту, 0 – по уровню

Прерывания IRQ2: 1 – по фронту, 0 – по уровню

Вложенные прерывания: 1 − разрешены, 0 − запрещены

Регистр IFC (табл. 6) осуществляет принудительное прерывание или сброс

задержанного чувствительного по фронту прерывания. В этот регистр может

осуществляться только запись числа.

Таблица 6

Назначение битов регистра IFC

Номер бита

Назначение

0

Сброс прерываний от таймера

1

Сброс прерываний прием SPORT1 или IRQ0

2

Сброс прерываний передача SPORT1 или IRQ1

16

Окончание табл. 6

Номер бита

3

4

5

6

7

8

9

10

11

12

13

14

15

Назначение

Сброс прерываний BDMA

Сброс прерываний IRQE

Сброс прерываний прием SPORT0

Сброс прерываний передача SPORT0

Сброс прерываний IRQ2

Принудительная установка прерываний от таймера

Принудительная установка прерываний прием SPORT1 или IRQ0

Принудительная установка прерываний передача SPORT1 или IRQ1

Принудительная установка прерываний BDMA

Принудительная установка прерываний IRQE

Принудительная установка прерываний прием SPORT0

Принудительная установка прерываний передача SPORT0

Принудительная установка прерываний IRQ2

Самостоятельный 8-разрядный регистр РХ служит для буферизации

данных при обмене между 16-разрядными регистрами процессора и 24-разрядной шиной данных памяти программ.

Кроме указаний регистров, некоторые процессоры семейства ADSP-21хх

содержат регистры управления внутреннего таймера и интерфейсные регистры

для организации ввода/вывода данных.

3. СИСТЕМА КОМАНД

Язык ассемблера состоит из набора команд-инструкций, в которых можно

использовать простые операторные выражения, и директив, используемых на

этапе

трансляции-ассемблирования.

Команды

процессоров

семейства

сгруппированы в следующие категории:

вычислительные команды АЛУ, умножителя и устройства сдвига;

команды пересылки данных;

команды управления последовательностью выполнения программы;

многофункциональные команды;

остальные.

Процессоры семейства ADSP-21xx могут выполнять за один цикл

операции выборки данных и умножения с накоплением.

17

Базовый

набор

команд

ADSP-21xx

включает

традиционные

для

микропроцессоров операции с блоками вычислителя, команды пересылки

данных и инструкции управления.

3.1.Команды АЛУ

В рассматриваемых сигнальных процессорах ADSP-21хх АЛУ имеет два

входа Х и Y. В дальнейшем соответствующие операнды будут обозначены как

Х-операнд и Y-операнд, а приемник результата – R.

Список стандартных функций АЛУ:

R=X+Y

− сложить операнды Х и Y;

R = X + Y +CI

− сложить операнды Х и Y и бит переноса;

R=X-Y

− вычесть операнд Y из X;

R = X - Y + CI – 1 − вычесть операнд Y из X с «заёмом» (единицы

старшего разряда при вычитании);

R=Y-X

− вычесть X из операнда Y;

R = Y - X +CI – 1 − вычесть X из операнда Y с «заёмом»;

R=-X

− инвертирование операнда X (в дополнительном коде);

R=-Y

− инвертирование операнда Y (в дополнительном коде);

R = Y+ 1

− инкрементирование операнда Y;

R=Y-1

− декрементирование операнда Y;

R = PASS X

− пропустить операнд X для сохранения результата

неизменным;

R = PASS Y

− пропустить операнд Y для сохранения результата

неизменным;

R = 0 (PASS 0)

− обнуление результата;

R = ABS X

− найти абсолютное значение операнда X;

R =X AND Y

− логическое И над операндами Х и Y;

R = X OR Y

− операция логического ИЛИ над операндами Х и Y;

R = X XOR Y

− операция исключающего ИЛИ над операндами Х и Y;

R = NOT X

− операция

логического

(в дополнительном коде);

18

НЕ

над операндом X

R = NOT Y

− операция

логического

НЕ

над

операндом Y

(в дополнительном коде).

Источники ввода данных в порты X, Y и направление вывода данных

через порт R для АЛУ приведены в табл. 7.

Таблица 7

Источники ввода/вывода данных АЛУ

Источники ввода данных

в порт X

АХ0, АХ1

AR

MR0, MR1, MR2

SR0, SR1

Источники ввода данных в

порт Y

AY0, AY1

AF

Направление вывода

данных через порт R

AR

AF

Для каждой команды возможно выполнение её по условию в следующем

виде:

IF [условие] R = Х + Y;

IF [условие] является необязательным элементом команды и может

использовать следующие флаги:

EQ − результат АЛУ

= 0;

NE − результат АЛУ

≠ 0;

GT − результат АЛУ

> 0;

GE − результат АЛУ

≥ 0;

LT − результат АЛУ

< 0;

LE − результат АЛУ

≤ 0.

[Not] AV − (нет) переполнение АЛУ;

[Not] АС − (нет) перенос в АЛУ;

[Not] MV − (нет) переполнение умножителя;

[Not] CE − цикл не завершен;

NEG − отрицательный знак на входе Х АЛУ;

POS − положительный знак на входе Х АЛУ.

Кроме указанных команд, для реализации операции деления используются

команды:

19

DIVS YОР, ХОР;

DIVQ ХОР.

Примеры команд АЛУ:

AR

= AX0 + AY0;

AF = MR1 XOR AY1;

AR = AX0 - AF;

IF GE AR = - AR;

IF AV AR = АY1 + 1;

3.2.Команды умножителя-накопителя

R=X*Y(формат)

− умножение операндов Х и Y.

R=MR + X*Y(формат)

− умножение операндов Х и Y и сложение

результата с содержимым регистра MR.

R=MR - X*Y(формат)

− умножение операндов Х и Y и вычитание

полученного результата из содержимого регистра MR.

R=0

− обнуление результата регистра MR.

R=MR[(RND)]

− округление результата.

Источники ввода данных и направление вывода данных умножителя

приведены в табл. 8.

Таблица 8

Источники ввода/вывода данных умножителя-накопителя

Источники ввода

данных в порт X

МХ0, МХ1

AR

MR0, MR1, MR2

SR0, SR1

Источники ввода

данных в порт Y

MY0, MY1

MF

Направление вывода

данных через порт R

MR(MR2, MR1, MR0)

MF

Форматы операндов при умножении:

SS − 2 знаковых операнда;

SU, US − 1 знаковый операнд;

UU – 2 беззнаковых операнда;

RND – округление результата.

Для каждой команды возможно выполнение её по условию в следующем виде:

20

IF [условие] R = Х * Y.

IF [условие] − является необязательным элементом команды.

Примеры команд умножителя накопителя:

MR = MX1 * МY0 (SS);

MF = AR * МY1 (SU);

MR = MR + AR * MY (SS);

MR = 0;

IF EQ MR = MX0 * МY0 (UU);

По умолчанию установлен режим умножителя дробных чисел. Установка

режима умножения целых чисел осуществляется командой:

ENA M_MODE; − установка;

DIS M_MODE; − сброс.

Переполнение умножителя (в регистре ASTAT флаг MV = 1) происходит

при изменении знакового бита во время накопления.

3.3.Команды устройства сдвига

Команды, содержащие величину сдвига:

SR = [SR OR] ASHIFT хор <данные> (выравнивание);

SR = [SR OR] LSHIFT хор <данные> (выравнивание);

Команды, для которых сдвиг задан в регистре SE:

[IF условие] SR = [SR OR] ASHIFT хор (выравнивание);

[IF условие] SR = [SR OR] LSHIFT хор (выравнивание);

где IF условие − арифметическое условие,

хор = [SR0, SR1, MR2, MR1, SI, MR0, AR],

выравнивание − [HI, LO] − по старшему или по младшему слову SR,

данные − -32...32 − величина сдвига (влево - вправо).

Арифметический сдвиг (ASHIFT) отличается от логического (LSHIFT) тем,

что при сдвиге вправо происходит расширение знака вместо записи нулей.

Рассмотренные выше команды АЛУ, умножителя и устройства сдвига

составляют самую многочисленную группу команд − команды вычислений.

21

Ниже будут рассмотрены другие группы команд сигнальных процессоров

ADSP-21xx.

3.4.Команды пересылки данных

В группе команд пересылки данных можно выделить следующие

разновидности:

Рг ←→ Рг (регистр-регистр);

Рг ←→ ПД (прямая/косвенная адресация);

Рг ←→ ПП (только косвенная адресация);

непосредственное значение

→ Рг;

непосредственное значение

→ ПД (только косвенная адресация).

Выделим отдельно команды работы с памятью данных (ПД) и памятью

программ (ПП):

команды для ПД

dreg = DM (ix, mx);

DM (ix, mx) = dreg;

DM (ix, mx) = <данные>;

DM(<адрес>) = dreg;

dreg = DM(<адрес>);

команды для ПП

dreg = РM (iрx, mрx);

РM (iрx, mрx) = dreg;

где ix = [I0, I1, I2, I3],

mx = [M0, M1, M2, M3] − при использовании генератора адреса #1,

или ix = [I4, I5, I6, I7],

mx = [M4, M5, M6, M7] − при использовании генератора адреса #2,

dreg = [АХ0, АХ1, АY0, АY1, МХ0, МХ1, МY0, МY1,AR, MR0, MR1,

MR2, SI, SE, SR0, SR1]

ipx = [I4, I5, I6, I7]

mpx = [М4, М5, М6, М7].

Примеры команд пересылки данных:

22

МХ0 = АY1;

АХ0 = DМ(0x3800);

АY0 = РМ(I4, М6);

SI = DM(0x2000);

DM(I3, M3) = 123;

3.5.Команды передачи управления в программе

Команды

этой

группы,

имеющие

общепринятые

мнемонические

обозначения, приведены ниже:

команда [условного] перехода

[IF условие] JUMP <dest>;

вызов подпрограммы

[IF условие] CALL <dest>;

возврат из подпрограммы

[IF условие] RTS;

прерывание

[IF условие] RTI;

переход по флагу

[IF <флаг-условие>] JUMP <адрес>;

вызов подпрограммы по флагу

[IF <флаг-условие>] СALL <адрес>;

где IF условие − арифметическое условие;

<dest> = [(I4), (I5), (I6), (I7), <адрес>];

флаг-условие − [Not] FLAG_IN − может устанавливаться и сбрасываться с

помощью специальных команд SET и RESET.

Кроме указанных команд, имеется команда организации циклов.

DO метка UNTIL условие;

{тело цикла}

метка: последняя команда,

где условие − арифметическое условие обнуления СЕ счетчика цикла CNTR.

метка − символический адрес последней команды цикла.

Используемые в командах управления последовательностью выполнения

программ коды условий приведены в табл. 9.

23

Таблица 9

Коды условий

Синтаксис

EQ

NE

LT

GE

LE

GT

AC

NOT AC

AV

NOT AV

MV

NOT MV

NEG

POS

NOT CE

FLAG_IN*

NOT

FLAG_IN*

Условие состояния

Равно нулю

Не равно нулю

Меньше нуля

Больше или равно нулю

Меньше или равно нулю

Больше нуля

Перенос в АЛУ

Нет переноса в АЛУ

Переполнение в АЛУ

Нет переполнения в АЛУ

Переполнение в умножителе-накопителе

Нет переполнения в умножителенакопителе

Операнд Х последней команды АВS был

отрицательным

Операнд Х последней команды АВS был

положительным

Счетчик не пуст

Значение на выводе FI

Значение на выводе FI

Истинно, если

AZ=1

AZ=0

AN.XOR.AV=1

AN.XOR.AV=0

(AN.XOR.AV).OR.AZ=1

(AN.XOR.AV).OR.AZ=0

AC=1

AC=0

AV=1

AV=0

MV=1

MV=0

AS=1

AS=0

−

Последнее значение на

выводе FI=1

Последнее значение на

выводе FI=0

* Только в командах JUMP и CALL.

3.6.Многофункциональные команды

Имеется возможность объединять в одной команде две или три операции,

соответствующие простым командам, рассмотренным ранее. Существует две

основные структуры многофункциональных команд.

Структура 1

Вычислительная операция

Считывание данных

ПД → Рг АЛУ, УМН

и

ПП → Рг,

где ПД – память данных, Рг – регистры, ПП – память программ, УМН –

умножитель.

При

использовании

данной

структуры

ограничения:

недопустима операция деления в АЛУ;

24

существуют

следующие

обращение к ПД только через генератор адреса #1, а к ПП − через

генератор адреса #2;

считывание из ПД только в МХ, АХ, а из ПП − в МY, АY;

результат вычисления записывается только в AR и MR.

Структура 2

Вычислительная операция

Считывание данных

АЛУ, УМН, УСД

Рг ←→ Рг

или Рг ←→ ПД

или Рг ←→ ПП,

где УСД – устройство сдвига.

Примеры многофункциональных команд:

AR = AX0 - АY1, АХ1 = DM(I1, M3);

MR = MR + MR0 * МY1(SS), АХ1 = MR0;

SR = SR OR LSHIFT MR2(HI), MX1 = PM(I6, M6);

При использовании второй структуры существуют следующие ограничения:

недопустимы операции деления в АЛУ и непосредственный сдвиг (SE) в

устройстве сдвига;

допускается использовать только вычислительные регистры (АХ, АY и

другие);

обращение к ПД только через генератор адреса #1, к ПП − через

генератор адреса #2.

3.7.Другие команды

Из других часто используемых команд можно отметить следующие:

пустая команда (нет операции)

NOP;

команды установки, сброса и переключения флага-условия

[IF условие]

SET

RESET

TOGGLE

FLAG.OUT

25

загрузка и извлечение данных из стеков

PUSH

STS или CNTR, PC, LOOP

POP

установка и сброс специальных режимов

ENA

BIT_REV, M_MODE, TIMER

DIS

модификация индексно-адресных регистров без обращения к памяти

MODIFY (

I0, I1, I2, I3

,

I4, I5, I6, I7

M0, M1, M2, M3

)

M4, M5, M6, M7

Директивы

В программе на ассемблере вместе с командами содержатся директивы,

используемые на этапе трансляции программы в машинный код, но сами они не

транслируются. В программном коде директивы помечаются точками.

Пример:

.VAR/DM my_array[128]

Директива, объявляющая, что в памяти данных формируется массив из 128

шестнадцатибитовых элементов, с началом по адресу my_array.

.INIT my_array: <filename.dat>

Директива считывает значение из файла данных filename.dat в массив во

время сборки программы (работает только в режиме эмуляции).

.include «def2181.h»

Подключает файл def2181.h, расположенный в той же директории, что и

программа, в котором как константы определены имена регистров и их

отдельных бит, а также имена адресов векторов прерывания.

4. ФОРМАТЫ ПРЕДСТАВЛЕНИЯ ЧИСЕЛ

Беззнаковые двоичные числа можно представить как положительные

значения с абсолютной величиной, почти в два раза превышающей абсолютное

26

значение знакового числа той же длины. Самые младшие слова чисел с

многократной точностью также представляются в беззнаковом формате.

Процессоры семейства ADSP-21xx поддерживают знаковые числа,

представленные в формате с дополнительным кодом. Двоично-десятичный

формат, формат с избыточными битами и величины со знаком не

поддерживаются этими процессорами.

Целые числа представляются в прямом коде (рис. 4). Каждому биту

соответствует определенная степень двойки, и в сумме они дают необходимое число.

2 15 2 14 2 13 2 12 2 11 2 10 2 9 2 8 2 7 2 6 2 5 2 4 2 3 2 2 2 1 2 0

Рис. 4. Представление целых беззнаковых чисел

В процессоре ADSP-2181, как во многих других, память данных разделена

на шестнадцатиразрядные слова. Для увеличения количества представляемых

чисел

необходимо

увеличить

количество

используемых

разрядов,

т.е.

использовать несколько слов.

В знаковых числах, для представления знака отводится один бит, поэтому

диапазон представления целых чисел со знаком от –215 − 1 = −32767 до 215 − 1 =

= 32767. В качестве знакового выбирается старший бит, что дает возможность

представлять положительные числа в прямом коде как числа без знака в

меньшем диапазоне. Для представления чисел со знаком можно использовать

три системы представления. Каждая из них получается путем модификации

модуля числа, представленного в прямом коде.

Прямой код – в старший бит помещается 1, остальные биты остаются

прежними (рис. 5).

0 0 0 0 1 1 0 1 1 0 0 0 1 1 0 0

3468(10)

1 0 0 0 1 1 0 1 1 0 0 0 1 1 0 0

-3468(10)

Рис. 5. Знаковые числа в прямом коде

Обратный код – все биты инвертируются (рис. 6).

27

0 0 0 0 1 1 0 1 1 0 0 0 1 1 0 0

3468(10)

1 1 1 1 0 0 1 0 0 1 1 1 0 0 1 1

-3468(10)

Рис. 6. Знаковые числа в обратном коде

Дополнительный код – все биты инвертируются, а к младшему разряду

прибавляется 1 (рис. 7).

0 0 0 0 1 1 0 1 1 0 0 0 1 1 0 0

3468(10)

1 1 1 1 0 0 1 0 0 1 1 1 0 1 0 0

-3468(10)

Рис. 7. Знаковые числа в дополнительном коде

Прямой код неудобен для машинных расчетов, так как при сложении

двух чисел одинаковых по модулю, но с разным знаком, не получается ноль.

При сложении чисел в обратном коде получается ошибка на единицу в

младшем

разряде,

которую

необходимо

корректировать.

Числа

в

дополнительном коде складываются, следуя обычным правилам сложения

двоичных чисел, что уменьшает сложность арифметического устройства

процессора.

Поэтому

наиболее

широкое

применение

получил

дополнительный код.

В документации на процессор ADSP-2181 данный формат называется 16.0.

Это означает что 16 разрядов отведено под целую часть и ноль разрядов

отведено под дробную часть числа.

В дробном формате двоичная точка лежит внутри числа, поэтому

некоторые или все биты его абсолютного значения имеют вес меньше единицы.

На рис. 8 показан формат числа, двоичная точка которого расположена слева от

трех самых младших бит, и указан их вес. Такой формат имеет обозначение 13.3.

Все возможные форматы чисел разрядностью 16 бит, которые могут быть

представлены в дробных форматах, приведены в табл. 10.

28

Рис. 8. Дробный формат 13.3 беззнакового и знакового числа

Таблица 10

Дробные форматы и их диапазоны

Формат Число Число

целых дробных

бит

бит

Наибольшее

положительное

значение (0x7FFF) в

десятичной системе

1

2

3

4

Наименьшее

отрицательное

значение

(0x8000) в

десятичной

системе

5

1.15

1

15

0.999969482421875

-1.0

0.000030517578125

2.14

2

14

1.999938964843750

-2.0

0.000061035156250

3.13

3

13

3.999877929687500

-4.0

0.000122070312500

4.12

4

12

7.999755859375000

-8.0

0.000244140625000

5.11

5

11

15.999511718750000

-16.0

0.000488281250000

6.10

6

10

31.999023437500000

-32.0

0.000976562500000

7.9

7

9

63.998046875000000

-64.0

0.001953125000000

8.8

8

8

127.996093750000000

-128.0

0.003906250000000

9.7

9

7

255.992187500000000

-256.0

0.007812500000000

10.6

10

6

511.984375000000000

-512.0

0.015625000000000

11.5

11

5

1023.968750000000000

-1024.0

0.031250000000000

12.4

12

4

2047.937500000000000

-2048.0

0.062500000000000

13.3

13

3

4095.875000000000000

-4096.0

0.125000000000000

14.2

14

2

8191.750000000000000

-8192.0

0.250000000000000

15.1

15

1

16383.500000000000000

-16384.0

0.500000000000000

16.0

15

0

32767.000000000000000

-32768.0

1.000000000000000

29

Значение

наименьшего

значащего бита

(0x0001) в

десятичной системе

6

При выполнении сложения и вычитания оба операнда должны быть

представлены в одном и том же формате, который совпадает с форматом

результата. Сложение и вычитание знаковых и беззнаковых входных чисел

выполняется одинаковым образом.

При умножении входные значения могут иметь различные форматы, от

которых будет зависеть результат. Язык ассемблер процессоров семейства

ADSP-21xx позволяет описать, являются ли оба входных значения знаковыми,

беззнаковыми или и тем и другим. Расположение двоичной точки в результате

определяется из ее расположения в каждом из входных значений, что показано

на рис. 9. Произведением двух 16-разрядных чисел будет 32-разрядное число.

Произведение двух значений с форматами М.N и P.Q будет иметь формат

(M+P).(N+Q). Например, произведение двух чисел в формате 13.3 будет иметь

формат 26.6, а произведение двух чисел в формате 1.15 будет иметь формат 2.30.

Главное правило

Пример для 4 бит

M.N

P.Q

(M+P) . (N+Q)

×

Пример для 16 бит

1.111 формат 1.3

11.11 формат 2.2

1111

1111

1111

1111

111.00001 формат 3.5

×

×

5.3

5.3

10.6

1.15

× 1.15

2.30

Рис. 9. Формат результата умножения

Произведением двух чисел в формате с дополнительным кодом будет

число с двумя знаковыми битами. Так как один из этих битов является

избыточным, все биты результата можно сдвинуть на 1 бит влево. Кроме того,

если одно входное значение было в формате 1.15, то после сдвига влево формат

результата окажется равным формату другого входного значения (с 16 битами

дополнительной точности). Например, при умножении числа в формате 1.15 на

число в формате 5.11 получается число в формате 6.26. После сдвига влево на

1 бит результат имеет формат 5.27, т.е. представляет собой число в формате

5.11 плюс 16 самых младших бит.

30

Во

всех

процессорах

семейства,

кроме

процессора

ADSP-2100,

целочисленный и дробный режимы управляются битом в регистре MSTAT. При

перезапуске по умолчанию для совместимости с ADSP-2100 устанавливается

дробный режим.

Дробный режим характеризуется тем, что результат умножения всегда

подвергается сдвигу на 1 бит влево перед записью его в регистр результата.

Сдвиг влево позволяет удалить один лишний знаковый бит, когда оба операнда

были знаковыми числами, и получить в итоге результат в одном из

представленных выше форматах. Когда оба операнда имеют формат 1.15,

результат получается в формате 2.30. В дробной части 30 бит. После сдвига

влево формат результата становится равным 1.31 и может округляться до 1.15.

Таким образом, при использовании дробного формата наиболее удобно

работать с форматом 1.15.

В целочисленном режиме сдвига влево не происходит. Этот режим

используется, когда оба операнда являются целыми числами в формате 16.0.

Результат имеет формат 32.0 и также является целым числом.

5. ЗАПУСК СРЕДЫ РАЗРАБОТКИ ПРОГРАММ

При разработке программ удобно пользоваться интегрированной средой

разработки и отладки (Integrated Development and Debugging Environment −

IDDE). Для семейства ADSP соответствующий пакет программ носит название

VisualDSP++.

VisualDSP++

обеспечивает

расширенные

возможности

разработки программ для всех семейств DSP, производимых Analog Devices, в

том числе SHARC, TigerSHARC, ADSP-218x и ADSP219x. Включенный в

VisualDSP++ компилятор языка «C++» был разработан специально для

потребителей DSP и поддерживает предложенный стандарт языка для

встраиваемых устройств (Embedded C++), который определяет подмножество

полного языка C++ по стандарту ISO/IEC. Компилятор «С++», разработанный

компанией ADI, также поддерживает шаблоны и другие возможности полного

стандарта, которые позволяют разработчику сокращать сроки создания

программ для ускорения их выпуска на рынок. Кроме того, доступны

31

предопределенные классы, которые поддерживают расширения, связанные с

методами цифровой обработки сигналов, а также учитывают особенности

аппаратного обеспечения.

В VisualDSP++ входят текстовый редактор, транслятор, редактор

связей, отладчик-симулятор, программа загрузки и другие полезные

программы. VisualDSP++ запускается из стартового меню Windows подобно

остальным приложениям. Элементы панели инструментов среды разработки

приведены в табл. 11.

Таблица 11

Элементы панели инструментов среды разработки

Операции с файлами:

создать, открыть, сохранить, распечатать, загрузить

программу, перезагрузить новую программу

Редактирование кода программ:

вырезать, копировать, вставить, отменить, снова

восстановить, поиск, повторить поиск, заменить,

искать текст, перейти, показать исходный файл,

установить закладку, перейти к следующей, перейти

к предыдущей, снять все закладки

Операции с проектом:

добавить файл, удалить из проекта, открыть окно

опций, собрать из выбранных файлов, собрать проект

с учетом обновленных файлов, собрать заново,

остановить сборку, режим компоновки проекта

Отладка программы:

старт или продолжение, запуск сначала, остановка,

сброс процессора, назначение точки остановки,

удаление всех точек остановки, разрешить или

отменить данную точку, в пошаговом режиме с

входом в подпрограммы, без входа в подпрограмму,

выйти из подпрограммы, открыть окна просмотра

выражений, Locals, стека, дизассемблер

В процессе загрузки потребуется проверка, что к компьютеру подключена

плата EZLAB. Если нет, то выбрать режим симулятора.

Для инициализации по запросу следует нажать кнопку сброса «Reset» на

плате. После этого на экране появится типичное окно интерфейса программы.

В случае необходимости можно объявить новую сессию работы среды

разработки. Для этого в меню «Session» выбрать пункт «New Session».

32

В появившемся окне (рис. 10), в выпадающем списке с названием «Debug

Target» установить «ADSP-218x Family Simulator». В окне «Processor»

установить тип выбранного процессора: в данной сессии ADSP-2181.

Рис. 10. Окно создания новой сессии

5.1. Создание проекта

Для создания нового файла проекта нужно выбрать пункт «New» из меню

«Project» или, нажав правую кнопку мыши в окне «Project Window», выбрать

пункт «New Project» контекстного меню (рис. 11).

Рис. 11. Окно проекта

В появившемся окне ввести имя файла проекта и сохранить проект в выбранной

рабочей папке, нажав кнопку «Сохранить». При создании нескольких проектов

лучше сохранять их в разных папках во избежание путаницы. В открывшемся

окне установок проекта (рис. 12) проверить все выпадающие списки на

соответствие выбранному семейству процессора. В окне «Name» закладки

«Project» проверить название файла проекта, а в выпадающем списке «Settings

for configuration» название папки для отладочных файлов.

33

Открыв закладку «General», указать каталоги вывода «Output Directories»:

«Intermediate files» (размещение промежуточных файлов) и «Output files»

(размещение выходных файлов). По умолчанию каталогом вывода является

каталог «Debug», находящийся там же, где размещен проект.

Рис. 12. Окно опций проекта

Выбрав необходимые опции, нажать «OK». Опции, устанавливаемые нами

при создании проекта, можно будет изменить, воспользовавшись меню «Project

\ Project Options».

К созданному проекту необходимо добавить файл «ADSP-2181.ldf», путь к

которому «…\ VisualDSP \ 218x \ ldf \ ADSP-2181.ldf». Скопировать этот файл в

каталог проекта. Добавить скопированный файл в проект, используя меню «Project \

Add to Project \File(s)» или нажав на панели инструментов кнопку

. После

добавления этот файл появится в каталоге «Linker Files» окна «Project Window».

Файлы описания компоновщика (*.LDF файлы) описывают целевую

систему, карту кода программы и данных в пределах системной памяти и

34

внутри семейства процессоров. Каждый проект требует *.LDF файл. Этот файл

можно редактировать.

Если файл с текстом программы (тексты на языках С/С++ и ассемблер)

уже существует, то также добавляем его к проекту. Он будет размещен в

каталоге «Source Files» (исходные файлы). Если файла текста программы нет,

необходимо создать его.

5.2. Создание файлов кода программы

Для создания нового файла исходного кода программы в меню «File»

выбрать пункт «New» или нажать сочетание клавиш «Ctrl+N». В появившемся

окне с заголовком «Untitled Edit 1» набрать код программы генерирования

гармонического сигнала, приведенный ниже:

//**********************************************

// Программа формирования гармонического сигнала

// **********************************************

#define n 1024

// определяем n=1024

// объявление секции данных data1

// циклический буфер данных,

// хранящий информацию о значениях

//синуса, заполняется из файла sin1024.dat

// буфер данных, содержащий

// значение гармонической функции

// циклический буфер, содержащий

// значения несущей

// обозначение секции таблицы векторов

//прерывания

// 0x0000: Вектор сброса

// 0x0004: Вектор IRQ2

// 0x0008: Вектор IRQL1

// 0x000C: Вектор IRQL0

// 0x0010: Вектор SPORT0 transmit

// 0x0014: Вектор SPORT0 receive

// 0x0018: Вектор IRQE

// 0x001C: Вектор BDMA

// 0x0020: Вектор SPORT1 transmit

// 0x0024: Вектор SPORT1 receive

// 0x0028: Вектор Timer

// 0x002C: Вектор Power down

.section/data data1;

.VAR/circ

sin[n] = "sin1024.dat";

.var

harmony[1024];

.var/circ

mod[n];

.section/pm interrupts;

JUMP start; nop; nop; nop;

RTI; nop; nop; nop;

RTI; nop; nop; nop;

RTI; nop; nop; nop;

RTI; nop; nop; nop;

RTI; nop; nop; nop;

RTI; nop; nop; nop;

RTI; nop; nop; nop;

RTI; nop; nop; nop;

RTI; nop; nop; nop;

RTI; nop; nop; nop;

RTI; nop; nop; nop;

// обозначение секции кода программ

// вызов функции

// нет операции

.section/pm program;

start: call harm;

nop;

35

.global harm;

harm:

I0=sin;

L0=length(sin);

m0= 128;

I1=harmony;

L1=0;

m1=1;

cntr=1024;

do harm_loop until ce;

SR1=DM(I0,M0);

harm_loop:

DM(I1,M1)=SR1;

rts;

harm.end:

//объявление функции harm глобальной

// (формирование гармонич. сигнала)

//тело функции

//загрузка указателя с первым адресом sin

//синус-циклический массив

//частота несущей 1 кГц

//harmony-нециклический массив

//шаг счетчика

//счетчик

//запуск цикла, вызывается подпрограмма

//harm_loop до тех пор, пока не 0

//из SR1 считывается в память данных (с адресом I0),

// по завершении считывания обновляется значением

// из M0

//возврат из подпрограммы

//окончание функции, возврат из подпрограммы

После того как программа будет набрана, нужно сохранить файл с новым

заголовком. Для этого в меню «File» выбрать пункт «Save As…», в

появившемся окне, в строке «Имя файла», написать название файла и нажать

кнопку «Сохранить».

Открыть добавленный файл программы можно двойным щелчком левой

кнопки мыши на его заголовке в окне «Project Window». Теперь, когда файлы

описания компоновщика (*.LDF файл) и файл с текстом программы добавлены

к проекту, можно произвести построение проекта.

5.3. Компиляция и компоновка

Для построения проекта необходимо в меню «Project» выбрать пункт

«Build Project», либо нажать клавишу «F7», либо на панели инструментов

кнопку

. Если в программе содержатся ошибки, то они будут показаны в

окне «Output Window». Если построение прошло успешно, в окне «Output

Window» с открытой закладкой «Console» появится сообщение «Load complete»

(загрузка завершена, рис. 13).

36

Рис. 13. Окно вывода сообщений

После компиляции в рабочей папке проекта «Debug» появятся файлы

объектного кода с расширением (*.doj) и исполняемого кода (*.dxe).

5.4. Тестирование и отладка

Для запуска программы выбрать в меню «Debug» пункт «Run», или нажать

клавишу «F5», или на панели инструментов нажать кнопку

. Код

программы будет выполняться либо полностью, либо до точки останова, если

она есть.

Для того чтобы поставить точку останова, надо в окне «Disassembly»

поставить курсор на нужную строку, нажав правую кнопку мыши, и выбрать

пункт «Insert Breakpoint F9» (рис. 14), или нажать клавишу «F9», или просто

щелкнуть дважды на нужной строчке.

Рис. 14. Окно дизассемблера

Для удаления точки останова надо повторить то же действие. Точки

останова можно деактивировать командой «Disable Breakpoint Ctrl+F9».

37

На панели инструментов есть кнопки, позволяющие удалять и деактивировать

сразу все точки останова.

Можно редактировать код программы в окне дизассемблера в процессе

выполнения, поставив курсор на нужную строку, и, нажав правую кнопку

мыши, выбрать в контекстном меню пункт «Edit…».

Окна, используемые при отладке, можно удалять и восстанавливать,

используя в меню «View» пункты «Project Window», «Output Window»,

«Disassembly» и т.д.

В процессе выполнения программы необходимо следить за правильностью её

выполнения и состоянием памяти программ и данных, различных регистров и т.п.

Из меню «Memory» можно открыть окна, показывающие состояние памяти

программ, памяти данных, байтовой памяти и памяти ввода/вывода (рис. 15).

Рис. 15. Доступ к различным областям памяти

Окна состояния регистров открываются из меню «Register». Из этого меню

также можно открыть окно, показывающее состояние только выбранных нами

регистров, пункт «Custom…» и сохранить состояния всех регистров в

текстовом файле на жестком диске.

При изменении исходного кода программы мы должны очистить память от

данных, записанных туда при предыдущем выполнении программы, выполнив

пункт «Reset» в меню «Debug» или нажав кнопку

на панели инструментов.

После этого можно нажать «Run» или «F5», и VisualDSP++ предложит

сохранить программу. Сохранив новый код программы, можно начать её

выполнение с первой строки. При выполнении пункта «Build Project»

сохранение программы производится автоматически.

38

Для закрытия проекта надо в меню «Project» выбрать пункт «Close», для

выхода из среды разработки «VisualDSP++» в меню «File» − пункт «Exit».

Построение графиков сигналов

Для проверки работоспособности программы удобно использовать

графические возможности визуализации содержимого любой области

памяти

процессора,

которые

предоставляет

разработчику

среда

VisualDSP++. Для построения графика необходимо запустить программу на

выполнение. Важным условием построения является отсутствие ошибок.

Затем выбрать пункт меню «View \ Debug Window \ Plot \ New» (рис. 16).

Рис. 16. Создание графика

Появится окно настройки графика «Plot Configurations» (рис. 17). В этом окне

необходимо указать тип графика: в данном случае «X-Y Plot». В выпадающем

списке «Memory» должно быть установлено DM. Переключатель «Axis

Selection» установить в положение «X», нажать кнопку «Browse» и в

появившемся окне «Browse for Symbol» выбрать значение «Sin». В окне с

заголовком «Count» указать количество отсчетов сигнала, выводимых на

график. При переключателе «Axis Selection», установленном в положении «Y»,

в окне «Browse for Symbol» выбрать значение «Harmony».

39

Рис. 17. Окно настройки графического отображения

После всех установок нажать кнопки «Add» и «OK». В ходе работы программы

график генерируемого сигнала должен иметь вид, показанный на рис. 18.

Рис.18. График генерируемого сигнала

При необходимости можно задать вывод нескольких массивов данных в

одном окне (кнопка «New»), произвольно задавать оси для функциональных

зависимостей («Axis Selection»). При нажатии на кнопку «Settings» можно с

помощью установок, появляющихся в окне «Plot Settings» (рис. 19), определить

40

цвета линий и фона, размер полей, сетку, надписи на осях, масштаб,

минимальное и максимальное значения и т.д.

Рис. 19. Окно установок отображения графической информации

Полученные графики удобно экспортировать в файл формата jpg для

последующей работы, для этого в окне графика нужно нажать правую клавишу

мыши. В появившемся всплывающем меню выбрать пункт «Export...».

Появится окно «Export Plot» с вариантами экспортирования графика (рис. 20).

Переключатель назначения экспорта поставить в положение «File», кнопкой

«Browse…» выбрать путь к папке. В окне «Select plot export file» ввести имя

файла графика и нажать кнопку «Сохранить» (рис. 21).

41

Рис. 20. Окно экспорта графика

Рис. 21. Окно сохранения файла графика

6.

ЛАБОРАТОРНОЕ ЗАДАНИЕ

В соответствии с вариантом индивидуального задания, приведенного в

табл. 12, написать программу модуляции гармонического сигнала. Отладить и

запустить программу, построить графики генерируемого сигнала.

Номер варианта выбирается по номеру студента в списке группы. Частота

квантования 8 кГц. Недостающие параметры определить самостоятельно.

Обозначения в таблице: АМ – амплитудная модуляция, ЧМ – частотная

модуляция, ЧМн – частотная манипуляция, Амн – амплитудная манипуляция.

42

Таблица 12

Варианты индивидуального задания

Номер

задания

Вид модуляции

fнес, Гц

(средняя частота)

Fмод, Гц,

и соотношение

полупериодов

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

АМ

АМ

АМ

АМ

АМ

ЧМ

ЧМ

ЧМ

ЧМ

ЧМ

ЧМн

ЧМн

ЧМн

ЧМн

ЧМн

Амн

Амн

Амн

Амн

Амн

999

889

705

410

330

999

889

705

410

330

999

889

705

410

330

999

889

705

410

330

40

35

33

25

27

40

35

33

25

27

40 (0,9)

35 (0,55)

33 (0,67)

25 (0,5)

27 (0,7)

40 (0,9)

35 (0,55)

33 (0,67)

25 (0,5)

27 (0,7)

Коэффициент

модуляции,

девиация частоты

или разнос частот,

Гц

0,8

0,75

0,65

0,45

0,33

550

450

300

210

160

550

450

300

210

160

1

1

1

1

1

Содержание отчета

Отчет о лабораторной работе должен содержать:

1)

титульный лист;

2)

цель и задачи работы;

3)

листинги модифицированных и отлаженных программ;

4)

перечень ошибок, выявленных при отладке;

5)

результаты работы с графиками сигналов;

6)

выводы по работе.

КОНТРОЛЬНЫЕ ВОПРОСЫ

1.

Перечислите основные вычислительные модули процессора и расскажите

об их назначении.

2.

Каково назначение генераторов адресов данных?

3.

Перечислите назначение и состав программного автомата.

43

4.

Перечислите шины процессора и опишите их назначение.

5.

Каково назначение устройства обмена между шинами?

6.

Перечислите внутренние периферийные устройства семейства ADSP-21xx

и их назначение.

7.

Каково назначение главного интерфейсного порта?

8.

Охарактеризуйте работу программируемого таймера.

9.

Опишите программно-логическую модель ядра процессора и перечислите

устройства, входящие в ее состав.

10. Какова структура регистра ASTAT? Перечислить назначение флагов

регистра.

11. Для чего предназначены регистры SSTAT и MSTAT?

12. Какова структура регистра MSTAT?

13. Каково назначение регистра IMASK и значения отдельных битов этого

регистра?

14. Опишите назначение битов регистра ICNTL.

15. Каково назначение регистра IFC?

16. Перечислите категории команд сигнального процессора.

17. Перечислите источники ввода/вывода данных АЛУ.

18. Для чего предназначены регистры AX, AY, AR и AF в структуре АЛУ?

19. Перечислите источники ввода/вывода данных умножителя-накопителя.

20. Перечислите разновидности команд пересылки данных.

21. Напишите команды пересылки, предназначенные для работы с памятью

данных.

22. Напишите команды пересылки, предназначенные для работы с памятью

программ.

23. Опишите структуры многофункциональных команд.

24. Приведите примеры команд загрузки данных в стек.

25. Приведите примеры команд устройства сдвига.

26. Приведите примеры команд передачи управления в программе.

44

27. Охарактеризуйте форматы представления данных в микропроцессорах

семейства ADSP-21xx.

28. Опишите дробный и целочисленный режим вычислений умножителя и

приведите пример умножения в этих режимах.

29. Как определить формат результата при умножении различных чисел в

микропроцессорах семейства ADSP-21xx?

1.

Руководство пользователя по сигнальным микропроцессорам семейства

ADSP-2100 / пер. с англ. под ред. А. Д. Викторова. СПб. : Санкт-Петербургский

гос. электротехн. ун-т, 1997. 520 с.

2.

Марков С. Цифровые сигнальные процессоры / С. Марков. М. : Микроарт,

1996. Кн. 1. 144 с.

45

Учебное электронное текстовое издание

Дурнаков Андрей Адольфович

Дядьков Николай Александрович

АРХИТЕКТУРА И СИСТЕМА КОМАНД ЦИФРОВЫХ

СИГНАЛЬНЫХ ПРОЦЕССОРОВ СЕМЕЙСТВА ADSP-21XX

Редактор

Подготовка к публикации

Компьютерная верстка

И.В. Коршунова

Н.В. Лутовой

А.А. Дурнакова

Рекомендовано Методическим советом

Разрешен к публикации 27.12.2012

Электронный формат – pdf

Объем 2,42 уч.-изд. л.

620002, Екатеринбург, ул. Мира, 19

Информационный портал УрФУ

http://www.ustu.ru