Курс лекций МПСУ_Раздел 3_Организация микропроцессорных

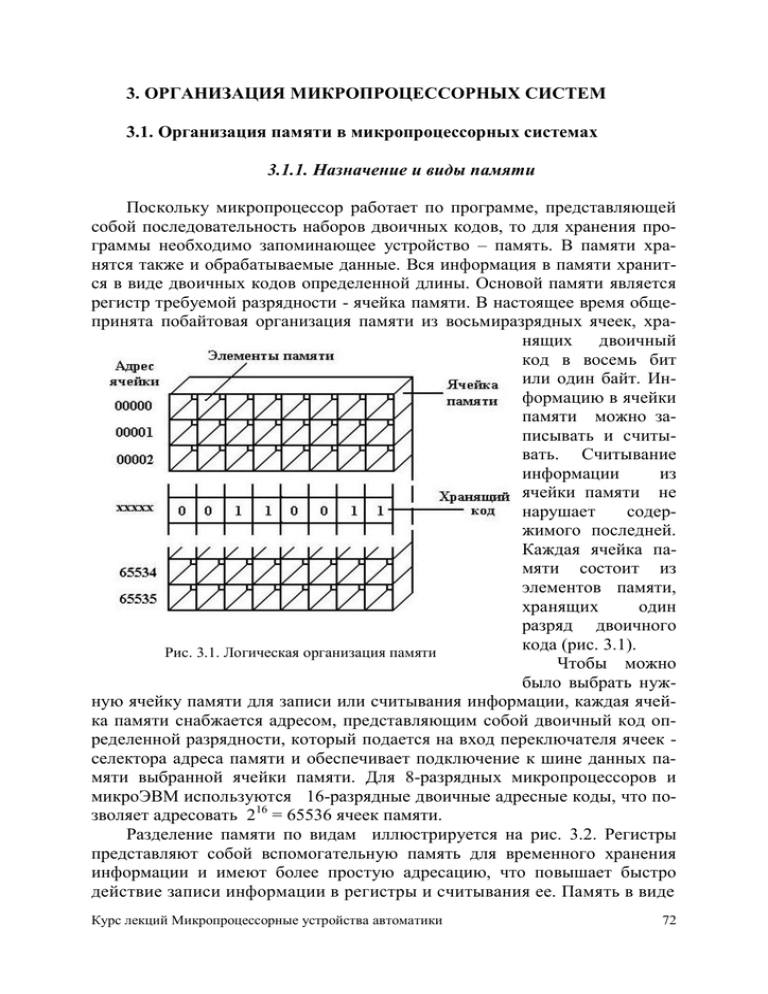

advertisement