VMK-Ps-L6-02 1.1 Структура и функционирование микропроцессора

advertisement

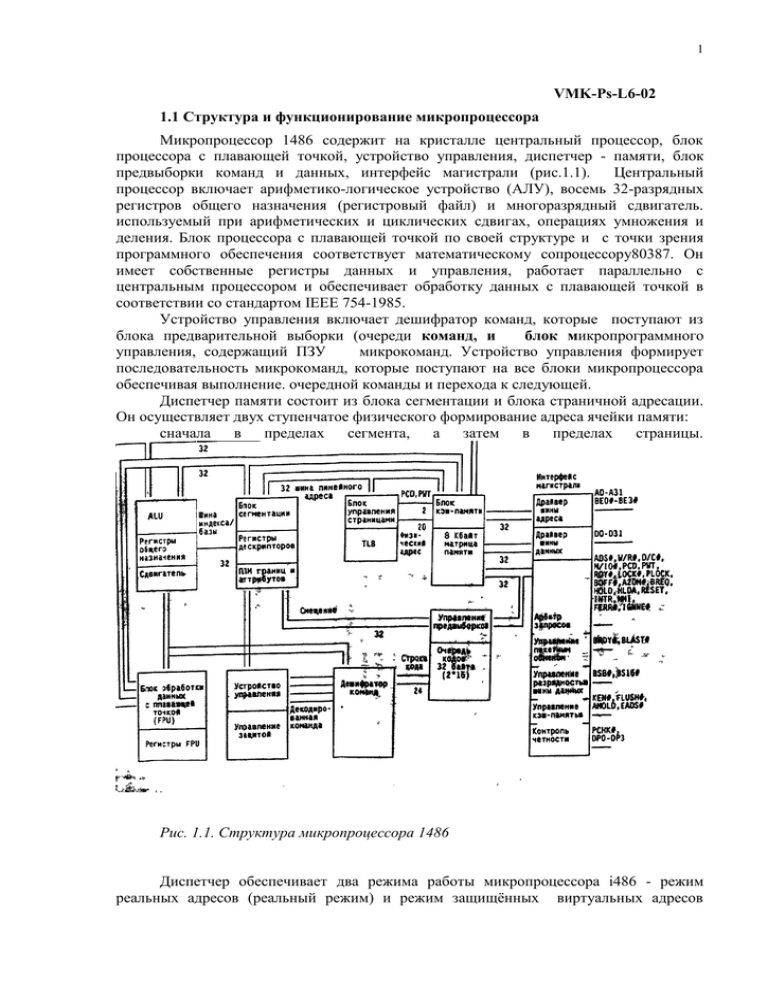

1 VMK-Ps-L6-02 1.1 Структура и функционирование микропроцессора Микропроцессор 1486 содержит на кристалле центральный процессор, блок процессора с плавающей точкой, устройство управления, диспетчер - памяти, блок предвыборки команд и данных, интерфейс магистрали (рис.1.1). Центральный процессор включает арифметико-логическое устройство (АЛУ), восемь 32-разрядных регистров общего назначения (регистровый файл) и многоразрядный сдвигатель. используемый при арифметических и циклических сдвигах, операциях умножения и деления. Блок процессора с плавающей точкой по своей структуре и с точки зрения программного обеспечения соответствует математическому сопроцессору80387. Он имеет собственные регистры данных и управления, работает параллельно с центральным процессором и обеспечивает обработку данных с плавающей точкой в соответствии со стандартом IEEE 754-1985. Устройство управления включает дешифратор команд, которые поступают из блока предварительной выборки (очереди команд, и блок микропрограммного управления, содержащий ПЗУ микрокоманд. Устройство управления формирует последовательность микрокоманд, которые поступают на все блоки микропроцессора обеспечивая выполнение. очередной команды и перехода к следующей. Диспетчер памяти состоит из блока сегментации и блока страничной адресации. Он осуществляет двух ступенчатое физического формирование адреса ячейки памяти: сначала в пределах сегмента, а затем в пределах страницы. Рис. 1.1. Структура микропроцессора 1486 Диспетчер обеспечивает два режима работы микропроцессора i486 - режим реальных адресов (реальный режим) и режим защищённых виртуальных адресов 2 (защищенный режим). В реальном режиме i 486 работает как очень быстрый микропроцессор 8086. При этом реализуется расширенный набор команд а допускается увеличение разрядности операндов и адресов до 32. В защищенном режиме могут одновременно выполняться несколько задач (программ). Задачи изолированы и защищены одна от другой и от операционной системы микропроцессора 1486. Специальный механизм обеспечивает переключение задач. Механизмы защиты и переключения задач подробно рассмотрены в гл. 5. Отметим, что в i486, как и в ряде предыдущих моделей (80286, 80386), используется четыре уровня защищенности (О, 1, 2, 3), определяющих возможность доступа к различным разделам (сегментам) памяти: уровень 0 - наибольшая защищенность, уровни 1, 2, 3 - более низкая степень защиты, которая уменьшается при возрастании номера уровня. Для каждой выполняемой программы (задачи) устанавливается один из четырех уровней привилегий, дающих право вызова сегментов: уровень 0 - максимальные привилегии, позволяющие вызывать сегменты с любым уровнем защищенности; уровень 3 минимальные привилегии, допускающие вы…зов сегментов только с минимальным уровнем защищенности 3; уровни 1, 2 имеют соответственно, промежуточные привилегии, Устанавливаемые с помощью этих уровней правила обращения обеспечивают эффективную защиту сегментов от несанкционированного доступа. Предусмотрены также возможности управления доступом к устройствам ввода/вывода. Сегментация является средством управления пространством логических адресов, она обеспечивает мобильность и повышает защищенность программ. Сегментированная память представляет собой набор блоков, характеризуемых определенными атрибутами, такими, как расположение, размер, тип (стек, программа, данные), характеристика защиты. В системе на основе микропроцессора 1486 каждой задаче доступны до 16387 сегментов величиной до 4 Гбайт каждый. Следовательно, обеспечивается возможность использования до 64 Тбайт виртуальной памяти для каждой задачи. Блок страничной адресации действует на более низком уровне, разбиение памяти на страницы возможно только в защищенном режиме. …………????????…….. Глава 7 Обмен по магистрали Магистраль микропроцессора 1486 является той архитектурной компонентой, которая в наибольшей степени отличает его от МП 80386. Изменения, внесенные в набор сигналов и протоколы обмена имели целью реализовать в виде увеличенной производительности i486 те преимущества в быстродействии и функциональной мощности набора внутренних блоков, которые появились за счет использования более совершенной микроэлектронной технологии. Микропроцессор i486 имеет 168выводный корпус с матричным расположением выводов. Изображение микросхемы со стороны выводов приведено в приложении 1, а список выводов по функциональным группам приведен в приложении 2. В этой главе описывается назначение сигналов на выводах i486, рассматриваются механизмы обмена по магистрали и различные типы магистральных циклов. Основа магистрали 1486, шины адреса и данных, в целом соответствует магистрали МП 80386. Отличие здесь заключается в том, что линии А2-А31 шины адреса стали двунаправленными. Главные нововведения связаны с изменением механизмов управления обменом, что затронуло структуру шины управления, тактовую сетку и набор циклов магистрали. В части управления обменом основными изменениями являются: машинный такт длительностью в период внешнего 3 синхросигнала, наличие механизма пакетной передачи для ускоренного заполнения внутренней кэш-памяти, улучшенный арбитраж магистрали, возможность организации 8-разрядной шины данных, контроль передаваемых данных по четности. В микропроцессоре i486 исключен механизм конвейерного формирования адресов и передаче данных, имевшийся в МП 80386. Вешний синхросигнал непосредственно тактирует работу i486. Следовательно, микропроцессор i486/25 использует внешний синхросигнал с частотой 25 МГц. а не 50 МГц, как МП 80386. Это существенно упрощает проектирование и изготовление систем на основе i486, снижает их стоимость 4 ….. Стр 179 процессора формирует или проверяет сигналы четности. Четтность определяется в том смысле, что соответствующий байт содержит чётное количество логических единиц. Сигналы четности генерируются во всех циклах записи данных в то время, когда данные выдаются микропроцессором. В циклах чтения данных сигналы четности должны быть введены в i486 по этим линиям для контроля правильности поступившей информации. Значения сигналов на этих линиях не влияют на ход выполнения программы. Реакция на ошибку четности возлагается на специальную аппаратуру контроля. Состояние контроля четности (РСНК#). Активный сигнал на этом выходе указывает на ошибку четности вводимых данных.. Чётность проверяется при чтении кода команды, чтении из памяти или порта ввода/вывода. В циклах подтверждения прерывания проверка чётности не выполняется. Сигнал РСНК# отображает результат контроля четности байтов, выбранных в соответствии с сигналами адресации байтов и сигналами определения разрядности шины данных. Правильное значение сигнала формируется только в такте непосредственно следующем за циклом чтения. В другие моменты времени сигнал пассивен. 5 Активность сигнала РСНК# показывает, что имеется несоответствие четности поступивших данных и значения сигнала на с соответствующем входе четности ОРi. Микропроцессор i486 не выдаёт вектора прерывания при обнаружении ошибки четности данных. Сигналы определения цикла магистрали (М/IO#, D/C# W/R#, LОСК#, РLОСК#) указывают тип выполняемого цикла магистрали. Сигнал W/R# разделяет циклы записи и циклы чтения, D/C# разделяет циклы данных и циклы управления, М/IO# разделяет циклы обращения к памяти и циклы ввода/вывода LОСК# сопровождает блокированные циклы магистрали, РLОСК# - псевдоблокированные циклы. Основными для определения типа цикла являются сигналы М/IO#, D/C# W/R#. Они имеют силу с момента активизации сигнала А05# (адрес уста! О. Определение типа цикла магистрали в зависимости от комбинации сигналов М/IO#, D/C# ,W/R#, дано в табл. 7.1. Сигнал LОСК# показывает, что i486 выполняет цикл типа чтение-модификация-запись, во время которого между чтением и записью он не может освободить магистраль. Циклы этого типа используются Стр180 как часть механизма семафоров во внешней памяти. Могут быть блокированы несколько циклов записи или чтения. Таблица 7.1. Типы циклов магистрали М/IO# 0 0 0 0 1 1 1 1 D/C# 0 0 1 1 0 0 1 1 W/R# 0 1 0 1 0 1 0 1 Тип цикла Подтверждение прерывания Октанов/Специальный цикл Чтение из устройства ввода/вывода Запись в устройство ввода/вывода Чтение кода из памяти Зарезервировано Чтение данных из памяти Запись данных в память Когда активизирован сигнал LОСК# , текущий цикл маги блокирован и микропроцессору i486 должно быть предоставл( ключительное право управления системной магистралью. LОСК# становится активным в первом такте первого блок» иого цикла магистрали, а в пассивное состояние возвращаете) прихода сигнала завершения последнего блокированного цикл При активном сигнале LОСК# микропроцессор 1486 н( верждает запрос захвата магистрали НОЫ). Если захват мага Произошел, выход 1.0СК4? переводится в третье состояние. Г тивизации сигнала КЕN# блокированные циклы чтения не I дят в циклы заполнения кэш-памяти. Псевдоблокированные циклы позволяют читать и записи память операнды длиннее 32 бит за один прием. Для перед< ких операндов требуется интервал времени более одного 1 рального цикла. Микропроцессор активизирует сигнал псевдс ровки LОСК# при чтении и записи операндов в формате с кмцсй точкой, чтении дескриптора таблицы сегмента и запо, строк кэш-памяти. При активном сигнале, РLОСК# другие активные уст1 микропроцессорной системы не могут получить управление ( ной магистралью. Сигнал запроса НОЬО не получает подтв ния в течение псевдоблокированных циклов записи и чтение Стр 187. 6 7.2. Механизмы обмена Передача данных между микропроцессором, памятью и другими устройствами системы выполняется с использованием несколльких механизмов обмена, каждый из которых характеризуется своим протоколом. Можно выделить следующие механизмы обмена по магистрали микропроцессора i486: запись/чтение отдельных операндов без использования кэш-памяти; пакетная передача данных; запись/чтение с использованием кэш-памяти команд и данных; обмен при динамическом изменении разрядности шины данных; обмен с использованием арбитража магистрали при работе нескольких процессоров или других активных устройств; обслуживание запросов внешних (аппаратных) прерываний; выполнение служебных операций. Протокол каждого механизма описывает асинхронную процедуру обмена сигналами управления и данными между микропроцессором и его окружением. Каждый механизм обмена имеет свою группу сигналов управления, но использует и часть общих. Привязка протоколов обмена к тактовой сетке приводит к формированию набора базовых циклов магистрали. Поскольку в реальной ситуации удобно использовать несколько механизмов обмена одновременно, то базовые циклы магистрали 486 имеют варианты, которые реализуются в случае одновременной активизации внешних и внутренних запросов, каждый из которых запускает свой механизм. Команды и данные передаются между i486 и другими устройствами системы в ходе цикла обмена (операции обмена), который может включать один или несколько магистральных циклов. Логические операнды: байт, слово, двойное слово - могут быть переданы без ограничений, связанных с выравниванием физических адресров. Данные доступны с любого байта, но при отсутствии выравнивания может понадобиться два иди три цикла магистрали. Циклы магистрали обеспечивают доступ к пространству физической памяти или пространству ввода/вывода. Периферийные устройства могут быть отображены на карту памяти, или на карту ввода/вывода, либо на обе из них. Адреса физической памяти имеют диапазон с 00000000Н по FFFFFFFFН (4 Гбайт). Адреса ввода/вывода, .... Стр193 7 Стр195 8 9