Проектирование цифровых устройств на программируемых

advertisement

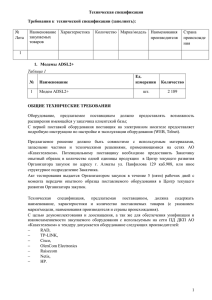

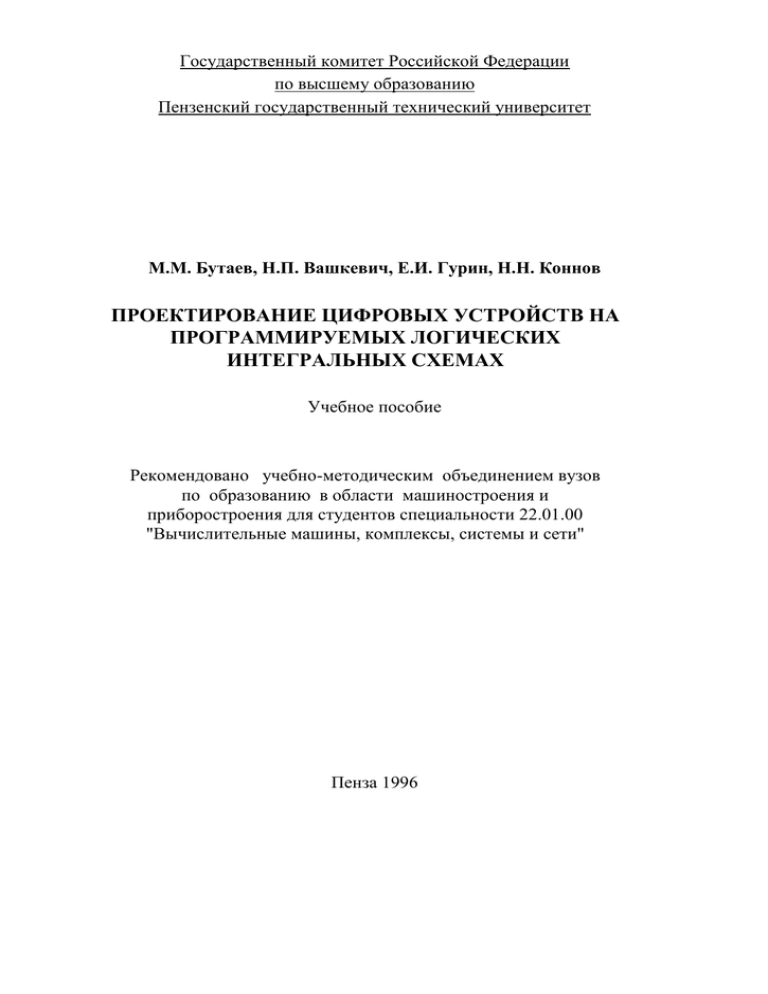

Государственный комитет Российской Федерации по высшему образованию Пензенский государственный технический университет М.М. Бутаев, Н.П. Вашкевич, Е.И. Гурин, Н.Н. Коннов ПРОЕКТИРОВАНИЕ ЦИФРОВЫХ УСТРОЙСТВ НА ПРОГРАММИРУЕМЫХ ЛОГИЧЕСКИХ ИНТЕГРАЛЬНЫХ СХЕМАХ Учебное пособие Рекомендовано учебно-методическим объединением вузов по образованию в области машиностроения и приборостроения для студентов специальности 22.01.00 "Вычислительные машины, комплексы, системы и сети" Пенза 1996 УДК 621.382:621.396.6 Б93 Бутаев М.М., Вашкевич Н.П., Гурин Е.И., Коннов Н.Н. Проектирование цифровых устройств на программируемых логических интегральных схемах: Учебн. пособие. - Пенза: Изд-во Пенз. гос. техн. ун-та, 1996. - с.: 27 ил., 1 табл., библиогр. 9 назв. Описываются структура и принципы функционирования различных типов программируемых логических интегральных схем (ПЛИС). Рассматриваются этапы проектирования цифровых устройств на ПЛИС с применением ЭВМ и способы программирования ПЛИС. Приводятся примеры проектирования конкретных устройств. Учебное пособие подготовлено на кафедре "Вычислительная техника" и предназначено для студентов специальности 22.01.00. Рецензенты: ГНПП "Рубин" к.т.н., доцент ИПК и ПРО А. И. Дралин Изд-во ПГТУ М.М. Бутаев, Н.П. Вашкевич, Е.И. Гурин, Н.Н. Коннов СОДЕРЖАНИЕ Ведение 1. Основные сведения о программируемых логических интегральных схемах 1.1. Структура ПЛИС 1.2. Основные этапы разработки схем на ПЛИС 1.3. Программирование ПЛИС 2. ПЛИС с гибкой логикой 2.1. Структура ПЛИС с гибкой логикой 2.2. Общие принципы проектирования схем на ПЛИС с гибкой логикой 2.3. Содержимое исходного файла 3. Программируемые пользователем вентильные матрицы 3.1. Структура программируемых пользователем вентильных матриц 3.2. Программируемые логические блоки 3.3. Организация связей 3.4. Организация памяти 3.5. Системы проектирования 3.6. Программирование микросхем 4. Примеры проектирования схем на ПЛИС 4.1. Проектирование типовых узлов 4.2 Проектирование пересчетных схем Литература Приложение 1. Справочные данные по языку PLDasm Приложение 2. Содержимое файла RPT ВВЕДЕНИЕ Все большее применение при разработке цифровых устройств находят программируемые логические интегральные схемы (ПЛИС). ПЛИС первого поколения имели достаточно простую структуру и содержали программируемую матрицу соединений с триггерами на выходах. Они использовались в основном для разработки несложных устройств управления. В настоящее время разработаны и применяются более сложные микросхемы, в том числе программируемые пользователем вентильные матрицы (ППВМ), которые по структуре приближаются к базовым матричным кристаллам. Однако в отличие от последних каждая ППВМ может программироваться многократно, что значительно снижает затраты на разработку новых устройств. Проектирование цифровых устройств с применением ПЛИС имеет свои особенности. Для разработки конкретных схем используются специально созданные системы автоматизированного проектирования, в которых для ввода могут использоваться языки описания схем или универсальные схемные редакторы типа OrCAD. Обязательным этапом является моделирование, во время которого проверяется правильность разработанной схемы. Для программирования микросхем применяются программаторы, использующие стандарт IEEE 1149.4 JTAG. Этот стандарт позволяет не только производить загрузку ПЛИС, но и проверять правильность работы микросхемы. Использование ПЛИС обеспечивает максимальную гибкость при необходимости модификации аппаратуры. Применение ПЛИС позволяет сократить процесс проектирования и отладки цифровых устройств. При этом время, требуемое для получения работающей микросхемы, составляет от нескольких часов до нескольких дней, весь процесс разработки и получения готовой микросхемы производится на одном рабочем месте. При подготовке пособия авторами использовались материалы популярных у разработчиков ПЛИС. В оформлении материалов пособия принимали участие студенты специальности 22.01.00 Стрижков Д. В. и Голдобеев А. С. 1. ОСНОВНЫЕ СВЕДЕНИЯЯ О ПРОГРАММИРУЕМЫХ ЛОГИЧЕСКИХ ИНТЕГРАЛЬНЫХ СХЕМАХ 1.1. Структура ПЛИС Программируемые логические интегральные схемы (ПЛИС) представляют собой БИС с регулярной структурой, которые могут программироваться пользователем для выполнения заданной функции. На практике для реализации комбинационных схем достаточно давно применяются программируемые логические матрицы (ПЛМ). Развитием этих схем явились комбинационно-поледовательные микросхемы типа КМ1554ХП4 и КМ1554ХП8, которые наряду с ПЛМ содержат регистровые схемы на выходе[1]. Более сложной схемой является программируемая пользователем ПЛИС ПЛ400 с ультрафиолетовым стиранием информации. По сравнению с предшествующими матричными логическими схемами она имеет большее количество триггеров и более широкие возможности проведения связей. Структура типовой ПЛИС приведена на рис.1.1. Схема имеет N триггерных ячеек ТЯ.1, ТЯ.2 ... ТЯ.N, M информационных входов I.1, I.2 ... I.M и вход синхронизации C. Выходы триггерных ячеек подключены к контактам I/O.1, I/O.2 ... I/O.N, которые могут программироваться в качестве входов или выходов в зависимости от структуры разрабатываемой схемы. Прямые и инверсные значения выходов триггерных ячеек, информационных входов и сигнала синхронизации подключены к логическому массиву соединений, выходами которого являются элементарные конъюнкции (термы) P.i. К каждой триггерной ячейке подключается K выходов логического массива P.1, P.1 ... P.K. На рис.1.2 приведена схема триггерной ячейки. В состав триггерной ячейки входит триггер (обычно D-триггер), элемент ИЛИ, на входы которого подключается K термов P.1 ... P.K с выхода логического массива, схема сложения по модулю два М2, переключатели K1 и K2. На управляющий вход триггера поступает сигнал Q.D, формируемый в виде дизъюнктивных нормальных форм с возможностью инверсии на схеме М2. Синхронизация триггера обычно осуществляется от общего сигнала C. Во многих схемах предусмотрена возможность задания сигнала синхронизации из логического массива. C I/O.1 K Òß.1 F.1 I.1 Ëîãè÷åñêèé I.2 I/O.2 K Òß.2 ìàññèâ F.2 ñîåäèíåíèé I.M I/O.N K Òß.N F.N Рис. 1.1 Структура ПЛИС Âûõîäû ëîãè÷åñêîãî ìàññèâà OE K1 I/O.i P1.i & 1 Q.D D M2 PK.i C IC & F.i T Q C K2 Рис. 1.2 Триггерная ячейка Переключатель K1 позволяет выдавать на выходной контакт как выход триггера Q, так и управляющий вход - Q.D. Сигнал OE=1 разрешает прохождение сигнала с контакта K1 на выход I/O.i. При OE=0 контакт I/O.i может при необходимости использоваться в качестве входа. Переключатель K2 определяет сигнал обратной связи F.i в логический массив: это может быть выход триггера или сигнал, поступающий на контакт I/O.i при использовании его в качестве входного. В ряде микросхем может использоваться двойная обратная связь F1.i и F2.i (рис. 1.3), при использовании которой в случае, если выход триггера не выводится на контакт микросхемы, в логический массив соединений могут одновременно подключаться выход триггера Q (или его вход - Q.D) и контакт I/O.i, используемый как вход. Сигнал OE в этом случае равен нулю, т. е. запрещает прохождение сигнала с переключателя K1 на I/O.i. При необходимости при соответствующих положениях K1 и K2 в обратную связь могут поступать одновременно сигналы Q и Q.D. OE K1 Q.D D C F1.i T I/O.i Q C K2 F2.i Рис. 1.3 Триггерная ячейка с двойной обратной связью На рис. 1.4 показана упрощенная схема логического массива соединений. Каждый из сигналов F.1 ... F.N и I.1 ... I.K при необходимости может подключаться к любой из горизонтальных линий P1.1 ... PK.N. На выходах последних вырабатываются элементарные логические произведения (термы). Похожая организация используется в программируемых логических матрицах. I.1 F.1 I.K F.N & & P1.1 Òß.1 PK.1 P1.N & & Òß.N PK.N Рис. 1.4 Логический массив Для создания конкретной схемы ПЛИС должна быть запрограммирована внешними схемами. При этом программируются как логический массив, так и триггерные ячейки. При программировании ПЛИС могут использоваться четыре варианта: однократно прожигаемые перемычки, электрически программируемые элементы с ультрафиолетовым стиранием, электрически перепрограммируемые элементы памяти и программируемые структуры на базе ЗУ с произвольной выборкой. В таблице показаны количественные характеристики зарубежных ПЛИС: количество триггерных ячеек (ТЯ), количество входов и особенности некоторых схем. Номе Тип ТЯ Вход Особенности р ы 1 5C032 8 10 2 5AC312 12 8 Двойная обратная связь 3 5C060 12 4 4 5C090 24 12 5 5C180 48 12 12 блоков по 4 ТЯ Как показано в таблице ПЛИС 5AC312 имеет двойные обратные связи. Кроме того эти схемы имеют одноступенчатые триггеры типа "защелка" на входах. Упоминавшаяся выше отечественная ПЛИС ПЛ400 имеет 40 контактов, содержит 24 триггерные ячейки, 12 информационных входов и общий вход синхронизации. 1.2. Основные этапы разработки схем на ПЛИС При разработке цифровых схем на ПЛИС можно выделить следующие этапы: - выбор ПЛИС, позволяющей реализовать нужную схему исходя из ее объема и быстродействия; - разработка схемы и ввод ее с помощью специального языка описания схем или универсального схемного редактора; - моделирование схемы с целью проверки правильности ее работы; - размещение схемы на кристалле и проведение связей; - трансляция введенной схемы в битовую последовательность; - загрузка этой последовательности (программирование ПЛИС). Для разработки заданной схемы могут использоваться специально созданные системы автоматизированного проектирования. Эти системы обычно создаются разработчиком ПЛИС. В них для ввода схемы применяются специальные языки описания схем или универсальные схемные редакторы типа OrCAD. Обязательным этапом является моделирование, во время которого проверяется правильность разработанной схемы. В качестве системы моделирования могут также применяться универсальные системы моделирования. Для программирования микросхемы используются специальные режимы загрузки. В различных ПЛИС эта операция может выполняться различными способами. Есть ПЛИС, в которых загрузка конфигурации производится также, как и в программируемых логических матрицах (ПЛМ). Однако в последнее время предпринимаются попытки стандартизации этой процедуры. Для этих целей был создан стандарт IEEE 1149.4 JTAG. Этот стандарт позволяет не только производить загрузку ПЛИС, но и проверять правильность работы микросхемы. Проверка производится специальным методом, получившим название в иностранной литературе "Boundary Scan" (периферийное сканирование, граничный просмотр). Более подробно данный стандарт описан ниже. 1.3. Программирование ПЛИС Программирование ПЛИС представляет собой загрузку данных конфигурации в микросхему для настройки на нужную функцию. Программирование может осуществляться с помощью различных способов, которые определяются разработчиком ПЛИС. Один из распространенных способов предусматривает загрузку данных словами (обычно байтами), что ускоряет ее, но требует дополнительных аппаратных затрат. В последнее время для программирования ПЛИС применяются программаторы, использующие специально созданный стандарт IEEE 1149.4 JTAG, при этом стандарта работой ПЛИС управляет специальный автомат TAP (рис. 1.5), для которого определены состояния запись команды (UPDATE-IR), сдвиг данных (SHIFT-DR), конец команды (EXIT-IR), захват данных (СAPTURE-DR), "прогон-тест/простой" (Run-Test/Idle) и др. При этом возможно программирование не только одной микросхемы, но и нескольких, если они объединены в одну цепь. На рис. 1.6 показаны три микросхемы: D1, D2 и D3, управление и синхронизация которых осуществляются сигналами TMS и TCK. Данные последовательно вдвигаются в ПЛИС на входы TDI и выдвигаются через выходы TDO. Массивы данных загружаются с помощью специальных команд. Рассмотрим их подробнее. Команда LDVECT (код 00101) используется для загрузки адреса строки или столбца и данных программирования. Регистр команд обновляется в состоянии UPDATE-IR конечного автомата контроллера TAP. Данные выдвигаются в состоянии SHIFT-DR. Команда IDCODE (код 00010) используется для считывания идентификационного кода устройства и идентификационных байт пользователя. Во время этого режима между выводами TD1 и TD0 подключается специальная цепь чтения регистра идентификации устройства. TEST-LOGIC RESET 1 0 RUN TEST/IDLE 0 1 SELECT DR-SCAN 1 1 SELECT IR-SCAN 0 0 1 1 CAPTURE-DR CAPTURE-IR 0 0 SHIFT-DR 1 SHIFT-IR 0 1 EXIT1-DR EXIT1-IR 0 0 PAUSE-DR 1 0 PAUSE-IR 0 EXIT2-DR 1 0 0 EXIT2-IR 1 1 UPDATE-DR 1 0 0 UPDATE-IR 1 0 Рис. 1.5. Работа автомата TAP под управлением сигнала TMS Команда FRGM (код 10101) используется для программирования ячеек EPROM. Адреса строк или столбцов и программные данные должны быть записаны заранее с помощью команды LDVECT. Программирование инициируется в состоянии Run-Test/Idle на первом снижающемся фронте TCK. Устройство должно оставаться в этом состоянии как минимум 200 мкс. TDI TDI TDO TDI D1 TMS TDO D2 TCK TMS TCK TDI TDO TMS TCK D3 TMS TCK TDO Рис. 1.6 Программирование микросхем в стандарте JTAG Программируемые данные верифицируются с помощью исключающего ИЛИ. Данные, подвергаемые операции "исключающее ИЛИ", записываются в регистр состояния "программирование-верификация" в состоянии CAPTURE-DR. Один бит данных может быть выдвинут в состоянии SHIFT-DR через вывод TDO. Во время этой операции адресные и программные данные не изменяются. Команда FREAD (код 00110) используется для считывания всей строки данных ПЗУ. Здесь требуется вдвигать только адрес строки. После вдвигания адресов строк устройство должно оставаться в состоянии RunTest/Idle как минимум 250 нс до сбора считываемых данных в состоянии CAPTURE-DR. Для этого режима отсутствует встроенная внутренняя верификация. Обычная операция заключается в загрузке команды FREAD и затем вводе состояния SHIFT-DR. Затем вдвигается адрес строки и вводится состояние Run-Test/Idle, пребывание в этом состоянии как минимум 250 нс. Затем вводится состояние CAPTURE-DR, в котором данные собираются в сдвиговые регистры. Собранные данные могут быть выдвинуты через вывод TDO в состоянии SHIFT-DR. Команда SWRITE (код 01111) используется для изменения содержимого битов ОЗУ Ей можно воспользоваться для осуществления реконфигурации устройства не изменяя содержимого ПЗУ. Данные, записываемые в ячейки ОЗУ, и адрес строки вдвигаются в состояние SHIFTDR. Операция записи в ОЗУ фактически осуществляется в состоянии RunTest/Idle контроллера TAP. Запись в SRAM инициируется на первом снижающемся фронте TCK в состоянии Run-Test/Idle и заканчивается на первом снижающемся фронте TCK после выхода из состояния Run-Test/Idle. В этом режиме отсутствуют верификация или считывание. Для считывания содержимого ячеек SRAM можно использовать команду SREAD. Обычная операция заключается в загрузке команды SWRITE, переходе в состояние SHIFT-DR, вдвигании данных и затем переходе в состояние Run-Test/Idle для осуществления записи. Пока устройство находится в режиме SWRITE, выводы пользователя остаются в состоянии высокого выходного сопротивления. Для активизации выводов регистр команд должен быть модифицирован новой командой (IDCODE, BYPASS и т.д.). Команда SREAD (код 10000) используется для считывания содержимого битов SRAM в массиве JEDEC. Необходимо вдвинуть только адрес строки. После вдвигания адреса строки устройство должно оставаться в состоянии Run-Test/Idle во время состояния SHIFT-DR. Данные собираются в регистры строк в состоянии CAPTURE-DR и могут быть выдвинуты в состоянии SHIFT-DR. Для этого режима отсутствует встроенная верификация. Обычная операция заключается в загрузке команды SREAD, переходе в состояние SHIFT-DR и загрузке адреса строки. Затем производится переход в состояние Run.Test/Idle, после которого - переход в состояние SHIFT-DR через состояние CAPTURE-DR и выдвижение данных. Команда UESCODE (код 10110) используется для считывания кода "Электронная подпись пользователя". UESCODE может быть запрещен к выдаче с помощью команды FRGM. Эта команда аналогична команде FREAD. Однако отсутствует необходимость вдвигать адрес строки для считывания содержимого UES. Команда RADLOAD (код 11000) загружает 6 битов адреса строки. Она используется в файлах BSDL для обеспечения соответствия стандарту программирования устройства и внутренней реконфигурации. Команда PORST (код 10100) может использоваться для переключения iFX780 или iFX740 в ее первоначальное состояние. Конфигурация устройства пересчитывается с битов EPROM. После загрузки команды производится переход к состоянию TEST-LOGIC RESET. Использование этих команд позволяет программировать ПЛИС, а также считывать загруженные данные. 2. ПЛИС С ГИБКОЙ ЛОГИКОЙ 2.1. Структура ПЛИС с гибкой логикой В последнее время получили распространение ПЛИС, которые могут программироваться многократно. Такие схемы получили название ПЛИС с гибкой логикой (от англ. FLEXlogic). Матрицы iFX780 и iFX740 фирмы Intel являются двумя представителями семейства программируемых логических устройств типа FLEXlogic. На рис. 2.1 показана структура такой ПЛИС. В состав схемы JTAG ÏÇÓ Ñòàòè÷åñêîå ÎÇÓ Êîíôèãóðàöèÿ 10xI/O ÏËÁ0 10xI/O ÏËÁ2 Ìàññèâ ÏËÁ1 10xI/O ÏËÁ3 10xI/O ñîåäèíåíèé 10xI/O ÏËÁ4 ÏËÁ5 10xI/O 10xI/O ÏËÁ6 ÏËÁ7 10xI/O Рис. 2.1 Структура ПЛИС с гибкой логикой входят восемь программируемых логических блоков ПЛБ0 ... ПЛБ7 и массив соединений. Каждый программируемый логический блок имеет десять выходов I/O и два варианта конфигураций: десять триггерных ячеек или ОЗУ размером 128x10 бит. Конфигурация схемы размещается в статическом ОЗУ. Эта конфигурация при включении питания автоматически считывается из электрически программируемого постоянного ЗУ (ПЗУ) и записывается в ОЗУ. Если необходимо, можно также записать новую конфигурацию в ОЗУ, не изменяя содержимого ПЗУ. Этот процесс называется реконфигурацией. Таким образом, если функция ПЛИС будет неизменной, внутреннее ППЗУ может программироваться один раз. Разработчику в этом случае не нужно вникать в детали программирования или реконфигурации. Эта конфигурация будет действовать до отключения питания или пока не будет записана новая конфигурация. Конечным результатом реконфигурации является изменение функции ПЛИС. Это может потребоваться при макетировании, когда функция меняется неоднократно. Можно также изменять функции ПЛИС в течение срока службы изделия, когда внешнее устройство управления (обычно микропроцессорное) может осуществить внутрисхемную реконфигурацию ПЛИС. Как программирование ППЗУ, так и реконфигурация осуществляются через интерфейс JTAG. На рис. 2.2 показана организация логики для случая, когда ПЛБ определен в виде триггерных ячеек. В этом случае к каждому из десяти триггеров T1 ... T10 подключается логическая схема, содержащая три элемента ИЛИ и переключатели. Кроме того, в каждом блоке вырабатывается сигнал равенства двух 12-разрядных чисел A=B. Ячейки 2 ... 9 имеют двухвходовые схемы ИЛИ. Крайние ячейки 1 и 10 имеют одну 12входовую схему ИЛИ. Каждая ячейка при необходимости может занимать у соседней ячейки по одной схеме ИЛИ, что достигается соответствующей установкой переключателей. Таким образом, ячейки 2 ... 9 могут задавать логические функции в виде дизъюнктивных нормальных форм, содержащих от 2 до 8 термов, а ячейки 1 и 10 - от 12 до 16 термов. Положение переключателей задается путем программирования микросхемы. P1.1 & 1 P1.12 & 1-1 P1.13 & 1 P1.14 & 1 T1 3-1 2-1 A=B P2.1 & 1 1 P2.2 & T2 1-2 3-2 P2.3 & P2.4 & Pi.1 & 1 2-2 A=B 1 A=B 1 Pi.2 & Pi.3 & 1 Pi.4 & 2-i Ti 1-i 3-i A=B Рис. 2.2 Организация логики в ПЛИС На рис. 2.3 показана организация триггерной ячейки. В ее состав входят триггер, который может программироваться как D- или T- триггер, мультиплексоры MS1 ... MS5, переключатели K1 ... K3, схемы сложения по модулю 2, с помощью которых в данной схеме может осуществляться инверсия. Синхронизация триггера может производиться с помощью сигналов CLK1, CLK2, их задержанных значений, а также с помощью "асинхронных" C/P2 C/P1 MS3 OE1 OE2 MS1 È1 VCC GND Q.D Si I/O Q PR D/T CLK1 Q È2 Çàäåðæêà K1 CLK1 CLK2 MS5 Çàäåðæêà K2 CL CLK2 MS2 ACLK1 ACLK2 C/P2 C/P1 F1.i Ìàññèâ ñîåäèíåíèé F2.i K3 Äâîéíàÿ îáðàòíàÿ ñâÿçü Рис. 2.3 Организация ПЛБ MS4 сигналов ACLK1 и ACLK2. Асинхронный сброс и установка триггера осуществляется с помощью сигналов C/P1 и C/P2. 2.2. Общие принципы проектирования схем на ПЛИС с гибкой логикой Для программирования iFX780 или iFX740 необходимо выполнить следующие этапы (рис. 2.4): 1. С помощью любого редактора создается исходный файл с расширением .PDS. 2. Производится компиляция исходного файла, в результате которой создаются файлы ошибок (расширение .ERR), отчета (расширение .RPT) и др. 3. Создается стандартный промежуточный файл JEDEC (JEDEC объединенный совет по электронным приборам), пользуясь командным языком PLDshell или какими-либо другими средствами разработки. 4. С помощью программы загрузки файл JEDEC преобразуется в битовую последовательность двоичных строк, которые записываются в iFX780 посредством интерфейса JTAG. EDIT Ñîçäàíèå èñõîäíîãî ôàéëà PDS COMPILE/SIM (PLDasm) Êîìïèëÿöèÿ è ìîäåëèðîâàíèå VIEW PROGRAM Ëèñòèíãè, îøèáêè è äðóãèå ôàéëû Ñðåäñòâà ïðîãðàììèðîâàíèÿ .ERR, .RPT, .HST, .TRF Ïðîãðàììà çàãðóçêè JEDEC FILE .JED Ïðîãðàììèðîâàíèå ÏËÈÑ Рис. 2.4 Последовательность проектирования схем на ПЛИС ПЛИС фирмы INTEL - это семейство программируемых логических устройств, конфигурация которых записывается в статическом ОЗУ на кристалле. Одна из особенностей этого семейства заключается в том, что данная конфигурация может быть изменена внутрисхемно через интерфейс JTAG без подачи какого-либо специального напряжения. Устройство iFX780 имеет энергонезависимую память на кристалле, где хранится одна конфигурация. Когда включается питание устройства, конфигурация записывается в статическое ОЗУ (SRAM) на кристалле, и приводит ее в рабочее состояние. Устройство iFX780 не обладает способностью считывать конфигурацию из внешней памяти, поэтому если оно подлежит реконфигурации, требуется какой-то внешний контроллер (микроконтроллер, конечный автомат и т.д.), который загрузит новую конфигурацию в ПЛИС через интерфейс JTAG. Первый этап в формировании конфигурации устройства - создание файла JEDEC. Это может быть осуществлено с помощью PLDshell - средства, поставляемого фирмой Intel, или средства, выпускаемого какой-либо другой фирмой. Файл JEDEC полностью описывает, какая конфигурация придается устройству. Файл JEDEC имеет такую форму, в которой он не может быть передан непосредственно в порт JTAG, не может он также считываться контроллером, формирующим конфигурацию. Эти требования полностью зависят от контроллера, и в некоторых случаях необходимо, чтобы разработчик преобразовывал распространенный формат данных в более частный. Программа JED2JTAG преобразует файл JEDEC в потоки бит, которые имеют соответствующий формат для передачи их в порт JTAG устройства FLEXlogic. Он также предоставляет разработчику возможность выбора из трех различных выходных форматов. Контроллер может использовать один из этих форматов непосредственно, или, при невозможности этого, выходные данные JED2JTAG могут преобразовываться с тем, чтобы они соответствовали требованиям конкретной разработки. 2.3. Содержимое исходного файла В состав исходного файла должны входить секции: секция определений, секция проектирования, секция моделирования. Секция определений содержит заголовок, режимы работы, задание используемых модулей, тип используемой микросхемы, описание контактов и др. Заголовок содержит следующие строки: Title - наименование проекта; Pattern - стандартое расширение исходного файла (обычно PDS); Revision - количество проходов (обычно один); Author - фамилия автора; Company - место работы (учебы); Date - текущая дата. В качестве примера можно использовать следующий заголовок: Title COUNTER Pattern PDS Revision 1 Author PETROW Company PGTU Date 20/4/95 Для описания режимов используется ключевое слово OPTIONS. Данная часть секции является необязательной. Необходимые режимы устанавливаются по умолчанию, поэтому эту секцию включать необязательно. Для задания используемых модулей при иерархическом проектировании используется ключевое слово DEFMOD, после которого следует имя модуля и список аргументов. Тип используемой микросхемы задается после ключевого слова PIN. Среди возможных имен можно использовать, например, следующие:85C220, 85C224, 5AC312, 5C060, 5C090, PLD22V10, FX740_44, FX740_68, FX780_84, FX780_132 и др. Описание контактов включает ключевое слово PIN, после которого следует описание контакта, которое включает номер контакта и его сигнал. Например, строка PIN 1 CLOCK описывает контакт 1, на который поступает синхросигнал. Номер контакта может отсутствовать. В этом случае система сама определит номер. Так, например, строка PIN UPDOWN описывает контакт, на который подается сигнал UPDOWN (этот сигнал может поступать извне или вырабатываться микросхемой). Следующие строки описывают задание группы сигналов на контакты: PIN 2 I1 PIN 3 I2 PIN 4 I3 PIN 5 I4. Такой же результат можно получить с использованием так называемой векторной нотации: PIN [2:5] I[1:4]. Описание контакта может также задавать тип триггерной ячейки. Так, например, строка PIN Q задает ячейку, показанную на рис. 1.2, в которой выход триггера Q через ключ K1 проходит на выход ячейки и одновременно через ключ K2 поступает через обратную связь в логический массив. Сигнал OE при этом задается равным единице (OE=VCC). С помощью ключевого слова NODE описывается так называемый спрятанный контакт. Для него будет зарезервирован триггер, однако он не выводится на выходной контакт микросхемы. Ключевое слово COMB описывает функцию возбуждения триггера. Так, например, строка PIN 1 Q1 COMB задает выход на контакт 1 сигнала Q1.D, поступающего на вход D-триггера. Схема триггерной ячейки для такого описания приведена на рис. 2.5. На этом рисунке не показаны схемы ИЛИ и М2. На выход через ключ K1 проходит сигнал Q1.D. В качестве обратной связи в зависимости от положения перключателя K2 может использоваться выход Q1 или Q1.D. Ключевое слово CMBFBK задает в качестве обратной связи функцию возбуждения триггера Q1.D, например описание PIN 1 Q1 COMB REGFBK соответствует положению переключателей на рис. 2.5. OE=VCC K1 Q1.D D C F.i=Q1 T I/O.i=Q1 Q1 C K2 Рис. 2.5 Триггерная ячейка с комбинационным выходом Для ячейки с двойной обратной связью, показанной на рис. 1.3, должно быть задано следующее описание: PIN Q REG CMBFBK. Секция проектирования должна содержать как минимум одну из следующих подсекций: EQUATION - описание уравнений; STATE - описание состояний; T_TAB - табличное описание схемы. Подсекция описания уравнений должна начинаться с ключевого слова EQUATION. В уравнениях могут использоваться следующие операции * - логическое умножение (И); + - логическое сложение (ИЛИ); :+: - сложение по модулю 2; / - функция отрицания, активный низкий уровень; = - присвоение для комбинационного выхода; := - присвоение для триггерного выхода. Так, например, для триггерного выхода Q1 и логического выхода A1 могут быть заданы следующие уравнения: Q1 := IN1 + IN2; A1 = /(IN1 + IN2) * IN3 + (IN4 :+: IN5) * /IN6. Для каждого триггера могут использоваться компоненты: .CLKF - сигнал синхронизации; .TRST - разрешение выхода; .RSTR - сигнал очистки; .SETF - сигнал установки; .D - информационный вход; .FB - сигнал обратной связи. Так, например, сигнал разрешения выхода для триггера Q1 может быть задан следующим выражением: Q1.TRST = IN1 * IN2. Асинхронный сброс триггера Q1 задается выражением Q1.RSTR = IN2 + IN3. Описание состояний автомата должно начинаться с ключевого слова STATE. Состояния могут описываться переменными S0, S1 и т.д. В исходном файле должно быть предусмотрено кодирование состояний. Пусть имеется четыре состояния, закодированныx следующим образом: S0 = /Q1 * /Q0 S1 = /Q1 * Q0 S2 = Q1 * Q0 S3 = Q1 * /Q0 Переходы между состояниями описываются так: S1 := UP -> S2 + DOWN -> S4, что задает переход из состояния S1 в состояние S2 под действием сигнала UP и в состояние S4 под действием сигнала DOWN. Возможно задание переходов по умолчанию: DEFAULT_BRANCH S0 - переход в S0, DEFAULT_BRANCH HOLD_STATE - переход в текущее состояние, DEFAULT_BRANCH NEXT_STATE - переход в следующее состояние. Табличное описание схемы должно начинаться с ключевого слова T_TAB. В качестве примера можно привести следующее задание переменных C1 . . C4 на основе аргументов I1 . . I4. ( I1 I2 I3 I4 >> C1 C2 C3 C4 ) 1 0 0 0 : 1 0 0 0 0 1 0 0 : 0 1 0 0 0 0 1 0 : 0 0 1 0 0 0 0 1 : 0 0 0 1 ПЛБ в ПЛИС типа FLEXlogic может конфигурироваться как блок ОЗУ размером 128x10. Блок ОЗУ может иметь десять входов данных, семь входов адреса, до десяти выходов, три входа управления: блок доступен - BE, запись разрешена - WE, чтение разрешено - OE (рис. 2.6). Для сигналов управления активным является низкий уровень. Задание блока в качестве ОЗУ можно осуществлять записью PIN BUFRAM[9:0] RAM Значения сигналов управления могут задаваться следующим образом: BUFRAM[9:0].DATA = DIN[9:O] ; 10 входов данных BUFRAM[6:0].ADDR = A[6:O] ; 7 линий адреса BUFRAM.BE = ENABLE_ ; сигнал блок доступен BUFRAM.WE = WR_ ; сигнал запись разрешена BUFRAM.TRST = OE_ ; сигнал чтение разрешено. Отдельные выводы могут быть скрыты (или физическим устройством, или пользователем ). Для примера показано как можно скрыть биты ОЗУ 5 и 7...9: BUFRAM5.TRST = VCC BUFRAM[7:9].TRST = VCC По умолчанию ОЗУ может инициализироваться как RAM DEFAULTS, например, запись CLK1 CLK1 Çàäåðæ. CLK1 CLK2 CLK2 Çàäåðæ. CLK2 7 Àäðåñ Äàííûå ÎÇÓ BE OE WE Mcell I/O Mcell I/O Mcell I/O 10 Рис. 2.6 Запоминающее устройство RAM_DEFAULTS myrom ;адрес значение 0 : OxF [Oxl:OxF] : OxO [Ox10:Ox7F] : Ox3FF; или DEFAULT_VALUE Ox3FF будет устанавливать первое слово равным значению 15, следующие 15 слов нулю, а остальные слова установит равным значению 3FFh. Для слияния отдельных файлов в единый проект можно использовать процедуру Merge так, как это показано на рис. 2.7. Секция моделирования начинается с ключевого слова SIMULATION Для задания отдельных сигналов можно использовать ключевое слово SETF. Например, запись SETF /CLKPIN /ILE I1 /I2 I3 производит следующие присваивания: CLKPIN=0 ILE=0 I1=1 I2=0 I3=1. .PDS File Merge .PDS File .PDS File Рис. 2.7 Слияние файлов Моделирование синхросигнала удобно осуществлять оператором CLOCKF, который задает один импульс. Например, запись CLOCKF CLK задает один импульс сигнала CLK. Для задания вектора используется ключевое слово VECTOR. Запись VECTOR V := [ Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0 ] обеспечивает вывод в виде вектора выходов Q7 ... Q0. Для задания повторяющихся действий используется оператор FOR, после которого должно стоять ключевое слово BEGIN, отмечающее начало повторяющейся последовательности. Конец оператора FOR задает ключевое слово END. Пример: задать действие 39 синхросигналов CLK. FOR I := 0 TO 38 DO BEGIN CLOCKF CLK END Предварительная установка задается оператором PRLDF. Запись PRLDF /Q1 /Q0 обеспечивает начальную установку Q1, Q0 в нулевое состояние. 3. ПРОГРАММИРУЕМЫЕ ПОЛЬЗОВАТЕЛЕМ ВЕНТИЛЬНЫЕ МАТРИЦЫ 3.1. Структура программируемых пользователем вентильных матриц Программируемые пользователем вентильные матрицы (ППВМ) включают в себя три главных программируемых элемента (рис.3.1): нескоммутированные программируемые логические блоки (ПЛБ), блоки ввода-вывода (БВВ) и внутренние связи. ПЛБ являются функциональными элементами для построения логики пользователя, БВВ обеспечивают связь между контактами корпуса и внутренними сигнальными линиями. Программируемые ресурсы внутренних связей обеспечивают управление путями соединения входов и выходов ПЛБ и блоков ввода-вывода на соответствующие сети. Необходимая конфигурация устанавливается с помощью программирования внутренних статических ячеек памяти, которые определяют логические функции и внутренние соединения. Наиболее распространенным семейством ППВМ являются микросхемы серии XC фирмы XILINX. Среди них выделяются три крупных семейства: XC2000, XC3000 и XC4000. ППВМ обеспечивают эффективное проектирование схем и снижают время разработки и риск ошибок, свойственных обычным матрицам логических вентилей. ППВМ имеют большой набор ресурсов проведения соединений, что особенно удобно при реализации сложных схем с большим количеством связей. Устройства настраиваются с помощью загрузки данных конфигурации во внутренние ячейки памяти. ППВМ может либо активно считывать данные о своей конфигурации из внешнего последовательного или байтпараллельного ПЗУ (основные режимы), либо данные о конфигурации могут быть записаны в ППВМ внешним контроллером. Семейства ППВМ поддержаны мощным и сложным программным обеспечением, охватывающим все аспекты проекта: схемный ввод, моделирование, автоматическое размещение и проведение связей и, наконец, создание битового потока конфигурации. Ñõåìû çàãðóçêè Ñòàòè÷åñêîå ÎÇÓ Êîíôèãóðàöèÿ Âíóòðåííèå ñâÿçè Á Á Á ÏËÁ Á ÏËÁ Á ÏËÁ Á Á Á Á Á ÏËÁ ÏËÁ ÏËÁ Á ÏËÁ ÏËÁ ÏËÁ Á Á Á Á Á Âíåøíèå ñâÿçè Рис. 3.1 Структура ППВМ Возможность многократного перепрограммирования ППВМ позволяет использовать их в проектах, где аппаратные средства ЭВМ изменяются динамично или должны приспосабливаться к различным прикладным задачам пользователя. ППВМ позволяют сократить цикл проектирования и разработки. Плотность логических элементов ППВМ достигает 20000 вентилей, а частота синхросигнала - 50 MГц. Использование усовершенствованной, высокоточной технологии, а также архитектурных усовершенствований способствуют этому увеличению возможностей ППВМ. Однако достижение этой высокой плотности логических элементов и уровней характеристик требует также новых и более мощных автоматизированных систем проектирования. Устройства ППВМ могут быть повторно конфигурированы для изменения логической функции, когда они размещены в системе. Это дает проектировщику системы новые возможности, не доступные при любом другом типе логики. Аппаратные средства ЭВМ могут быть изменены так же просто, как программное обеспечение. Обновление проекта или его модификация выполняется легко. ППВМ могут динамически повторно конфигурироваться для исполнения различных функций в разное время. Перепрограммируемая логика может использоваться для реализации системы самодиагностики, создания системы, способной к повторному программированию для различных окружающих сред или действий. Дополнительной выгодой от использования перепрограммируемых устройств ППВМ является упрощение конструкции аппаратных средств и их отладки и сокращение времени подготовки изделия к продаже. 3.2. Программируемые логические блоки Организацию программируемого логического блока (ПЛБ) рассмотрим на примере блока семейства XC4000. Основные элементы ПЛБ показаны на рис. 3.2. Каждый ПЛБ содержит пару триггеров T1 и T2 и два независимых генератора функций G и F на четыре входа каждый. Два функциональных генератора предоставляют проектировщикам большую гибкость, так как в большинстве случаев требуются комбинационные логические функции меньше, чем на четыре входа. Тринадцать входов и четыре выхода ПЛБ обеспечивают доступ к генераторам функций и триггерам. Эти входы и выходы связаны с программируемыми ресурсами внутренних связей. Каждый из этих генераторов функций имеет по четыре входа F1 ... F4 и G1 ... G4. Каждый из генераторов способен реализовать любую произвольно определенную булеву функцию из четырех переменных. Генераторы функции реализованы как таблицы памяти, поэтому задержка распространения независима от осуществляемой функции. C1 C2 C3 C4 H1 DIN S/R EC Óïðàâëåíèå ñáðîñîì T1 Ìóëüòèïëåêñîðû G4 G3 G2 G1 SD D G' Q YQ T1 EC RD H' 1 Óïðàâëåíèå ñáðîñîì T2 Y F4 F3 F2 F1 F' SD D Q XQ T2 Ìóëüòèïëåêñîðû EC K RD 1 Ìóëüòèïëåêñîðû Рис. 3.2 Программируемый логический блок X Третий генератор функции, помеченный H', может осуществить любую булеву функцию из трех входов F', G' и входа из внешнего блока (H1). Сигналы от генераторов функции могут поступать на два выхода: F' или H' может выдаваться на выход X, а G' или H' - на выход Y. Таким образом, ПЛБ может использоваться для реализации любых двух независимых функций четырех переменных, любой единственной функции пяти переменных или любой функции четырех переменных вместе с некоторыми функциями пяти переменных. Можно осуществить даже некоторые функции до девяти переменных. Реализация широких функций в едином блоке сокращает число требуемых блоков и задержку распространения сигнала, обеспечивая увеличение плотности и быстродействия. Два элемента памяти в ПЛБ являются динамическими D-триггерами с входами общей синхронизации K и разрешения синхронизации EC. Третий общий вход (S/R) может быть запрограммирован или как вход асинхронной установки или как сигнал сброса независимо для каждого из двух регистров. Отдельная общая линия установки-сброса, не показанная на рис.3.2, выполняет установку или сброс всех регистров при включении, перепрограммировании или при активизации управления специализированной сетью сброса. Эта сеть сброса не соединена с другими ресурсами проведения соединений. Она может быть связана с любым контактом корпуса как вход общего сброса. Каждый триггер может быть переключен или передним, или задним фронтом синхросерии. Источник входных данных триггера может программироваться, управление осуществляется либо с помощью функций F', G' и H', либо с помощью прямого входа блока DIN. Триггеры управляют выходами XQ и YQ программируемого логического блока. Мультиплексоры в ПЛБ устанавливают соответствие четырех входов управления, помеченных C1 ... C4 на рис. 3.2, четырем внутренним сигналам управления (H1, DIN, S/R и EC) любым произвольным способом. Гибкость и симметрия архитектуры ПЛБ облегчает размещение и проведение соединений для данного применения. Так как генераторы функции и триггеры имеют независимые входы и выходы, с каждым из них можно обращаться как с самостоятельным объектом при размещении для достижения высокой плотности упаковки. Входы, выходы и функции непосредственно могут свободно обмениваться местами в пределах ПЛБ для исключения перегрузки соединений при выполнении операций размещения и проведения соединений. Кроме того, каждый из генераторов функции ПЛБ F' и G' содержит специализированную арифметическую логику для быстрой генерации сигналов переноса и заема, значительно повышающую эффективность и производительность сумматоров, вычитателей, аккумуляторов, компараторов и даже счетчиков (рис. 3.3). Эта логика может быть инициирована при COUNT A1 G4 G3 MS1 LF1 G’ MS2 G2 SUM 1 G1 ... G4 B1 G1 CL1 MS3 CIN1 CIN2 CL2 MS4 F4 F3 B0 F2 A0 F1 LF2 SUM 0 F’ F1 ... F4 Рис. 3.3 Организация арифметических операций программировании. Два генератора функции с четырьмя входами могут программироваться как двухразрядный сумматор с встроенным переносом, который может быть расширен на любую длину. Эта специальная схема переноса так быстра и эффективна, что обычные методы ускорения распространения переноса неэффективны уже при 16 разрядах и дают слабый эффект при 32 разрядах. Схема 16-разрядного сумматора требует девять ПЛБ и имеет задержку комбинационных схем в 20.5 нс. Быстрая схема переноса открывает доступ к большому количеству новых применений, использующих арифметические действия, где предыдущие поколения ПЛИС не были достаточно быстры и эффективны. Например: быстродействующие вычисления адреса смещения в микропроцессоре или графических системах или быстродействующее сложение в цифровой обработке сигналов. Схема быстрого переноса семейства XC4000 содержит два разряда счетчика в каждом ПЛБ и работает с ними при частоте синхронизации до 42 MГц для 16 разрядов, при этом счетчики могут быть загружаемыми. Для 16-разрядного реверсивного счетчика это означает удвоение скорости. Изобилие триггеров в ПЛБ позволяет проектировщику использовать конвейерную обработку. Это мощный путь увеличения производительности за счет разбиения функции на меньшие подфункции и параллельного их выполнения с передачей результатов через переключатели конвейера. Конвейерный метод может использоваться там, где общая производительность важнее простой задержки. В ППВМ имеются также схемы многоразрядного декодирования. Семейство XC4000 имеет четыре программируемых декодера. Каждый из этих декодеров с встроенной функцией И способен принимать до 42 входов в БИС XC4005 и до 72 в XC4013. Эти специализированные декодеры принимают сигналы ввода-вывода и внутренние сигналы как входные и формируют внутренний сигнал декодирования через 18 нс, считая от контакта до контакта. Таким образом, достаточно большие ПЛМ могут быть эмулированы с помощью дизъюнкции выходов декодера ПЛБ. Эта особенность декодера компенсирует то, что раньше считалось недостатком ППВМ. 3.3 Организация связей Связи между блоками сделаны металлическими проводниками с программируемыми пунктами переключения и матрицами переключений. Они состоят из металлических сегментов с программируемыми точками переключений, реализующими желаемое проведение соединений. Изобилие различных ресурсов проведения соединений обеспечивает достижение эффективного автоматизированного проведения соединений. Имеются три главных типа связи, различаемых относительной длиной их сегментов: линии единичной длины, линии двойной длины и длинные линии. Линии единичной длины представляют собой сетку горизонтальных и вертикальных линий, которые пересекаются в матрице переключений (МП) между каждым блоком. На рис. 3.4 показаны линии связи длины вокруг одного ПЛБ. ÌÏ ÌÏ F4 C4 G1 C1 K F1 X G4 YQ ÏËÁ XQ F2 C2 ÌÏ единичной Y G3 C3 F3 G2 ÌÏ Рис. 3.4 Линии одиночной длины Каждая матрица переключений состоит из программируемых n-канальных проходных транзисторов, используемых для установления связей между линиями единичной длины. Например, сигнал, поступающий с правой стороны матрицы переключений, может быть соединен с линией единичной длины сверху, слева или снизу, или возможна любая их комбинация, если требуется множество ответвлений. Линии единичной длины обычно используются для передачи сигналов в пределах ограниченной области и обеспечения ветвления для сетей с нагрузочной способностью по выходу, превышающей единицу. Генератор функции и входы управления ПЛБ (F1...F4, G1...G4 и C1...C4) могут управляться от любого смежного сегмента линий единичной длины. Вход синхронизации ПЛБ (K) может управляться от половины смежных линий единичной длины. Каждый выход ПЛБ может управлять рядом линий единичной длины, имеющих возможность соединения как с горизонтальными, так и с вертикальными длинными линиями. Линии двойной длины состоят из сетки металлических сегментов (рис. 3.5), имеющих удвоеннную длину по сравнению с ÏËÁ ÏËÁ ÏËÁ ÏËÁ Ìàòðèöû êëþ÷åé Рис. 3.5 Линии двойной длины линиями одиночной длины. Линия двойной длины проходит два ПЛБ, прежде чем попасть в матрицу переключателей. Как и в случае с линиями единичной длины, все входы ПЛБ, кроме K, могут управляться от любой соседней линии двойной длины, и каждый выход ПЛБ может управлять ближайшими линиями двойной длины в вертикальных и горизонтальных плоскостях. Линии двойной длины обеспечивают наиболее эффективную реализацию взаимосоединений между точками промежуточной длины. Длинные линии формируют сетку металлических сегментов, которые проходят по всей длине или ширине матрицы (рис. 3.6). F4 C4 G4 YQ G1 C1 K F1 X ÏËÁ Y G3 C3 F3 XQ F2 C2 G2 Рис. 3.6 Длинные линии Кроме того, вертикальные длинные линии могут управляться специальными глобальными буферами, разработаными для распределения синхроимпульсов и других сигналов управления с большим коэффициентом разветвления по всей матрице с минимальным сдвигом фазы. Длинные линии предназначены для сигнальных сетей с высоким коэффициентом разветвления по выходу и критичных по времени. Каждая длинная линия имеет в центре программируемый расщепляющий переключатель, который может разделить линию на два независимых канала проведения соединения, каждый из которых проходит половину ширины или высоты матрицы. Входы ПЛБ могут управляться от подмножества смежных длинных линий. Выходы ПЛБ соединяются с длинными линиями через трехстабильные буфера или линии внутренней связи единичной длины. Связь между длинными линиями и линиями единичной длины управляется программируемыми пунктами связи в пересечениях линий. Линии двойной длины не соединяются с другими линиями. Программируемые пользователем БВВ (рис. 3.7) обеспечивают интерфейс между внешними контактами корпуса и внутренней логикой. Каждый БВВ управляет одним контактом корпуса и может быть определен для входных, выходных или двунаправленных сигналов. Сигналы с внешнего контакта I/O поступают в ПЛИС с выходов БВВ I1 и I2. Входы соединены с входным триггером T2, который может быть запрограммирован или как запускаемый фронтом сигнала триггер, или как одноступенчатый триггер типа "защелка". Дополнительно входные данные триггера могут быть задержаны на несколько наносекунд для компенсации задержки сигнала синхронизации, который должен сначала пройти через глобальный буфер перед достижением БВВ. Это устраняет требование к времени задержки данных на внешнем контакте. Каждый из сигналов I1 и I2, выходящих из блока, может быть либо прямым сигналом, либо сигналом с триггера T2. Выходные сигналы могут инвертироваться и могут проходить непосредственно на выходной контакт или записываться в триггер T1. Как вариант, может использоваться сигнал разрешения вывода для переключения выходного буфера в состояние высокого импеданса, осуществляющий вывод с тремя состояниями или двунаправленный входвыход. Выходные сигналы OUT и сигналы разрешения вывода (OE) могут быть проинвертированы, скорость нарастания напряжения выходного буфера может быть уменьшена для минимизации мощности импульсных помех шины питания при переключении некритических сигналов. Выходной ток буфера семейства XC4000 составляет 12 mA; два смежных выхода буферов могут быть объединены внешним проводником, образуя монтажное И, что увеличивает выходной ток до 24 mA. В семействах XC4000A и XC4000H, каждый выходной буфер обеспечивает выходной ток 24 mA. Óïðàâëåíèå âûõîäîì OE Óïðàâëåíèå Vcc êîíòàêòîì K1 K7 OUT K2 D Q Âûõîäíîé áóôåð T1 C1 I/O K3 I1 K4 I2 Âõîäíîé áóôåð K5 Q D K8 D T2 C2 K6 Рис. 3.7 Блок ввода-вывода Имеется ряд других программируемых возможностей в БВВ. Программируемость резисторов, подключаемых к источнику питания и к корпусу, полезна для соединения неиспользованных контактов с питанием или землей для минимизации потребления энергии. Отдельные сигналы синхронизации предусматриваются для выходных и входных триггеров. Эти синхросигналы могут быть проинвертированы, сгенерированы для переключения триггеров по переднему, либо заднему фронтам. Как и в случае с триггерами ПЛБ, глобальный сигнал установки-сброса (на рис. 3.7 не показан) может использоваться для установки или очистки входных и выходных регистров всякий раз, когда активизируется сеть RESET. 3.4. Организация памяти Устройства семейств XC4000, XC4000A и XC4000H являются программируемыми логическими устройствами с возможностью реализации ОЗУ, доступного пользователю с организацией 16 x 2 или 32 x 1 типа SRAM (Рис. 3.8). Входы F1...F4 и G1...G4 генераторов функции действуют как адресные линии, выбирающие определенную ячейку памяти. Функциональное назначение управляющих сигналов ПЛБ изменяется в этой C1 C2 H1 DIN C3 C4 S/R EC & G4 G3 G2 G1 W E DATA IN G’ LF1 WRITE G’ WRITE F’ & M 16x2 MS F4 F3 F2 F1 W E DATA IN F’ LF2 Рис. 3.8 Организация ЗУ на базе ПЛБ конфигурации: входы DIN, S/R и H1 станут двумя входами данных D0 и D1 и входом разрешения записи WE при организации памяти 16 x 2. При организации 32 x 1 вход D1 действует как пятый бит адреса, и DO - как вход данных. Содержимое адресованной ячейки памяти доступно на выходах F и G генераторов функций и может быть выведено из ПЛБ через выходы X и Y. Возможно также использование триггеров ПЛБ для выдачи информации. Программирование генераторов функции ПЛБ как памяти не затрагивает функциональных возможностей других частей ПЛБ, за исключением переопределенных сигналов управления. Генератор функций H может использоваться для реализации булевых функций над F', G' и D1, а триггеры D могут хранить F', G', H' или D0-сигналы. Время доступа чтения ОЗУ такое же, как задержка логического элемента - приблизительно 5.5 нс; время записи равно приблизительно 8 нс; в обоих случаях время доступа в несколько раз быстрее, чем при использовании любого внешнего кристалла. Такая реализация распределенного ОЗУ - это новая концепция, создающая дополнительные возможности при проектировании системы, включающей регистровые матрицы множества сумматоров, регистры состояний, регистры индекса, счетчики DMA, распределенные регистры сдвига, стеки LIFO и буфера FIFO. Информационный канал FIFO на 16 байт использует четыре ПЛБ для хранения и шесть ПЛБ для подсчета адреса и мультиплексирования (Рис. 3.9). При 32 ячейках хранения на ×òåíèå Ñ÷åò÷èê çàïèñè Ñ÷åò÷èê ÷òåíèÿ 2CLBs Çàïèñü 2CLBs 4 4 8 8 8 Óïðàâë. 2CLBs FULL EMPTY Âõîäíûå äàííûå WE 4CLBs Âûõîäíûå äàííûå ÎÇÓ 16x8 Рис. 3.9 Запоминающее устройство типа FIFO ПЛБ, в сравнении с двумя триггерами на ПЛБ, стоимость распределенной памяти сокращена в 16 раз. При использовании устройств XC4000 проектировщик может проектировать узлы, в которых сохраняется содержание конфигурации функциональных генераторов. Каждый функциональный генератор может использоваться как маленькая память типа ОЗУ. Функциональные генераторы в любом ПЛБ могут быть конфигурированы тремя путями. 1. Два 16 x 1 RAM с двумя входами данных и двумя выходами данных с одинаковой или, если это предпочтительнее, разной адресацией для каждого RAM. 2. Один 32 x 1 RAM с одним входом данных и одним выходом данных. 3. Один 16 x 1 RAM плюс один генератор функции с пятью входами. 3.5. Системы проектирования Для проектирования цифровых устройств на ППВМ семейства XC4000 применяются мощные и удобные средства разработки. Фирма Xilinx обеспечивает достаточно мощную версию инструментальных средств Xilinx Automatic CAE (XACT). Процесс проектирования состоит из трех этапов: ввода проекта, выполнения проекта и верификации проекта. Ввод проекта Проект может быть введен с использованием программного обеспечения схемотехнического уровня, описания конечного автомата или ввода булевых уравнений. Фирма Xilinx совместно с другими фирмами разработали библиотеку и интерфейсные продукты, совместимые с большим разнообразием сред моделирования и ввода проекта. Стандартная спецификация файла взаимообмена XNF обеспечивает упрощение преобразования входных и выходных файлов системы разработки XACT. Xilinx предлагает взаимообмен системы разработки XACT со следующими средами проектирования: OrCAD, Viewlogic Viewdraw and Viewsim, Mentor Graphics V7 and V8 и др. Несколько сред разработки поддерживаются другими фирмами. В настоящее время применяется более чем 100 пакетов. Наряду со стандартной библиотекой макрокоманд программных средств (Soft Macros), семейство XC4000 также включает в себя библиотеку Hard Macros. Библиотека Soft Macros содержит детальные описания общих логических функций типа счетчиков, сумматоров, и т.д.; она не содержит информацию о разбиении или проведении соединений. Эффективность Soft Macros зависит поэтому от того, как программное обеспечение обрабатывает макрокоманду. Библиотека Hard Macros содержит полную информацию о разделении, размещении и проведении соединений. Эти предварительно определенные и оттестированные функции позволяют пользователю создавать критичные по времени проекты с оптимизированными характеристиками. Проектирование с Hard Macros осуществляется достаточно просто. В состав библиотеки Soft Macros входят следующие компоненты: 11 вентилей, 43 триггера, 7 буферов, 8 сумматоров-вычитателей, 13 компараторов, 23 мультиплексора, 16 декодеров, 2 устройства кодирования по четности, 16 регистров данных, 26 регистров сдвига, 3 типа ОЗУ, 2 типа ПЗУ, 59 счетчиков и др. В состав библиотеки Hard Macros входят следующие компоненты: 2 cумматора, 2 аккумулятора, 4 компаратора, 3 мультиплексора, 4 декодера и др. Выполнение проекта Инструментальные средства выполнения проекта обеспечивают разработку схем с высокой плотностью, в том числе устройств XC4000, и позволяют полностью автоматизировать процесс проектирования, включая этапы разбиения логической схемы, размещения блока и трассировки сигналов. Компонента разбиения инструментальных средств принимает логическую схему со схемотехнического уровня и делит логическую схему так, чтобы она могла быть реализована на блоках, имеющихся в устройстве. Компонента размещения определяет наилучшие местоположения блоков в зависимости от их связанности и требуемых характеристик, а компонента трассировки соединяет размещенные блоки друг с другом. Улучшенные алгоритмы размещения и проведения соединений обеспечивают полностью автоматическое исполнение наибольшего количества проектов. Новые алгоритмы также сокращают время выполнения по сравнению с предыдущими поколениями программного обеспечения. Автоматизированные инструментальные средства дополняет диалоговый графический редактор XACT Design Editor (XDE), который показывает модель фактической логической схемы и ресурсов проведения соединений ППВМ. XDE может использоваться для непосредственного просмотра результатов, полученных автоматизированными инструментальными средствами. Используя XDE, можно осуществить необходимые модификации; XDE может также выполнить проверку логических связей и возможных нарушений правил проектирования. Пошаговые вычисления с временными задержками обеспечивают временной анализ и помогают определить критические направления. Верификация проекта Высокая стоимость разработки требует тщательного моделирования для верификации проекта. Из-за специфики базовых матричных кристаллов (БМК) и вентильных матриц (ВМ) изменения проекта в последнюю минуту недопустимы. Проектировщик, использующий вентильные матрицы и БМК, должен с помощью моделирования проверить всю логическую схему и временную диаграмму ее работы при самых плохих ситуациях. Процесс моделирования весьма трудоемкий и длительный: моделирование нескольких секунд работы системы может потребовать неделю работы проектировщика. Пользователи программируемых вентильных матриц могут применять аппаратные средства отладочных схем в дополнение к моделированию. Так как устройства Xilinx перепрограммируемы, проекты могут быть верифицированы в системе в режиме реального времени. Система разработки XACT поддерживает и моделирование, и аппаратные средства отладочных схем. Для моделирования система извлекает информацию о временной диаграмме функционирования разведенной схемы из базы данных проекта. Эти данные можно затем послать на моделирование для верификации критичных по времени частей проекта. Для внутрисхемной отладки XACT имеет ряд загрузочных и считывающих кабелей (XChecker), с помощью которых устройство подсоединяется к ПЭВМ или рабочей станцией через последовательный порт RS-232С. Разработчик может загрузить проект или пересмотренный проект в систему при испытаниях. Проектировщик может также исполнять логическую схему в пошаговом режиме, читать содержимое многочисленных триггеров устройства и наблюдать уровни внутренних логических схем. Простые модификации можно загрузить в систему в течение нескольких минут. 3.6. Программирование микросхем Программирование микросхем - это процесс загрузки данных конкретного проекта в одно или несколько устройств ППВМ для задания конфигурации внутренних блоков и их взаимных соединений. Эта операция подобна загрузке командных регистров программируемого периферийного кристалла. Семейства XC4000 используют приблизительно 350 бит данных конфигурации для ПЛБ и на соответствующие им взаимосвязи. Каждый бит конфигурации определяет состояние статической ячейки памяти, которая управляет или битом таблицы задания функции, или входом мультиплексора, или проходным транзистором связи. Система разработки XACT переводит проект в файл сетевого списка. Она автоматически разделяет, размещает логическую схему, проводит ее соединения и генерирует данные конфигурации в формате ПЗУ. Семейства XC4000 имеют шесть режимов программирования, выбираемых трехразрядным входным кодом, поступающим на входы M0, M1 и M2. Имеются три самозагружаемых режима Master, два периферийных режима (Peripheral) и последовательный ведомый режим (Serial Slave), используемый прежде всего для цепочечной организации устройств. В течение программирования некоторые из контактов вводавывода временно используются для процесса программирования. В режимах Master используется внутренний генератор для генерирования сигнала CCLK с целью управления ведомыми устройствами и генерирования адреса и синхронизации для внешнего ПЗУ, содержащего данные конфигурации. В режиме параллельный ведущий (Master Parallel) генерируются сигнал CCLK и адреса ПЗУ и принимаются байты данных, которые внутри схемы преобразуются в последовательную форму в формате структуры данных ППВМ. В двух периферийных режимах принимаются данные шириной один байт из шины. Имеется состояние READY-BUSY (ГОТОВО-ЗАНЯТО) как сигнал квитирования установления связи. В асинхронном режиме внутренний генератор генерирует сигнал пакетной разбивки CCLK, который преобразует в последовательную форму данные шириной байт. В синхронном режиме синхронизация от внешнего источника, подаваемая на вход CCLK, преобразует данные в последовательную форму. В режиме Serial Slave (последовательный ведомый) устройство ППВМ получает последовательные данные конфигурации относительно переднего фронта CCLK и после загрузки конфигурации выдает дополнительные данные, повторно синхронизированные по следующему заднему фронту CCLK. Несколько ведомых устройств с идентичными конфигурациями могут быть монтажно соединены с параллельными входами DIN и запрограммированы одновременно. Поток данных конфигурации начинается строкой единиц, кодом начала 0010, 24-битным счетчиком длины и четырехразрядным разделительным полем единиц. Далее следуют фактические данные конфигурации в структурах, каждая из которых начинается нулевым битом и оканчивается контролем ошибки с четырьмя битами. При проверке ошибки CRC программное обеспечение вычисляет текущий CRC или вставляет уникальный частичный 4-битный контроль в конце каждой структуры. Когда питание подключается к устройству ППВМ, внутренняя цепь вызывает инициализацию логической схемы конфигурации. После того, как все структуры конфигурации загружены в устройство ППВМ, DOUT повторяет входные данные для передачи оставшихся данных на следующее устройство. 4. ПРИМЕРЫ ПРОЕКТИРОВАНИЯ СХЕМ НА ПЛИС 4.1. Проектирование типовых узлов Рассмотрим проектирование простейшей триггерной схемы, приведенной на рис 4.1, с помощью системы проектирования PLDshell. Схема занимает две триггерные ячейки QA и QB, при этом выход 1 триггера QA на контакт не выводится, однако он используется для задания функции для 2 триггера QB. OE=0 IN1 D CLK C QA IN3 (PIN FEEDBACK) QA D Äâîéíàÿ IN3 Q Q QB OE=VCC QB C îáðàòíàÿ ñâÿçü Рис. 4.1 Триггерная схема Описание этой схемы будет следующим: CHIP MOD INTEL_ARCH ; определение ПЛИС PIN 15 QA ; описание контактов PIN 15 IN3 EQUATIONS QA.D:=IN1 ; описание 1 триггера QA QA.TRST=GND QA.CLKF=CLK QB.D:=QA*IN3 ; описание 2 триггера QB QB.TRST=VCC Необходимо отметить, что в приведенном выше примере тип триггера жестко задается пользователем в программе. Рассмотрим описание схемы сложения по модулю 2 двух двухразрядных чисел a1,a2 и b1,b2. Результатом является двухразрядное число cmp1,cmp2. Описание схемы сложения по модулю 2 будет следующим: DEFMOD 2_bit_compare (a1,a2,,cmp1,cmp2) ; заголовок CHIP MOD INTEL_ARCH ; пределение ПЛИС PIN a1 ; описание контактов PIN a2 PIN b1 PIN b2 PIN cmp1 PIN cmp2 ; задание выполняемой функции MODULE 2_bit_xor FILE 2bxor (in1=A1, in2=B1, out=CMP1) MODULE 2_bit_xor FILE 2bxor (in1=A2, in2=B2, out=CMP2) ENDMOD Данный пример содержит только комбинационные элементы и не использует триггерные схемы. 4.2 Проектирование пересчетных схем Рассмотрим проектирование реверсивного счетчика, который увеличивает свое состояние при воздействии сигнала UPDOWN=1 и уменьшает свое состояние при UPDOWN=0, сброс производится сигналом CLEAR. Работа счетчика может быть представлена в виде цифрового автомата, изображенного на рис. 4.2. На этом рисунке не показан сброс счетчика. S2 DOWN DOWN UP UP S1 S3 UP DOWN UP DOWN S4 Рис. 4.2 Граф переходов реверсивного счетчика Заголовок исходного файла может быть определен следующим образом: Title 2-Bit Counter Sample File ; заголовок Pattern pds Revision 1 Author IVANOW Company PGTU Date Date ; текущая дата) Описание контактов имеет следующий вид: PIN 1 CLK ; синхронизация PIN 2 UPDOWN ; управление PIN 3 CLEAR ; сброс PIN 12 Q1 PIN 13 Q0 Описание состояний автомата: STATE MOORE_MACHINE DEFAULT_BRANCH S1 S1 = /Q1 * /Q0 ; S1 = 00 - состояние 0 S2 = /Q1 * Q0 ; S2 = 01 - состояние 1 S3 = Q1 * /Q0 ; S3 = 10 - состояние 2 S4 = Q1 * Q0 ; S4 = 11 - состояние 3 Описание переходов: S1 := UP -> S2 + DOWN -> S4 S2 := UP -> S3 + DOWN -> S1 S3 := UP -> S4 + DOWN -> S2 S4 := UP -> S1 + DOWN -> S3 Описание условий: CONDITIONS UP = UPDOWN * /CLEAR ; сложение, если UPDOWN=1 и CLEAR=0 DOWN = /UPDOWN * /CLEAR ; вычитание, если UPDOWN=CLEAR=0 Во время трансляции система сама установит функции возбуждения для триггеров Q0 и Q1 в соответствии с заданными выше условиями. Эти функции можно посмотреть в файле с расширением RPT, который генерируется системой. Для данного автомата функции возбуждения будут иметь следующий вид: Q1.D := /Q1 * Q0 * UPDOWN*/CLEAR + Q1 * Q0 * /UPDOWN*/CLEAR + /Q1 * /Q0 * /UPDOWN*/CLEAR + Q1 * /Q0 * UPDOWN*/CLEAR Q0.D := /Q0 * /CLEAR Задание временных диаграмм: SIMULATION TRACE_ON UPDOWN CLEAR CLK Q1 Q0 SETF UPDOWN /CLEAR /CLK PRLDF /Q1 /Q0 FOR j := 0 TO 5 DO ; шесть тактов счета на сложение BEGIN CLOCKF CLK END SETF CLEAR ; очистка счетчика CLOCKF CLK SETF /CLEAR SETF /UPDOWN FOR j := 0 TO 5 DO ; шесть тактов счета на вычитание BEGIN CLOCKF CLK END Временные диаграммы работы счетчика приведены на рис. 4.3. Рассмотрим проектирование четурехразрядного счетчика, работающего только на сложение при действии разрешающего сигнала ENA=1. Работа счетчика задается с помощью уравнений алгебры логики. Для моделирования устанавливаетя следующий режим работы: Четыре такта счетчик работает на сложение, четыре такта - ожидание, а затем счетчик снова работает на сложение. Рис. 4.3 Временные диаграммы работы реверсивного счетчика Заголовок исходного файла может быть определен следующим Title 4-Bit Counter Sample File ; заголовок Pattern pds Revision 1 Author IVANOW Company PGTU Date Date ; текущая дата) CHIP 4_count 85С220 Описание контактов имеет следующий вид: PIN CLK ; сигнал синхронизации PIN ENA ; разрешение счета PIN QA ; старший разряд счетчика PIN QB PIN QC PIN QD ; младший разряд счетчика Задание уравнений: EQUATIONS QA := ENA * /QA QB := ENA * QB * /QA + ENA * /QB * QA QC := ENA * QC * /QA + ENA * QC * /QB + ENA * /QC * QB * QA QD := ENA * QD * /QA + ENA * QD * /QB + ENA * QD * /QC + ENA * /QD * QC * QB * QA EQUATIONS QA.CLKF = CLK ; задание сигналов синхронизации QB.CLKF = CLK QC.CLKF = CLK QD.CLKF = CLK Моделирование: SIMULATION VECTOR COUNT := [ QD, QC, QB, QA ] ; задание вектора TRACE_ON ENA CLK QD QC QB QA SETF ENA /CLK PRLDF /QA /QB /QC /QD ; сброс счетчика в ноль FOR X := 0 TO 3 DO ; четыре такта работы на сложение BEGIN CLOCKF CLK END SETF /ENA FOR X:=0 TO 3 DO ; четыре такта ожидание BEGIN CLOCKF CLK END SETF ENA FOR X:=0 TO 9 DO ; десять тактов работы на сложение BEGIN CLOCKF CLK END TRACE_OFF Временные диаграммы работы счетчика приведены на рис. 4-4. Рассмотрим проектирование 8-разрядного счетчика. Счетчик является реверсивным, управление его осуществляется сигналом UD, если UD=0, то производится счет на сложение. Рис. 4.4 Временные диаграммы работы четырехразрядного счетчика Разрешение работы осуществляется сигналом RS, если RS=1 то разрешается счет. Заголовок исходного файла может быть определен следующим образом: TITLE 8-bit Counter Using Toggle Flip-Flops Pattern pds Revision 1 Author IVANOW Company PGTU Date Date ; текущая дата) CHIP 8bit_counter 85C090 Описание контактов имеет следующий вид: PIN RS ; управление (0 ==> запрет, 1 ==> счет) PIN RESET ; сброс нулем PIN UD ; UP/DOWN (0 ==> счет на сложение) PIN CLK ; Синхронизация PIN Q7 ; старший разряд счетчика PIN Q6 .... ; задание разрядов с 5 по 2 PIN PIN Q1 Q0 ; младший разряд счетчика ; определение функций с помощью строк Q0U '(UD * RS)' ; описание фунций Q1U '(UD * Q0 * Q0U)' ; возбуждения Q2U '(UD * Q1 * Q1U)' ; триггеров при Q3U '(UD * Q2 * Q2U)' ; работе счетчика Q4U '(UD * Q3 * Q3U)' ; на сложение Q5U '(UD * Q4 * Q4U)' Q6U '(UD * Q5 * Q5U)' Q7U '(UD * Q6 * Q6U)' Q0D '(/UD * RS)' ; описание фунций Q1D '(/UD * /Q0 * Q0D)' ; возбуждения Q2D '(/UD * /Q1 * Q1D)' ; триггеров при Q3D '(/UD * /Q2 * Q2D)' ; работе счетчика Q4D '(/UD * /Q3 * Q3D)' ; на вычитание Q5D '(/UD * /Q4 * Q4D)' Q6D '(/UD * /Q5 * Q5D)' Q7D '(/UD * /Q6 * Q6D)' STRING STRING STRING STRING STRING STRING STRING STRING STRING STRING STRING STRING STRING STRING STRING STRING Уравнения EQUATIONS Q0.T := Q0U + Q0D ; при записи уравнений используются Q1.T := Q1U + Q1D ; введенные выше строки Q2.T := Q2U + Q2D ; тип триггеров задается Q3.T := Q3U + Q3D ; данными описаниями Q4.T := Q4U + Q4D Q5.T := Q5U + Q5D Q6.T := Q6U + Q6D Q7.T := Q7U + Q7D Во время трансляции система установит функции возбуждения для триггеров Q7 ... Q0 в соответствии с заданными выше уравнениями. Для данного счетчика функции возбуждения будут иметь следующий вид: Q0.T := RS Q1.T := UD * Q0 * RS + /UD * /Q0 * RS Q2.T := UD * Q1 * Q0 * RS + /UD * /Q1 * /Q0 * RS Q3.T := UD * Q2 * Q1 * Q0 * RS + /UD * /Q2 * /Q1 * /Q0 * RS Q4.T := UD * Q3 * Q2 * Q1 * Q0 * RS + /UD * /Q3 * /Q2 * /Q1 * /Q0 * RS Q5.T := UD * Q4 * Q3 * Q2 * Q1 * Q0 * RS + /UD*/Q4*/Q3*/Q2*/Q1*/Q0*RS Q6.T := UD * Q5 * Q4 * Q3 * Q2 * Q1 * Q0 * RS + /UD*/Q5*/Q4*/Q3*/Q2*/Q1*/Q0*RS Q7.T := UD * Q6 * Q5 * Q4 * Q3 * Q2 * Q1 * Q0 * RS + UD*/Q6*/Q5*/Q4*/Q3*/Q2*/Q1*/Q0*RS Приведенные выше уравнения зафиксированы в файле с расширением RPT. Q0.CLKF = CLK ; задание синхронизации счетчика ...... ; задание синхронизации для Q1 ... Q6 Q7.CLKF = CLK Q0.RSTF = RESET ; задание асинхронного сброса ...... ; задание асинхронного сброса для Q1 ... Q6 Q7.RSTF = RESET SIMULATION VECTOR V := [ Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0 ] SETF RESET RS /CLK UD SETF /RESET ; окончание сигнала сброса FOR I := 0 TO 38 DO ; начало работы BEGIN CLOCKF CLK IF ( (I > 4) * (I < 11) ) THEN BEGIN ; остановка работы счетчика между SETF /RS ; шестым и двенадцатым синхросигналами END IF ( I = 11 ) THEN BEGIN SETF RS ; продолжение счета END END На рис. 4.5 приведены временные диаграммы работы счетчика на начальном этапе. Рис. 4.5 Временные диаграммы работы 8-разрядного счетчика (начальный этап) ЛИТЕРАТУРА 1. Цифровые интегральные микросхемы /П.П.Мальцев, Н.С.Долидзе и др. - М.:Радио и связь. 1994 - 240 с. 2. Берски Д. Соперничество высокой плотности с вентильными матрицами. Электроника. - 1991. - № 5. - C. 15 - 27. 3. Берски Д. Быстродействующие ППВМ - кристаллы с повышенной плотностью упаковки. // Электроника. - 1993. - .№ 18. - С. 44 - 57. 4. Забара С.С. и др. Проектирование логических схем нейрокомпьютера в элементном базисе ПЛИС XC2000. //Управляющие системы и машины. 1993. - № 1. - С. 9 - 15. 5. Беpезнев А.Г. САПP ПЛИС фиpмы XILINX. // Мир ПК. - 1994. - .№4. С. 54-58. 6. Support all Intel PLDs and FLEXlogic FPGA. PLDshell Plus/PLDasm. User Guide v3.1, 1993. 7. XILINX. The Programmable Logic Data Book. - San Jose, California. 1993. - P.374. 8. Tuck B. FPGAs race for the gold in product development // Comput. Des. 1992. Vol. 31, N 4. -P. 88-90, 92, 96, 98-100, 102, 104. 9. Bursky D. Denser, faster FPGAs vie for gate-array applications // Electron. Des. -1993. -41,N11. -С. 55-56, 62-64, 68-71, 74-75. ПРИЛОЖЕНИЕ 1 СПРАВОЧНЫЕ ДАННЫЕ ПО ЯЯЗЫКУ PLDASM Заголовок исходного файла Title PLDasm Language Summary Pattern <pattern label> Revision <rev. number> Author <your name> Company <your company> Date <current date> Определения DEFMOD <module name> ( <argument list> ) CHIP <module name> INTEL_ARCH PIN <argument list name> NODE <any buried pin> Режимы OPTIONS TURBO = [ON|OFF] ; default is ON SECURITY = [ON|OFF] ; default is OFF DRIVE_LEVEL = [5VOLT|3VOLT] ; default is 5VOLT outputs Тип используемой микросхемы Корпус Тип Быстродействие 20 pin C/PDIP 85C220 -80(10ns Tpd), -66(12ns Tpd) C/PDIP 5C032 -30, -35, -40 24/28 pin C/PDIP PLD22V10 -10, -15 C/PDIP PLD610 -10, -15, -25 C/PDIP 85C224 -80(10ns Tpd), -66(12ns Tpd) C/PDIP 5AC312 -25, -30 C/PDIP 85C22V10 -10, -15 C/PDIP 5C060 -45, -55 28 pin C/PDIP 85C508 -7, -10 PLCC N85C508 -7, -10 40/44 pin C/PDIP PLD910 -12, -15, -20, -25 C/PDIP 5AC324 -25, -30, -35 C/PDIP 5C090 -50, -60 PLCC 44 pin PLCC 68 pin PLCC 84 pin PLCC 132 pin PQFP N5C090 -50, -60 FX740_44 -10, -15 FX740_68 -10, -15 FX7840_84 -10, -15 FX780_132 -10, -15 Описание контактов PINLIST PIN 1 CLOCK PIN 1 DCLOCK DELAYCLK ; задержанная синхронизация PIN UPDOWN ; неопределенный контакт PIN /CLEAR ; активный низкий уровень PIN 2 I1 PIN 5 I4 PIN [2:5] I[1:4] ; векторная нотация PIN [0:3] D[0:3] ; NODE 32 Q0 ; скрытый контакт NODE Q1 ; PIN O1 COMB PINFBK ; комбинационный выход, контакт в обратную связь PIN O2 COMB CMBFBK 5VOLT ; комбинационный выход, выход 5VOLT PIN O3 COMB REGFBK ; комбинационный выход, регистр ОС (только 85C22V10, FX7xx ) NODE O4 CMBFBK BURIED ; скрытая ячейка PIN O5 REG PINFBK 3VOLT ; регистровый выход, выход 3.3 VOLT PIN O6 REG REGFBK ; регистровый выход, PIN O7 REGFBK BURIED ; скрытый регистр PIN cout_t JKFBK ; JK триггер PIN tout CMBFBK ; T триггер PIN BUFRAM[0:9] RAM ; комбинационный выход ОЗУ NODE ROMTAB[8:0] RAM ; скрытый комбинационный выход ОЗУ Ключевые слова [ STATE ], [ EQUATIONS ], [ T_TAB ], [ MODULE ], [ RAM_DEFAULTS ], [ SIMULATION ]. Использование цифровых автоматов STATE [MEALY_MACHINE|MOORE_MACHINE] ; автомат Милли 1 0 OUTPUT_HOLD OUT1 /OUT2 0 1 X DEFAULT_OUTPUT /OUT1 OUT2 %OUT3 Задание состояний по умолчанию: DEFAULT_BRANCH S0 ; переход к S0 DEFAULT_BRANCH HOLD_STATE ; переход в текущее состояние DEFAULT_BRANCH NEXT_STATE ; переход к следующему состоянию Описание состояний: S0 = /Q1 * /Q0 S1 = /Q1 * Q0 S2 = Q1 * Q0 S3 = Q1 * /Q0 Описание переходов S0 := VCC -> S1 ; переход к S1 S1 := UP -> S2 + DOWN -> S4 Выходы автомата Милли: S1.OUTF := DOWN -> LOCAL * /MEMORY * /INTACK + UP -> /LOCAL S2.OUTF = UP -> ASTRB S3.OUTF = VCC -> ASTRB CONDITIONS UP = UPDOWN * /CLEAR DOWN = /UPDOWN * /CLEAR ACTIVE = /EN + RDY Уравнения EQUATIONS O1 = ... ; комбинационный выход (COMBINATORIAL) O1 := ... ; регистровый (D) выход (REGISTERED) O1.FB ; обратная связь из ячейки (REGFBK, CMBFBK) O1.D := ... ; регистровый (D) выход (REGISTERED) O1.T := ... ; триггерный (T) выход O1.J := ... ; выход JK триггера O1.K := ... ; выход JK триггера Сигналы управления O1.CLKF = CLOCK ; синхросигнал O1.ACLK = CLOCK * ENABLE ; O1.RSTF = CLEAR ; сброс O1.SETF = PRESET ; установка O1.TRST = /OE ; разрешение AND1 = IN1 * IN2 ; логическое И /NAND1 = IN1 * IN2 ; логическое И-НЕ OR1 = IN1 + IN2 ; логическое ИЛИ /NOR1 = IN1 + IN2 ; логическое ИЛИ-НЕ XOR1 = IN1 :+: IN2 ; сложение по модулю 2 /XOR1 = IN1 :+: IN2 ; сложение по модулю 2 с инверсией NOT = /IN1 ; инверсия SOP = /(IN1 + IN2) * IN3 + (IN4 :+: IN5) * /IN6 ОЗУ Определение PIN BUFRAM[0:9] RAM BUFRAM BUFRAM[0:6].ADDR = <addr6, addr5, ...,addr0> BUFRAM[0:9].DATA = <data9, data8, ...,data0> /BUFRAM[0:9].TRST = oe /BUFRAM.BE = ce /BUFRAM.WE = we Табличное задание ( I1 I2 I3 I4 >> C1 C2 C3 C4 ) 1 0 0 0 : 1 0 0 0 0 1 0 0 : 0 1 0 0 0 0 1 0 : 0 0 1 0 0 0 0 1 : 0 0 0 1 Моделирование SIMULATION VECTOR INS := [ IN8,IN7,IN6,IN5,IN4,IN3,IN2,IN1,IN0 ] VECTOR NUM := [ Q3, Q2, Q1, Q0 ] VECTOR GLOB := [ ADDR23, ADDR22, ADDR16, ADDR12] SETF /CLKPIN /ILE I1 /I2 /I3 INS:=#o377 PRLDF /Q0 /Q1 /Q2 /Q3 CLOCKF CLKPIN FOR j := 0 TO 5 DO ; оператор цикла BEGIN SETF INS := j CLOCKF CLK IF ( NUM == 4 ) ; когда состояние равно 4 BEGIN SETF /OE ; запрещеие OE END END WHILE ( OUTA + OUTB ) DO BEGIN CLOCKF ACLK1 END ПРИЛОЖЕНИЕ 2 СОДЕРЖИМОЕ ФАЙЛА RPT Файл RPT создается в результате работы программы PLDshell и содержит результаты трансляции и данные, необходимые для загрузки в микросхему. Заголовок INTEL Logic Optimizing Compiler Utilization Report 2BIT.rpt FIT Release [ 3.1 ] SID [ 2.364 ] ***** Design implemented successfully Заголовок исходного файла TITLE 2-BIT COUNTER SAMPLE FILE PATTERN PDS REVISION 1 AUTHOR YOUR NAME COMPANY YOUR COMPANY DATE DATE Описание контактов OPTIONS TURBO = ON SECURITY = OFF CHIP 2_BIT_COUNT 85C220 PIN 1 CLK PIN 2 UPDOWN PIN 3 CLEAR PIN [12:13] Q[1:0] Уравнения EQUATIONS Q1.D := /Q1 * Q0 * UPDOWN * /CLEAR + Q1 * Q0 * /UPDOWN * /CLEAR Q1.CLKF = CLK Q1.RSTF = GND Q1.SETF = GND Q1.TRST = VCC Q0.D := /Q0 * /CLEAR Q0.CLKF = CLK Q0.RSTF = GND Q0.SETF = GND Q0.TRST = VCC Данные по моделированию SIMULATION TRACE_ON UPDOWN CLEAR CLK Q1 Q0 SETF UPDOWN /CLEAR /CLK PRLDF /Q1 /Q0 FOR J := 0 TO 5 DO BEGIN CLOCKF CLK END SETF CLEAR CLOCKF CLK SETF /CLEAR SETF /UPDOWN FOR J := 0 TO 5 DO BEGIN CLOCKF CLK END SETF CLEAR CLOCKF CLK SETF /CLEAR TRACE_OFF ***** Design implemented successfully ; Отметка об успешном окончании этапа проектирования Изображение используемой микросхемы 85C220 ----CLK -| 1 20 |Vcc UPDOWN -| 2 19 |Gnd CLEAR -| 3 18 |Gnd Gnd -| 4 17 |Gnd Gnd -| 5 16 |Gnd Gnd -| 6 15 |Gnd Gnd -| 7 14 |Gnd Gnd -| 8 13 |Q0 Gnd -| 9 12 |Q1 GND -|10 11 |Gnd ----CMOS Device: ground unused inputs and I/Os Gnd = unused input or I/O pin. RESERVED = Leave pins unconnected on board. N.C. = unconnected pins **OUTPUTS** ; выходы Использование ресурсов микросхемы Name Pin Resource MCell PTerms Q1 12 RORF 8 4/ 8 Q0 13 RORF 7 1/ 8 **INPUTS** ; входы Name Pin Resource MCell PTerms UPDOWN 2 INP CLEAR 3 INP CLK 1 INP **UNUSED RESOURCES** ; неиспользуемые ресурсы Name Pin Resource MCell PTerms - 4 INPUT - 5 INPUT - 6 INPUT - - 7 INPUT - 8 INPUT - 9 INPUT - 11 INPUT - 14 MCELL 6 8 - 15 MCELL 5 8 - 16 MCELL 4 8 - 17 MCELL 3 8 - 18 MCELL 2 8 - 19 MCELL 1 8 **PART UTILIZATION** 2/ 8 MacroCells (25%), 31% of used Pterms Filled 3/10 Input Pins (30%) PTerms Used 7% **RESOURCE MNEMONICS** INP = Pin Input to Logic Array RORF = D-Register pin Output, Register Feedback Macrocell Interconnection Cross Reference FEEDBACKS: MM 00 78 Q0 ....... RORF @M7 -> * * @13 Q1 ....... RORF @M8 -> . * @12 INPUTS: CLK ...... INP @1 -> * * UPDOWN ... INP @2 -> . * CLEAR .... INP @3 -> * * QQ 01 . = not connected x = no connection possible * = signal feeds cell ? = error, unable to fit