61-72x

advertisement

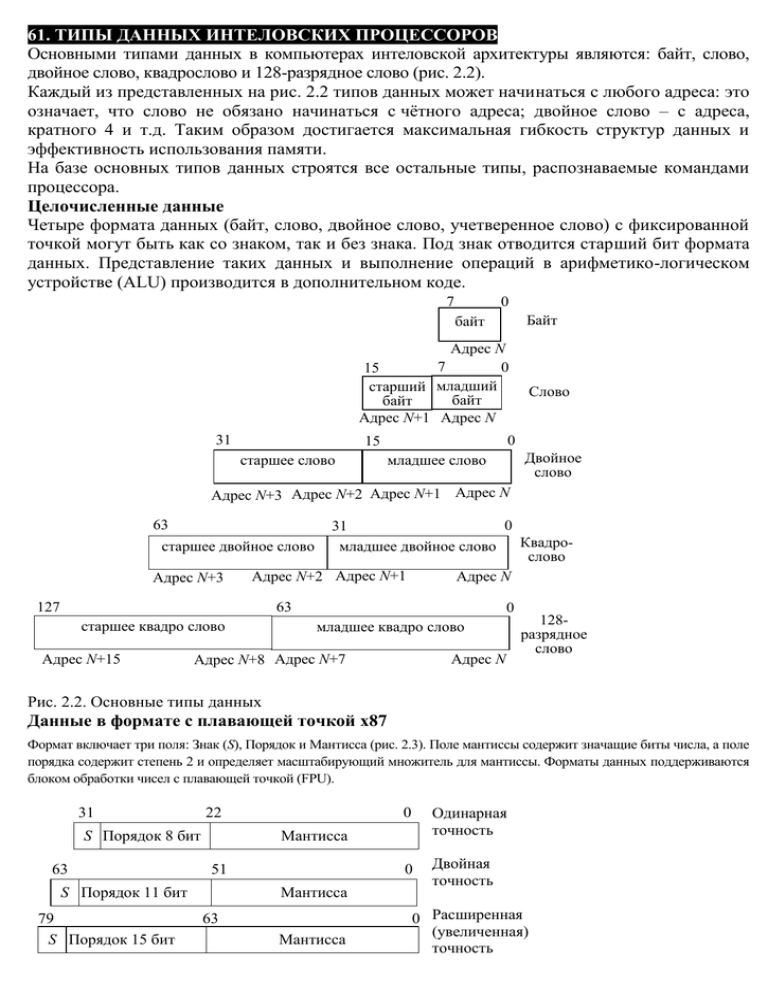

61. ТИПЫ ДАННЫХ ИНТЕЛОВСКИХ ПРОЦЕССОРОВ Основными типами данных в компьютерах интеловской архитектуры являются: байт, слово, двойное слово, квадрослово и 128-разрядное слово (рис. 2.2). Каждый из представленных на рис. 2.2 типов данных может начинаться с любого адреса: это означает, что слово не обязано начинаться с чётного адреса; двойное слово – с адреса, кратного 4 и т.д. Таким образом достигается максимальная гибкость структур данных и эффективность использования памяти. На базе основных типов данных строятся все остальные типы, распознаваемые командами процессора. Целочисленные данные Четыре формата данных (байт, слово, двойное слово, учетверенное слово) с фиксированной точкой могут быть как со знаком, так и без знака. Под знак отводится старший бит формата данных. Представление таких данных и выполнение операций в арифметико-логическом устройстве (ALU) производится в дополнительном коде. 7 0 Байт байт Адрес N 7 0 15 старший младший байт байт Адрес N+1 Адрес N 31 0 15 старшее слово Слово Двойное слово младшее слово Адрес N+3 Адрес N+2 Адрес N+1 Адрес N 63 старшее двойное слово Адрес N+3 0 31 Квадромладшее двойное слово слово Адрес N Адрес N+2 Адрес N+1 127 63 старшее квадро слово Адрес N+15 0 младшее квадро слово Адрес N+8 Адрес N+7 Адрес N 128разрядное слово Рис. 2.2. Основные типы данных Данные в формате с плавающей точкой х87 Формат включает три поля: Знак (S), Порядок и Мантисса (рис. 2.3). Поле мантиссы содержит значащие биты числа, а поле порядка содержит степень 2 и определяет масштабирующий множитель для мантиссы. Форматы данных поддерживаются блоком обработки чисел с плавающей точкой (FPU). 31 22 S Порядок 8 бит 63 Мантисса 51 S Порядок 11 бит 79 S Порядок 15 бит Одинарная точность 0 0 Мантисса 63 Мантисса Двойная точность 0 Расширенная (увеличенная) точность Рис. 2.3. Форматы данных с плавающей точкой Двоично-десятичные данные (BCD) На рис. 2.4 приведены форматы двоично-десятичных данных. 7 3 0 Цифра 7 Цифра 79 72 71 Игнорируется9 0 Цифра 0 Цифры Неупакованные BCD – одна цифра Упакованные BCD – две цифры 80-разрядное упакованное BСD в блоке FPU Рис. 2.4. Форматы двоично-десятичных данных Данные типа строка Строка представляет собой непрерывную последовательность бит, байт, слов или двойных слов (рис. 2.5). Строка бит может быть длиной до 1 Гбита, а длина остальных строк может составлять от 1 байта до 4 Гбайтов. Поддерживается АLU. A+N 7 0 N ... A+2N+1 A+2N 15 0 N A+4N+3 31 А+3 А+2 А+1 А 7 07 07 07 0 3 2 1 0 А+3 115 1 ... А+3 31 A+4N 0 N А+2 А+1 0 15 0 А А+1 А А+2 Строка байт Строка слов 0 0 Строка двойных слов 0 ... А+2 А+1 А А-1 7 07 07 07 0 Строка бит Рис. 2.5. Данные типа строка Символьные данные Поддерживаются строки символов в коде ASCII и арифметические операции (сложение, умножение) над ними (рис. 2.6). Поддержка осуществляется блоком АLU. 7 +N 0 7 Символ N … +1 0 Символ 1 ASCII ASCII 7 0 Символ 0 0 ASCII ASCII Рис. 2.6. Символьные данные Данные типа указатель Указатель содержит величину, которая определяет адрес фрагмента данных. Поддерживается два типа указателей, приведенных на рис. 2.7. 47 +5 +4 +3 +2 +1 0 0 Длинный указатель (дальний) селектор 16 р. смещение 32 р. 1 +3 +2 +1 3 0 0 Короткий указатель (ближний) смещение 32 р. Рис. 2.7. Данные типа указатель Данные ММХ-технологии Целочисленные данные могут быть как со знаком, так и без знака (рис. 2.8). 63 47 15 31 0 Упакованные 8 байт Данные 3 Данные 2 Данные 1 Данные 0 Данные 1 Упакованные 4 слова Упакованные 2 двойных слова Данные 0 64-разрядное слово Данные Рис. 2.8. Данные ММХ-технологии Данные SSE-расширения На рис. 2.9 приведен 128-разрядный формат упакованных данных с плавающей точкой одинарной точности. 127 95 Данные 3 63 Данные 2 0 Упакованные 4 числа с плавающей Данные 0 запятой одинарной точности 31 Данные 1 Рис. 2.9. Данные SSE-расширения Данные расширения SSE2 На рис. 2.10 приведен 128-разрядный формат упакованных данных с плавающей точкой с двойной точностью. 127 63 Данные 1 Данные 0 0 Упакованные 2 числа с плавающей запятой двойной точности Рис. 2.10. Данные SSE2 расширения с плавающей запятой На рис. 2.11 показаны 4 формата упакованных в 128 бит целочисленных данных, которые могут быть как со знаком, так и без знака. 127 95 63 31 0 Упакованные 16 байт Упакованные 8 слов Данные 3 Данные 2 Данные 1 Данные 0 Данные 1 Данные 0 Данные Упакованные 4 двойных слова Упакованные 2 64-разрядных слова 128-разрядное слово Рис. 2.11. Целочисленные данные SSE2 расширения Данные в IA-64 В IA-64 непосредственно поддерживается 6 типов данных, в том числе три формата, используемых ранее (одинарная точность, двойная точность, расширенная точность), 82-разрядный формат данных с плавающей точкой (рис. 2.12) и 64-разрядные целые – со знаком и без знака. 81 S 63 Порядок 17 р. Мантисса Рис. 2.12. Формат данных с плавающей точкой 82-разрядный 0 62. СТРУКТУРА И ФОРМАТЫ КОМАНД ЭВМ Команда представляет собой код, определяющий операцию и данные, участвующие в операции. По характеру выполняемых операций различают следующие основные группы команд: а) команды арифметических операций над числами с фиксированной и плавающей точками; б) команды десятичной арифметики; в) команды логических операций и сдвигов; г) команды передачи кодов; д) команды операций ввода/вывода; е) команды передачи управления; ж) команды векторной обработки; з) команды задания режима работы машины и др. Команда в общем случае состоит из операционной и адресной частей (рис. 2.14, а). В свою очередь, эти части, что особенно характерно для адресной части, могут состоять из нескольких полей. Операционная часть содержит код операции (КОП), который задает вид операции (сложение, умножение и др.). Адресная часть содержит информацию об адресах операндов и результате операции. Структура команды определяется составом, назначением и расположением полей в команде. Форматом команды называют ее структуру с разметкой номеров разрядов (бит), определяющих границы отдельных полей команды, или с указанием числа бит в определенных полях. Важной и сложной проблемой при проектировании ЭВМ является выбор структуры и форматов команды, т.е. ее длины, назначения и размерности отдельных ее полей. Естественно стремление разместить в команде в возможно более полной форме информацию о предписываемой командой операции. Однако в условиях, когда в современных ЭВМ значительно возросло число выполняемых различных операций и соответственно команд (в системе команд х86 более 500 команд) и значительно увеличилась емкость адресуемой основной памяти (4 Гбайт, 6 Гбайт), это приводит к недопустимо большой длине формата команды. Действительно, число двоичных разрядов, отводимых под код операции, должно быть таким, чтобы можно было представить все выполняемые машинные операции. Если ЭВМ выполняет М различных операций, то число разрядов в коде операции nкоп log2 М; например, при М = 500 nкоп = 9. Если основная память содержит S адресуемых ячеек (байт), то для явного представления только одного адреса необходимо в команде иметь адресное поле для одного операнда с числом разрядов nА log2 S; например, при S = 4 Гбайт nА = 32. Отмечавшиеся ранее, характерные для процесса развития ЭВМ расширение системы (наборы) команд и увеличение емкости основной памяти, а особенно создание микроЭВМ с коротким словом, потребовали разработки методов сокращения длины команды. При решении этой проблемы существенно видоизменилась структура команды, получили развитие различные способы адресации информации. Проследим изменения классических структур команд. Чтобы команда содержала в явном виде всю необходимую информацию о задаваемой операции, она должна, как это показано на рис. 2.14, б, содержать следующую информацию: А1, А2 – адреса операндов, А3 – адрес результата, А4 – адрес следующей команды (принудительная адресация команд). Такая структура приводит к большой длине команды (например, при М = 500, S = 4 Гб длина команды – 137 бит) и неприемлема для прямой адресации операндов основной памяти. В компьютерах с RISC-архитектурой четырехадресные команды используются для адресации операндов, хранящихся в регистровой памяти процессора. Можно установить, что после выполнения данной команды, расположенной по адресу К (и занимающей L ячеек), выполняется команда из (К + L)-й ячейки. Такой порядок выборки команды называется естественным. Он нарушается только специальными командами передачи управления. В таком случае отпадает необходимость указывать в команде в явном виде адрес следующей команды. В трехадресной команде (рис. 2.14, в) первый и второй адреса указывают ячейки памяти, в которых расположены операнды, а третий определяет ячейку, в которую помещается результат операции. Можно условиться, что результат операции всегда помещается на место одного из операндов, например первого. Получим двухадресную команду (рис. 2.14, г), т.е. для результата используется подразумеваемый адрес. В одноадресной команде (рис. 2.14, д) подразумеваемые адреса имеют уже и результат операции, и один из операндов. Один из операндов указывается адресом в команде, в качестве второго используется содержимое регистра процессора, называемого в этом случае регистром результата, или аккумулятором. Результат операции записывается в тот же регистр. Наконец, в некоторых случаях возможно использование безадресных команд (рис. 2.14, е), когда подразумеваются адреса обоих операндов и результата операции, например при работе со стековой памятью. а Код операции Операционная часть б в г д Адресная часть КОП А1 А2 А3 КОП А1 А2 А3 КОП А1 А2 А4 е КОП А1 КОП Рис. 2.14. Структуры а – обобщенная; б – четырехадресная; г – двухадресная; д – одноадресная; е – безадресная в – команд: трехадресная; 63. СПОСОБЫ АДРЕСАЦИИ ИНФОРМАЦИИ В ЭВМ Следует различать понятия адресный код в команде АR и исполнительный (физический адрес) адрес АИ. Адресный код — это информация об адресе операнда, содержащаяся в команде. Исполнительный адрес — это номер ячейки памяти, к которой производится фактическое обращение. Таким образом, способ адресации можно определить как способ формирования исполнительного адреса операнда АИ.по адресному коду команды АК. В системах команд современных ЭВМ часто предусматривается возможность использования нескольких способов адресации операндов для одной и той же операции. Для указания способа адресации в некоторых системах команд выделяется специальное поле в команде — поле «метод» (указатель адресации УА), рис.2.3, а. В этом случае любая операция может выполняться с любым способом адресации, что значительно упрощает программирование. КОП УА А а) КОП А б) Рис.2.3. Общая структура команды: а) – с указателем метода адресации; б) – без указателя метода адресации Классификация способов адресации по наличию адресной инф-ции в команде. явная адресация неявная адресация. При явной адресации операнда в команде есть поле адреса этого операнда, в котором задается адресный код АК. Большинство методов адресации являются явными. При неявной адресации адресное поле в команде отсутствует, адрес операнда подразумевается кодом операции. Классификация способов адресации по кратности обращения в память. Широко используются следующие методы адресации операнда с различной кратностью обращения (r) в память: 1. Непосредственная (r = 0) 2. Прямая (r = 1) 3. Косвенная (r 2) Непосредственная адресация операнда. Обращение к регистровой памяти (РП) или ОП не производится (R = 0). Таким образом уменьшается время выполнения операции, сокращается объем памяти. Прямая адресация операндов. При этом способе (рис.2.5) адресации обращение за операндом в РП или ОП производится по адресному коду в поле команды, т.е. исполнительный адрес операнда совпадает с адресным кодом команды (АИСП. = АК). Обеспечивая простоту программирования, этот метод имеет существенные недостатки, так как для адресации к ячейкам памяти большой емкости требуется «длинное» адресное поле в команде. nКОП РК КОП nАК АК nКОП КОП mРП nАК АК mОП РП . . . а) АИ РП Операнд ОП m РП . . . б) МРП АИ ОП Операнд . . МОП Рис.2.5. Схема прямой адресации: а) – к регистровой памяти; б) – к основной памяти Косвенная адресация операндов. Адресный код команды указывает адрес ячейки памяти, в которой находится не сам операнд, а лишь адрес операнда, называемый указателем операнда. Адресация к операнду через цепочку указателей (косвенных адресов) называется косвенной. Адрес указателя - остается неизменным, а косвенный адрес может изменяться в процессе выполнения программы. Это обеспечив переадресацию данных, т.е. упрощает обработку массивов и списковых структур данных, упрощает передачу параметров подпрограммам, но не обеспеч перемещаемость программ в памяти. (рис. 2.6 а) 64. ПРИНЦИПЫ ОРГАНИЗАЦИИ СИСТЕМЫ ПРЕРЫВАНИЯ ПРОГРАММ Для оценки эффективности систем прерывания могут быть использованы следующие характеристики.1. Общее число запросов прерывания (входов в систему прерывания). 2. Время реакции — время между появлением запроса прерывания и моментом прерывания текущей программы. Для одного и того же запроса задержки в исполнении прерывающей программы зависят от того, сколько программ со старшим приоритетом ждут обслуживания, поэтому время реакции определяют для запроса с наивысшим приоритетом (tP). Время реакции зависит от того, в какой момент допустимо прерывание. Большей частью прерывание допускается после окончания текущей команды. В этом случае время реакции определяется в основном длительностью выполнения команды Это время реакции может оказаться недопустимо большим для ЭВМ, предназначенных для работы в реальном масштабе времени. В таких машинах часто допускается прерывание после любого такта выполнения команды (микрокоманды). Однако при этом возрастает количество информации, подлежащей запоминанию и восстановлению при переключении программ, так как в этом случае необходимо сохранять также и состояние счетчика тактов, регистра кода операции и некоторых других узлов. Такая организация прерывания возможна только в машинах с быстродействующей сверхоперативной памятью. Рис.3.15. Упрощенная временная диаграмма процесса прерывания Имеются ситуации, в которых желательно немедленное прерывание. Если аппаратура контроля обнаружила ошибку, то целесообразно сразу же прервать операцию, пока ошибка не оказала влияние на следующие такты работы программы. 3. Затраты времени на переключение программ (издержки прерывания) равны суммарному расходу времени на запоминание и восстановление состояния программы tизд= t3 + tв. 4. Глубина прерывания – максимальное число программ, которые могут прерывать друг друга. Если после перехода к прерывающей программе и вплоть до ее окончания прием запросов прекращается, то говорят, что система имеет глубину прерывания, равную 1. Глубина равна n, если допускается последовательное прерывание до n программ. Глубина прерывания обычно совпадает с числом уровней приоритета в системе прерыванияСистема с большим значением глубины прерывания обеспечивает более быструю реакцию на срочные запросы.Если запрос окажется не обслуженным к моменту прихода нового запроса от того же источника, то возникает так называемое насыщение системы прерывания.В этом случае предыдущий запрос от данного источника будет машинально утерян, что недопустимо. 1. Регистровые структуры центрального процессора IA-32. 80386 имеет 32 программно-доступных регистра. Подразделить их можно на следующие категории: 1. регистры общего назначения; 2. регистры сегментации; 3. регистр флагов; 4. регистры управления; 5. регистры системного адреса; 6. регистр тестов; 7. регистр отладки. Эти регистры являются также набором регистров процессоров Intel 8086 и Intel 80286, поэтому все 16-и разрядные регистры процессоров более ранних выпусков "покрываются" 32-х разрядными регистрами 80386-го процессора. Регистры базовой архитектуры микропроцессора включают: A)регистры общего адреса и данных Б)указатель команд В)регистр флагов. Данные регистры при включении новой задачи загружаются новым содержимым. Базовая архитектура содержит 6 прямо доступных сегмента, каждый размером до 4 Гбайт. Сегменты указываются значениями селектора, помещенными в регистр сегмента. Другой тип регистров – это регистры управления, системного адреса, отладки и тестов. Они используются для отладки операционных систем. 1. Регистры отладки и тестовые регистры Регистры отладки. Шесть доступных для программиста регистров отладки обеспечивают поддержку (на кристалле) отладки. Регистр отладки CRO-3 классифицирует четыре линейных останова. Другой из них DR6 используется для установки точек останова и регистра статуса отладки DR7, а также отображает текущее состояние точек останова. 2. Регистры общего назначения (РОН) Микропроцессор Intel 80386 имеет 8-м 32-х разрядных регистров общего назначения. Они поддерживают 16, 32-х разрядные адресные операнды, 1, 8, 16, 32, 64 операнды данных и битовые поля от 1 до 32 битов. Они называются: EAX, EBX, ECX, EDX, ESI, EDI, EBP, ESP. Младшие 16 разрядов каждого регистра могут использоваться по отдельности, они называются: AX, BX, CX, DX, SI, DI, BP, SP. Также могут индивидуально использоваться младший (0-7) и старший (8-15) байты РОН AX, BX, CX, DX, соответственно их называют: AL, BL, CL, DL и AH, BH, CH, DH. 3. Указатель команд (IP) Регистр указателя команд представляет собой 32-х разрядный регистр, который называют EIP. Он содержит смещение следующей команды, которую нужно выполнить. Смещение всегда определяется относительно сегмента кода. Его младшие 16 бит называются IP и используются при шестнадцатиразрядной адресации. 4. Регистр флагов Регистр флагов является 32-х разрядным и называется EFLAGS. Определенные биты EFLAGS управляют некоторыми операциями и подчеркивают статус 80386. Младшие 16-ть разрядов EFLAGS представляют собой регистр FLAGS, который может использоваться при выполнении операций с 8086. Неопределенные биты являются зарезервированными, т. е. в настоящий момент они не имеют значения, однако могут быть использованы для специальных целей в последующих версиях микропроцессора. Все флаги младшего байта регистра устанавливаются арифметическими или логическими операциями процессора. 5. Сегментные регистры Шесть 16-ти разрядных сегментных регистров содержат базовые адреса сегментов, определяющие сегменты памяти текущей адресации. В защищенном режиме, каждый сегмент может иметь размеры от одного байта до целого линейного и физического пространства машины до 4Гб в режиме реальной адресации, максимальный размер сегмента ограничен на 64Кб. Шесть сегментов, адресуемых в любой данный момент, определяются содержимым регистров CS, SS, DS, ES, FS и GS. Значение в CS указывает на текущий сегмент кода, содержимое SS указывает текущий сегмент стека, а значения в DS, ES, FS, GS на сегменты данных. 6. Регистры дескриптора сегмента Регистры дескриптора сегмента невидимы для программиста. В 80386, регистр дескриптора невидимый для программиста соотнесен с каждым видимым регистром селектора. Каждый из них содержит 32-х битовый базовый адрес сегмента, его границу (предел) и другие необходимые признаки сегмента. Когда адрес сегмента загружается в сегментный регистр, ассоциативный (соотнесенный) регистр дескриптора автоматически модифицируется в соответствии с новой информацией. В защищенном режиме базовый адрес, граница, все признаки модифицируются содержимым регистра дескриптора сегмента, индексированного селектором. Каждый раз, когда происходит ссылка на ячейку памяти, регистр дескриптора сегмента, автоматически вовлекается ссылкой на ячейку памяти. 32-х битовый базовый адрес сегмента становится компонентом вычисления линейного адреса, 32х битовое значение границы используется для операций контроля границы, а признаки проверяются на соответствие типу ссылки на ячейку памяти, которая запрашивается. 7. Управляющие регистры Три управл. регистра по 32 бита: CR0, CR2 и CR3. Наряду с регистрами системного адреса поддерживают состояние машины и воздействуют на все задачи в системе. 8. Регистры системного адреса Четыре специальных регистра существуют для обращения к таблицам или сегментам, поддерживаемыми 80286/80386 моделью защиты. Данные таблицы или сегменты следующие: GDT (таблица глобального дескриптора), IDT (таблица дескриптора прерывания), LDT (таблица локального дескриптора), TSS (сегмент состояния задачи). Адреса данных таблиц и сегментов помещены в память специальных регистров: регистров системного адреса и регистров системного сегмента. Называются данные регистры соответственно GDTR, IDTR, LDTR, TR.Регистровые структуры центрального процессора х86-64, IA-64. Регистры IA-64 В состав регистровых файлов IA-64 входят: 128 регистров общего назначения GPR (64разрядных); 128 регистров с плавающей запятой FR (82-разрядных); 128 прикладных регистров (в основном 64-разрядных) AR; 64 одноразрядных регистров предикатов PR; 8 регистров переходов BR(64-разрядных);не менее 4-х регистров идентификатора процесса CPUID; счетчик команд IP; регистр маркера текущего окна CFM стека регистров и др. Регистры CPUID являются 64-разрядными. В CPUID-регистрах 0 и 1 лежит информация о производителе, в регистре 2 находится серийный номер процессора, а в регистре 3 задается тип процессора (семейство, модель, версия архитектуры и т.п.) и число CPUID-регистров. Разряды регистра 4 указывают на поддержку конкретных особенностей IA-64, т.е. тех, которые реализованы в данном процессоре. Прикладные регистры AR0-AR127 - специализированные (в основном 64-разрядные) регистры, применяемые в IA-64 и IA-32. AR0-7 называются регистрами ядра; запись в них привилегированна, но они доступны на чтение в любом приложении и используются для передачи приложению сообщений от операционной системы. Среди других прикладных регистров укажем на AR16 (RSC) - регистр конфигурации стека регистров, используемый для управления работой "машиной" стека регистров IA-64 (RSE); AR17 (BSP), в котором находится адрес в памяти, где сохраняется положение GR32 в текущем окне стека; AR40 (FPSR) - регистр состояния для команд с плавающей запятой IA64; AR44 (ITC) - интервальный таймер; AR64 (PFS) - регистр предыдущего состояния функции, куда автоматически копируются некоторые другие регистры при вызове подпрограмм; AR65 (LC), используемый для организации циклов со счетчиком, и, наконец, 6-разрядный регистр эпилога AR66 (EC). Ряд AR-регистров является фактически регистрами IA-32 (дескриптор сегмента кодов, дескриптор сегмента стека) 64-разрядные регистры GR0-127 применяются не только для целочисленных операций IA-64; GR8-31 в режиме IA-32 используются также под целочисленные регистры и регистры селекторов и дескрипторов сегментов IA-32. GR0-31 называются статическими регистрами (GR0 всегда содержит 0), а GR32-127 стекируемыми регистрами. Статические регистры "видны" всем программам. Стекируемые регистры становятся доступными в программной единице через окно стека регистров, включающее локальные и выходные регистры, число которых задается командой alloc. 82-разрядные регистры с плавающей запятой FR0-127 также подразделяются на статические (FR0-31, причем всегда FR0=0.0, FR1=1.0) и вращаемые (FR32-127). FR8-31 в режиме IA-32 содержат числа с плавающей запятой и мультимедийные регистры. Вращение регистров является в некотором роде частным случаем переименования регистров, применяемого во многих современных суперскалярных процессоров с внеочередным спекулятивным выполнением команд. В отличие от них, вращение регистров в IA-64 управляется программно. 64-разрядные регистры переходов BR0-7 применяются для указания адреса перехода в соответствующих командах перехода (если адрес перехода не кодируется в команде явно). Регистры предикатов PR0-63 являются одноразрядными; в них помещаются результаты команд сравнения. Обычно эти команды устанавливают сразу два регистра PR в зависимости от условия - соответственно истинность условия и его отрицания. Такая избыточность обеспечивает дополнительную гибкость. Регистры х86-64 В процессорах x86-64 архитектуры (Hammer, Athlon 64, Opteron) существующие в х86 регистры общего назначения (GPR) расширены с 32 до 64 бит (см. рис. 3.7) и к ним добавлены еще 8 новых 64-разрядных регистров (R8 – 15). Также 8 новых регистров (XMM8 – 15) добавлено в блок SSE, что обесп ечивает поддержку SSE-2. В блоке FPU используются существующие в х87 регистры данных (80-разрядные). Регистр указателя команд (EIP) также расширен до 64 разрядов. Регистровые расширения - это один из самых больших шагов в развитии архитектуры, пару десятков лет просуществовавшей на восьми регистрах общего назначения. Новый REX-префикс делает доступными 8 новых регистров общего назначения (R8 - R15) и 8 новых регистров SSE (XMM8 XMM15), а также расширения всех РОН до 64 бит. Без префикса REX размер операнда по умолчанию для большинства команд - 32 бит. Это даёт доступ к регистрам EAX, EBX, ECX, EDX, EDI, ESI, EBP и ESP. Исключение составляют две группы команд, которые будут рассмотрены ниже. Чтобы получить доступ к полному 64-битному операнду (RAX, RBX, RCX, RDX, RDI, RSI, RBP, RSP) и новым регистрам R8 - R15, команда должна содержать префикс REX. Также префикс REX обеспечивает новую способность регистров, делая доступным младший значащий байт, слово или двойное слово любого регистра общего назначения для операций (см. рис. 2). При этом команда операции над байтами не может одновременно использовать старший байт наследованных 16-разрядных регистров (ah, bh, ch, dh) и новый байтовый регистр. Эта возможность предоставляет компилятору единообразный набор 1-, 2-, 4- и 8-байтовых регистров для более удобного и эффективного распределения данных в регистрах. Для кодирования префикса REX использованы коды 40h - 4Fh2. Эти коды трактуются в 32-битном режиме как однобайтные инструкции INC (40h - 47h) и DEC (48h - 4Fh) над 32разрядными регистрами EAX - ESP. 66. СТРАТЕГИЯ РАЗВИТИЯ ПРОЦЕССОРОВ INTEL Стратегия развития Intel заключается во внедрении новых микроархитектур процессоров, основанных на новых поколениях полупроводниковой производственной технологии. Темпы выпуска инновационных микроархитектур и полупроводниковых технологий основаны на принципе, который корпорация Intel называет моделью «TICK-TOCK» («ТИКТАК»). Каждый «TICK» обозначает (табл. 3.1) новый этап развития полупроводниковых технологий (техпроцесс – 65 нм, 45 нм, 32 нм), а каждый «TOCK» – создание новой микроархитектуры (Intel Core, Nehalem, Sandy Bridge). Переход на новый техпроцесс сопровождается выпуском соответствующих семейств процессоров (Penryn, Westmere). Этот цикл, как правило, повторяется каждые 2 года. Новаторская микроархитектура «обкатывается» на текущем производственном процессе, затем переносится на новую производственную технологию. Данная модель развития позволяет осуществлять внедрение единообразной процессорной микроархитектуры во всех сегментах рынка. Стратегия развития процессоров Intel Intel Core Penryn Nehalem NEW NEW NEW Microarchitecture Process Microarchitecture 65 nm 45 nm 45 nm 2006 г. 2007 г. 2008 г. TOCK TICK TOCK Westmere NEW Process 32 nm 2009 г. TICK Sandy Bridge NEW Microarchitecture 32 nm 2010 г. TOCK Стратегия развития архитектуры и полупроводниковой технологии, реализуемая корпорацией Intel, не только позволяет выпускать новые решения в соответствии с запланированными темпами, но и способствует внедрению инновационных решений в отрасли на уровне платформ, расширяя использование преимуществ высокой производительности и энергоэкономичности. 67. ОСОБЕННОСТИ МИКРОАРХИТЕКТУРЫ INTELCORE Микроархитектура Intel Core наследует философию эффективного энергопотребления, впервые реализованную в процессорах Intel Pen-tium M для мобильных ПК. Заимствовав лучшее от ставших основой для настольных и мобильных процессоров Intel микроархитектур Net Burst и Mobile, микроархитектура Intel Core содержит сотни нововведений, но основные из них сводятся к пяти технологическим решениям: 1. Технология Intel Wide Dynamic Execution (широкое динамическое исполнение). 2. Технология Intel Advanced Digital Media Boost (улучшенные цифровые медиа возможности). 3. Технология Intel Advanced Smart Cache (улучшенный интеллектуальный кэш). 4. Технология Intel Smart Memory Access (интеллектуальный доступ к памяти). 5. Технология Intel Intelligent Power Capability (интерактивное подключение подсистем). Рассмотрим подробнее каждую из перечисленных технологий. 68. МИКРОАРХИТЕКТУРА Intel Nehalem Микроархитектура Nehalem является дальнейшим развитием рассмотренной выше микроархитектуры Intel Core. Основные отличительные черты Nehalem Основными отличительными чертами данной микроархитектуры являются следующие: Усовершенствованное по сравнению с Core вычислительное ядро. Многопоточная технология SMT (Simultaneous Multi-Threading), позволяющая исполнять одновременно два вычислительных потока на одном ядре. Три уровня кэш-памяти: L1 кэш размером 64 Кбайта на каждое ядро, L2 кэш размером 256 Кбайт на каждое ядро, общий разделяемый L3 кэш размером 4, 8 и до 24 Мбайт. Интегрированный в процессор контроллер памяти с поддержкой нескольких каналов DDR3 SDRAM. Новая шина QPI с топологией точка – точка для связи процессора с чипсетом и процессоров между собой. Модульная структура. Монолитная конструкция – процессор состоит из одного полупроводникового кристалла. Технологический процесс с нормами производства – не более 45 нм. Использование двух, четырех или восьми ядер. Управление питанием и Turbo-режим. Усовершенствования вычислительного ядра Рис. 3.8. Структура ядра процессора микроархитектуры Nehalem В рассматриваемом ядре так называемый предпроцессор содержит следующие блоки: блок выборки команд и преддекодирования; блок предсказания переходов (ветвлений); блок очередей инструкций; декодер инструкций; блок обнаружения циклов в программе. Сначала х86 инструкции выбираются (Fletch) из кэш-памяти команд. Если в потоке команд оказывается команда условного перехода (ветвление программы), то включается механизм предсказания ветвления, который формирует адрес следующей выбираемой команды до того, как будет определено условие выполнения перехода. Основной частью блока предсказания ветвлений является ассоциативная память, называемая буфером адресов ветвлений ВТВ (Branch Target Buffer), в котором хранятся адреса ранее выполненных переходов. Кроме того, ВТВ содержит биты, хранящие предысторию ветвления, которые указывают, выполнялся ли переход при предыдущих выборках данной команды. При поступлении очередной команды условного перехода указанный в ней адрес сравнивается с содержимым ВТВ. Если этот адрес не содержится в ВТВ, т.е. ранее не производились переходы по данному адресу, то предсказывается отсутствие ветвления. В этом случае продолжается выборка и декодирование команд, следующих за командой перехода. При совпадении указанного в команде адреса перехода с каким-либо из адресов, хранящихся в ВТВ, производится анализ предыстории. В процессе анализа определяется чаще всего реализуемое направление ветвления, а также выявляются чередующиеся переходы. Если предсказывается выполнение ветвления, то выбирается и загружается в конвейер команда, размещенная по предсказанному адресу. В дополнение к уже имеющемуся в Intel Core блоку предсказания переходов был добавлен в Nehalem ещё один «предсказатель» второго уровня. Он работает медленнее, чем первый, но зато благодаря более вместительному буферу, накапливающему статистику переходов, обладает лучшей глубиной анализа. Далее, разделенные х86 инструкции (Pre Decode) на простые и сложные организуются в виде очередей (Instruction Queues) на входах четырех декодеров. Декодеры преобразуют х86 команды в микрокоманды, под управлением которых в процессоре выполняются элементарные операции (микрооперации). Как в Intel Core, три декодера используются для обработки простых инструкций, один – для сложных. Каждая простая х86 инструкция преобразуется в 1–2 микрокоманды, а для сложной инструкции из памяти микрокода (u Code ROM) выбирается последовательность микрокоманд (микропрограмма), которая содержит более двух микрокоманд (технология micro-ops fusion). Используя технологию macro fusion, четыре декодера могут обработать одновременно пять х86 команд, преобразуя их в четыре микрокоманды. В Nehalem увеличилось число пар x86 команд, декодируемых в рамках этой технологии «одним махом». Кроме того, технология macro fusion стала работать и в 64-битном режиме, в то время как в процессорах семейства Core 2 она могла активироваться лишь при работе процессора с 32-битным кодом. Следующее усовершенствование, связанное с повышением продуктивности начальной части исполнительного конвейера, коснулось блока обнаружения циклов в программе Loop Stream Detector. Этот блок появился впервые в процессорах с микроархитектурой Core и предназначался для ускорения обработки циклов. Определяя в программе циклы небольшой длины, Loop Stream Detector (LSD) сохранял их в специальном буфере, что давало возможность процессору обходиться без их многократной выборки из кэша и предсказания переходов внутри этих циклов. В процессорах Nehalem блок LSD стал ещё более эффективен благодаря его переносу за стадию декодирования инструкций. Иными словами, теперь в буфере LSD сохраняются циклы в декодированном виде, из-за чего этот блок стал несколько похож на Trace Cache процессоров Pentium 4. Однако Loop Stream Detector в Nehalem – это особенный кэш. Во-первых, он имеет очень небольшой размер, всего 28 микроопераций, во-вторых, в нём сохраняются исключительно циклы. После декодирования производится переименование регистров, переупорядочение (Retirement Unit) и сохранение до момента выполнения 128 микрокоманд в буфере (Reorder Buffer). Это количество микрокоманд на 33 % больше, чем в Intel Core (96 микрокоманд). На следующем этапе планировщик (Scheduler) через станцию резервирования (Reservation Station – RES) вместимостью до 36 инструкций (Intel Core – 32 инструкции) отправляет микрокоманды непосредственно на исполнительные устройства. Также как Core 2, процессоры с микроархитектурой Nehalem способны отправлять на выполнение до шести микроопераций одновременно. В каждом ядре процессора Intel Nehalem используются три универсальных порта (Port0, Port1, Port5) для связи с различными исполнительными устройствами, два порта (Port3, Port4) – для организации записи/загрузки (Store) адреса и данных в память и один (Port2) для организации чтения/выгрузки (Load) данных из памяти. Универсальные порты осуществляют связь с тремя блоками – для обработки целочисленных 64-битных данных (ALU), выполнения сдвигов (Shift) и операций сравнения (LEA); с тремя блоками – для обработки чисел с плавающей точкой (FAdd, FMul, FPShuffes); с тремя 128-битными блоками для обработки потоковых данных (SSE); с одним блоком – для исполнения переходов (Branch); со специальными блоками Divide (деление), Complex Integer (сложные целочисленные операции). В данном процессоре (ядре), как и в любом другом современном процессоре, реализована конвейерная технология обработки команд. Длина каждого из четырех конвейеров составляет 14 ступеней. В микроархитектуре Nehalem Intel продолжила взятый ранее курс на увеличение числа поддерживаемых SIMD инструкций. Пополненный набор команд расширился за счет семи новых инструкций и получил название SSE4.2. В SSE4.2 добавлено пять инструкций, предназначенных для ускорения синтаксического анализа XML-файлов. Также с помощью этих же инструкций возможно увеличение скорости обработки строк и текстов. Ещё две новые инструкции из набора SSE4.2 нацелены на совершенно иные приложения. Первая из них аккумулирует контрольную сумму, а вторая подсчитывает число ненулевых бит в источнике. 69. СЕМЕЙСТВО ПРОЦЕССОРОВ Intel Westmer e Основываясь на ошеломляющем успехе 45 нм производственного процесса с диэлектриками high-k и транзисторами с металлическими затворами, корпорация Intel в конце 2009 г. запустила 32 нм производственную технологию, в которой используются диэлектрики high-k и транзисторы с металлическими затворами второго поколения. Эта технология стала основой для новой 32 нм версии микроархитектуры Intel Nehalem. Новые процессоры Intel семейства Westmere стали первыми процессорами, созданными по нормам 32 нм техпроцесса. Эти процессоры известны под кодовыми названиями Clarkdale и Arrandale, предназначены для применения соответственно в настольных компьютерах и ноутбуках и входят в модельные линейки Intel Core i3, i5, i7. Процессоры Intel Westmere представляют собой двухъядерные решения. Кроме того, в их конструкции присутствуют два несущих кристалла (рис. 3.10), один из которых, выпускаемый по 32 нм техпроцессу, включает в себя два вычислительных ядра, разделяемую L3 кэш-память, контроллер шины QPI. Второй, более крупный кристалл, изготавливаемый по 45 нм технологии, содержит графический процессор GPU, двухканальный контроллер памяти DDR3, контроллер интерфейса PCI Express 2.0 и контроллер шин DMI и FDI (Flexible Display Interface). Взаимодействие между двумя кристаллами происходит по высокоскоростной шине QPI. В табл. 3.3 приведены характеристики процессоров Intel Clarkdale. Характеристики процессоров Intel Clarkdale Характеристики процессора Core i3 530 Core i3 540 Core i5 650 Core i5 660 Core i5 661 Core i5 670 Техпроцесс ядра CPU, нм 32 Техпроцесс ядра GPU, нм 45 Количество ядер CPU/ исполняемых потоков, шт. 2/4 Объем L3 кэш-памяти, Мб 4 Номинальная частота ЦП, ГГц 2.93 3.06 3.2 3.33 3.33 3.46 Частота ЦП с Turbo Boost (максимум), ГГц N/A N/A 3.46 3.6 3.6 3.73 Частота GPU, МГц 733 733 733 733 900 733 Есть Нет Есть Поддержка НТ Есть Поддерживаемая память, частота памяти, МГц Технология Intel vPro Dual Channel DDR3, 1333 Нет Нет Есть Технология Intel VT-x Есть Технология Intel VT-d Нет Нет Есть Есть Нет Есть Технология Intel TXT Нет Нет Есть Есть Нет Есть Набор инструкций AES-NI Нет Нет 87 73 TDP, Вт Есть 73 Из таблицы следует, что все процессоры поддерживают технологию Hyper-Threading (HT) или SMT, увеличивающую число вычислительных потоков, и технологию виртуализации VT-x. В большинстве процессоров реализованы новые инструкции из расширения AES-NI для ускорения выполнения алгоритмов шифрования и расшифровки. В этих же процессорах выполняется технология Turbo Boost, которая позволяет разгонять одно из вычислительных ядер до повышенных частот, что ускоряет работу с однопоточными приложениями. 70. ИЕРАРХИЧЕСКАЯ СТРУКТУРА ПАМЯТИ ЭВМ Памятью ЭВМ называется совокупность устройств, служащих для запоминания, хранения и выдачи информации. Основными характеристиками отдельных устройств памяти (ЗУ) являются емкость памяти, быстродействие и стоимость хранения единицы информации (бита). Емкость памяти определяется максимальным количеством данных, которые могут в ней храниться. Емкость измеряется в двоичных единицах (битах), машинных словах, но большей частью в байтах (1 байт = 8 бит). Часто емкость памяти выражают через число К = 1024, например, К бит — килобит, К байт — килобайт, 1024 Кбайт = 1 Мбайт (Мегабайт), 1024 Мбайт = 1 Гбайт (гигабайт), 1024 Гбайт = 1 Тбайт (терабайт). Быстродействие (задержка) памяти определяется временем доступа и длительностью цикла памяти. Время доступа - промежуток времени между выдачей запроса на чтение и моментом поступления запрошенного слова из памяти. Длительность цикла памяти определяется мин. временем между двумя последовательными обращениями к памяти. Требования к увеличению емкости и быстродействия памяти, а также к снижению ее стоимости являются противоречивыми. Чем больше быстродействие, тем технически труднее достигается и дороже обходится увеличение емкости памяти. Стоимость памяти составляет значительную часть общей стоимости ЭВМ. Исходя из этого память ЭВМ организуется в виде иерархической структуры (рис.4.1) запоминающих устройств, обладающих различными быстродействием и емкостью [ 4.1 ]. Чем выше уровень, тем выше быстродействие соответствующей памяти, но меньше её емкость. К верхнему (сверхоперативному) уровню относятся регистры операционных и управляющих блоков процессора, сверхоперативная память, управляющая память, буферная память. На втором уровне находится основная или оперативная память. На последующих уровнях размещается внешняя и архивная память. Регистры Процессор Сверхоперативная память (СОП) Уровни Буферная память Сверхоперативный Оперативная память Оперативный Система управления памятью обеспеч обмен информационными блоками между уровнями, причем обычно первое обращение к блоку инф-ции вызывает его перемещение с более низкого медленного уровня на более высокий. Это позволяет при последующих обращениях к данному блоку осущ его выборку с более быстродействующего уровня памяти. Внешняя память Внешний Непрерывный рост производительности ЭВМ проявляется, в первую очередь, в Рис.4.1. Иерархическая структура памяти повышении скорости работы процессора. Быстродействие ОП также растет, но все время отстает от быстродействия аппаратных средств процессора, в значительной степени потому, что одновременно Архивная память Архивный происходит опережающий рост её емкости, что делает более трудным уменьшение времени цикла работы памяти. Поэтому, быстродействие ОП часто оказывается недостаточным для обеспечения требуемой производительности ЭВМ. Это проявляется в несоответствии пропускных способностей процессора и ОП. Возникающая проблема выравнивания их пропускных способностей решается путем использования сверхоперативных буферных памятей небольшой емкости и повышенного быстродействия, хранящих команды и данные, относящиеся к обрабатываемому участку программы. При обращении к блоку данных, находящемуся на оперативном уровне, его копия пересылается в сверхоперативную буферную память (СБП). Последующие обращения производятся к копии блока данных, находящейся в СБП. Поскольку время выборки из сверхоперативной буферной памяти tСБУ (5 ис) много меньше времени выборки из оперативной памяти tОП, введение в структуру памяти СБП приводит к уменьшению эквивалентного времени обращения tЭ по сравнению с tОП: tЭ = tСБП + tОП , где = (1 — q) и q — вероятность нахождения блока в СБП в момент обращения к нему, т.е. вероятность «попадания». Очевидно, что при высокой вероятности попадания эквивалентное время обращения приближается к времени обращения к СБП. В основе такой организации взаимодействия ОП и СБП лежит принцип локальности обращений, согласно которому при выполнении какой-либо программы (практически для всех классов задач) большая часть обращений в пределах некоторого интервала времени приходится на ограниченную область адресного пространства ОП. Причем обращения к командам и элементам данных этой области производятся многократно. Это позволяет копии наиболее часто используемых участков программ и некоторых данных загружать в СБП и таким образом обеспечить высокую вероятность попадания q. Высокая эффективность применения СБП достигается при q 0,9. Буферная память не является программно доступной: это значит, что она влияет только на производительность ЭВМ, но не должна оказывать влияния на программирование прикладных задач. Поэтому, она получила название кэш — памяти (в переводе с английского — тайник). В структуре одних ЭВМ используется объединенная кэш — память команд и данных, в других ЭВМ раздельные кэш — памяти для команд и для данных. Кэш — память, входящую в состав процессора, называют кэш — памятью первого уровня. В современных компьютерах применяют кэш — память второго уровня, которая находится между процессором и ОП и еще больше повышает производительность ЭВМ. 71. Способы организации КЭШ памяти В функциональном отношении КЭШ-память рассматривается буферное ЗУ, размещённое между основной (оперативной) памятью и процессором. Основное назначение КЭШ-памяти - кратковременное хранение и выдача активной информации процессору, что сокращает число обращений к основной (оперативной) памяти, скорость работы которой меньше чем КЭШ-памяти. В процессе работы отдельные блоки информации копируются из основной памяти в КЭШ-память, и когда процессор обращается за командой или данными, то сначала проверяется их наличие в КЭШ-памяти. Если необходимая информация находится там, то она быстро извлекается. Такой случай обращения называется КЭШ-попаданием. Если необходимая информация в КЭШ-памяти отсутствует, то она выбирается из основной памяти и одновременно заносится в КЭШпамять. Такой случай называется КЭШ-промахов. Повышение быстродействия вычислительной системы достигается, когда КЭШпопадания реализуются намного чаще, чем КЭШ-промахи. Высокий процент КЭШпопаданий обеспечивается благодаря тому, что в большинстве случаев программы обращаются к ячейкам памяти, расположенным вблизи от ранее использованных. За единицу информации при обмене принята строка, причём под строкой понимается набор слов, выбираемый из оперативной памяти при одном к ней обращении. Хранимая в оперативной памяти (ОП) информация представляется, таким образом, совокупностью строк с последовательными адресами. В любой момент времени строки в КЭШ-памяти представляют собой копии строк из некоторого их набора в ОП, однако расположены они не обязательно в такой же последовательности, как в ОП. Типовая структура КЭШ-памяти. Включает основные блоки, кот обеспеч её взаим-ие с ОП и централ.процессором. Адресация ОП Основная ОП Блок замены строк Накопитель строк и адресных тегов Блок формирования запросов Блок сравнения адресов Регистр строк Блок обработки адресов Селектордемультиплексор Адрес от ЦП ЦП Слово к ЦП Кэш - память Строки, составленные из информационных слов, и связанных с ними адресные теги хранятся в накопителе, который является основой КЭШ-памяти. Адрес требуемого слова, поступающий от ЦП, вводится в блок обработки адресов (БОА), в котором реализуются принятые в данной КЭШ-памяти принципы использования адресов при организации их сравнения с адресными тегами. Само сравнение производится в блоке сравнения адресов (БСА), который конструктивно совмещается с накопителем, если КЭШ-память строится по схеме ассоциативной памяти. Назначение БСА состоит в выявлении попадания или промаха при обработке запросов от центрального процессора. Если если имеет место КЭШ-попадание (т.е. искомое слово храниться в КЭШ-памяти, о чём свидетельствует совпадение кодов адреса, поступающего от центрального процессора, и одного из адресов некоторого адресного тега ), то соответствующая строка из КЭШ-памяти переписывается в регистр строк. С помощью селектора-демультиплексора из неё выделяется искомое слово, которое и направляется в центральный процессор. В случае промаха с помощью блока формирования запросов (БФЗ) осуществляется инициализация выборки из ОП необходимой строки. Адресация ОП при этом производится в соответствии с информацией, поступившей от центрального процессора. Выбираемая из памяти строка вместе со своим адресным тегом помещается в накопитель и регистр строк, а затем искомое слово передается в центральный процессор. Для высвобождения места в КЭШ-памятис одна из строк удаляется. Определение удаляемой строки производится посредством блока замены строк (БЗС), в котором хранится информация , необходимая для реализации принятой стратегии обновления находящихся в накопителе строк. Способы размещения данных в КЭШ-памяти. Существует четыре способа размещения данных в КЭШ-памяти: прямое распределение полностью ассоциативное распределение частично ассоциативное распределение распределение секторов. Для того, чтобы конкретизировать описание, положим, что КЭШ-память может содержать 128 строк 16 слов в строке 8 р. , а основная память может содержать 128*128=16384 строк. Для адресации основной памяти используется 18 бит. Из них старшие 14 показывают адрес строки, а младшие 4 бит - адрес слова внутри этой строки. При одном обращении к памяти выбирается одна строка. 128 строк КЭШ-памяти указываются 7разрядными адресами. Если процессор намерен получить информацию из некоторой ячейки основной памяти, а копия содержимого этой ячейки уже имеется в КЭШ-памяти, то вместо оригинала считывается копия, время считывания составляет 50нс. Информация в КЭШ-памяти и основной памяти не изменяется. Если копии нет, то производится обращение к основной памяти с временем считывания 500нс. Полученная информация переписывается в процессор и попутно запоминается в КЭШ-памяти. Чтение информации в отсутствие копии отражено во второй строке таблицы. Информация в основной памяти не изменяется. При записи информации в ячейку памяти и наличии копии этой ячейки в КЭШ-памяти оригинал и копия обновляются. Таким образом, КЭШ-память ускоряет считывание команд и данных, которые "недавно" считывались или корректировались, а в остальных случаях выигрыша нет. При исп-нииКЭШ-памяти от 80 до 95% операций чтения выполняются быстро (за 506, а не 500нс). Для записи в КЭШ-памятьсущнескметодов замещения старой инф. Эти методы называются стратегией обновления основной памяти. Если результат обновления строк КЭШ-памяти не возвращается в основную память, то содержимое основной памяти становится неадекватным вычислительному процессу. Чтобы избежать этого, предусмотрены методы обновления основной памяти, которые можно разделить на две большие группы: метод сквозной записи и метод обратной записи. 72. Принципы организации оперативной памяти. Оперативная память удовлетворяет запросы кэш-памяти и устройств ввода/вывода. Она является местом назначения для ввода и источником для вывода. Существуют несколько методов организации оперативной памяти: 1) Метод строк/колонок (Row/column). ОП представляет собой матрицу разделенную на строки и колонки. При обращении к ОП одна часть адреса определяет строку, а другая - колонку матрицы. Ячейка матрицы, оказавшаяся на пересечении выбранных строк и колонок считывается в память или обновляется ее содержимое. 2) Метод статических колонок (Static-column) . При данном методе адресации ОП информация, относящаяся к какой-либо программе, размещается в определенной колонке. Последующее обращение к данной программе происходит в ту же самую колонку. За счет статичности части адреса (ее не надо передавать по адресной шине) доступ к данным осуществляется быстрее. 3) Метод чередования адресов (Interleaved). Впервые стал применяться в 386 моделях АТ компьютерах. Данный метод предполагает считывание (или запись) информации не по одному, а сразу по нескольким адресам: i, i+1, i+2 и т.д. Количество одновременно опрашиваемых адресов, по которым происходит считывание информации, определяет кратность чередования адресов, что соответствует количеству блоков ОП. На практике обычно используется 2-х или 4-х кратное чередование адресов, т.е. ОП делится на 2 или 4 блока. Запись информации в блоки осуществляется независимо друг от друга. Информация по адресу i хранится в первом блоке, по адресу i+1 во втором блоке и т.д. Считываемая с блоков информация далее переписывается в кэшпамять для последующей переработки. 4) Метод страничной организации (Page-mode) . Память адресуется не по байтам, а по границам страниц. Размер страницы обычно равен 1 или 2 Кбайта. Данный метод предполагает наличие в системе кэш-памяти емкостью не менее 128 Кб куда предварительно считываются требуемые страницы ОП для последующей переработки МП или другим устройством. Обновленная информация периодически из кэшпамяти сбрасывается в ОП. Последние два метода системной организации памяти предполагают обязательное наличие в системе сверх быстродействующей кэш-памяти для опережающего (read-ahaed) чтения в нее информации из ОП с последующей обработкой ее микропроцессором, что снижает время простоя последнего и повышает общую производительность системы. Для идентификации переменных и команд используются символьные имена (метки), виртуальные адреса и физические адреса (рис. 4.8). Символьные имена присваивает пользователь при написании программы на алгоритмическом языке или ассемблере.