Перекин Р - MES conference

advertisement

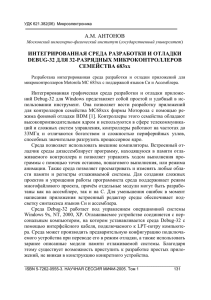

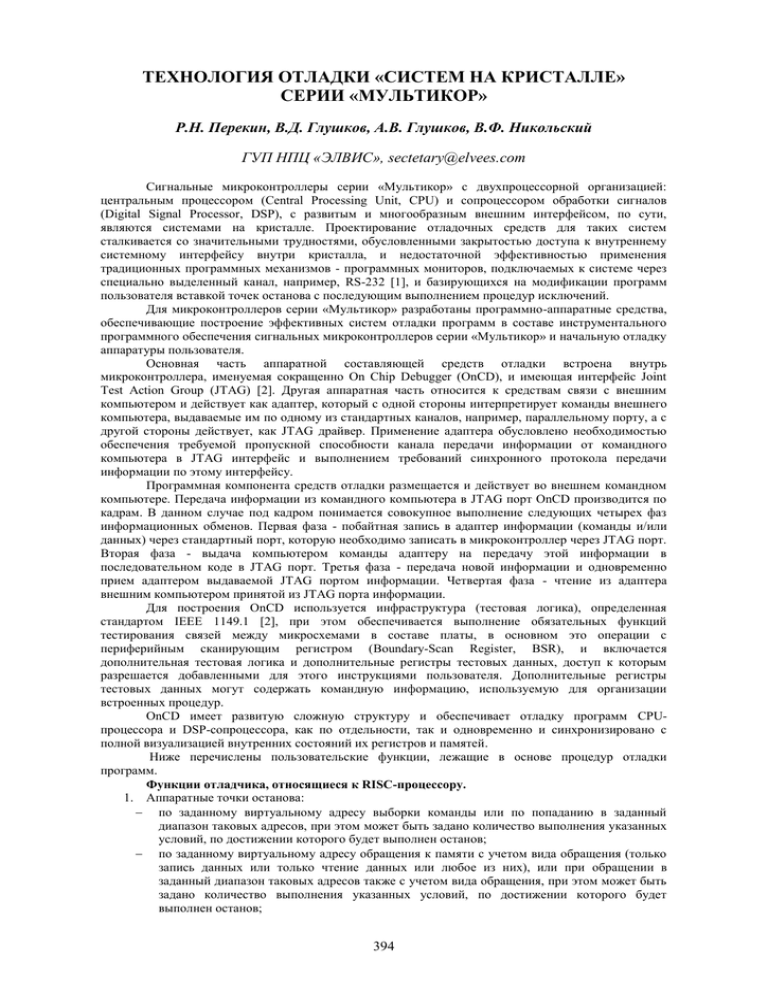

ТЕХНОЛОГИЯ ОТЛАДКИ «СИСТЕМ НА КРИСТАЛЛЕ» СЕРИИ «МУЛЬТИКОР» Р.Н. Перекин, В.Д. Глушков, А.В. Глушков, В.Ф. Никольский ГУП НПЦ «ЭЛВИС», sectetary@elvees.com Сигнальные микроконтроллеры серии «Мультикор» с двухпроцессорной организацией: центральным процессором (Central Processing Unit, CPU) и сопроцессором обработки сигналов (Digital Signal Processor, DSP), с развитым и многообразным внешним интерфейсом, по сути, являются системами на кристалле. Проектирование отладочных средств для таких систем сталкивается со значительными трудностями, обусловленными закрытостью доступа к внутреннему системному интерфейсу внутри кристалла, и недостаточной эффективностью применения традиционных программных механизмов - программных мониторов, подключаемых к системе через специально выделенный канал, например, RS-232 [1], и базирующихся на модификации программ пользователя вставкой точек останова с последующим выполнением процедур исключений. Для микроконтроллеров серии «Мультикор» разработаны программно-аппаратные средства, обеспечивающие построение эффективных систем отладки программ в составе инструментального программного обеспечения сигнальных микроконтроллеров серии «Мультикор» и начальную отладку аппаратуры пользователя. Основная часть аппаратной составляющей средств отладки встроена внутрь микроконтроллера, именуемая сокращенно On Chip Debugger (OnCD), и имеющая интерфейс Joint Test Action Group (JTAG) [2]. Другая аппаратная часть относится к средствам связи с внешним компьютером и действует как адаптер, который с одной стороны интерпретирует команды внешнего компьютера, выдаваемые им по одному из стандартных каналов, например, параллельному порту, а с другой стороны действует, как JTAG драйвер. Применение адаптера обусловлено необходимостью обеспечения требуемой пропускной способности канала передачи информации от командного компьютера в JTAG интерфейс и выполнением требований синхронного протокола передачи информации по этому интерфейсу. Программная компонента средств отладки размещается и действует во внешнем командном компьютере. Передача информации из командного компьютера в JTAG порт OnCD производится по кадрам. В данном случае под кадром понимается совокупное выполнение следующих четырех фаз информационных обменов. Первая фаза - побайтная запись в адаптер информации (команды и/или данных) через стандартный порт, которую необходимо записать в микроконтроллер через JTAG порт. Вторая фаза - выдача компьютером команды адаптеру на передачу этой информации в последовательном коде в JTAG порт. Третья фаза - передача новой информации и одновременно прием адаптером выдаваемой JTAG портом информации. Четвертая фаза - чтение из адаптера внешним компьютером принятой из JTAG порта информации. Для построения OnCD используется инфраструктура (тестовая логика), определенная стандартом IEEE 1149.1 [2], при этом обеспечивается выполнение обязательных функций тестирования связей между микросхемами в составе платы, в основном это операции с периферийным сканирующим регистром (Boundary-Scan Register, BSR), и включается дополнительная тестовая логика и дополнительные регистры тестовых данных, доступ к которым разрешается добавленными для этого инструкциями пользователя. Дополнительные регистры тестовых данных могут содержать командную информацию, используемую для организации встроенных процедур. OnCD имеет развитую сложную структуру и обеспечивает отладку программ CPUпроцессора и DSP-сопроцессора, как по отдельности, так и одновременно и синхронизировано с полной визуализацией внутренних состояний их регистров и памятей. Ниже перечислены пользовательские функции, лежащие в основе процедур отладки программ. Функции отладчика, относящиеся к RISC-процессору. 1. Аппаратные точки останова: по заданному виртуальному адресу выборки команды или по попаданию в заданный диапазон таковых адресов, при этом может быть задано количество выполнения указанных условий, по достижении которого будет выполнен останов; по заданному виртуальному адресу обращения к памяти с учетом вида обращения (только запись данных или только чтение данных или любое из них), или при обращении в заданный диапазон таковых адресов также с учетом вида обращения, при этом может быть задано количество выполнения указанных условий, по достижении которого будет выполнен останов; 394 по заданному виртуальному адресу выборки команды и по заданному виртуальному адресу обращения к памяти с учетом вида обращения. Останов происходит по событию, которое наступило раньше; по заданному значению одного векторного исключения или любой выборкой из векторов исключений. 2. Одношаговое выполнение конвейера команд, которое используется отладчиком для организации выполнения программы по одной команде. 3. Доступ к регистру команд по чтению и записи. При необходимости выполнение новой команды с сохранением состояния процессора, зафиксированного при останове. Эта функция совместно с одношаговым выполнением конвейера команд используется для визуализации состояния регистров и памяти системы, не проецирующихся в её адресное пространство, без модификации отлаживаемой программы в памяти. Например, чтение регистрового файла с сохранением или занесением в него нового значения. 4. Доступ к счётчику команд (Program Counter, PС) по чтению и записи. При необходимости выполнение операций с заданным адресом, например, пуск на выполнение программы с указанного адреса. 5. Чтение регистров РС конвейера: регистров адреса команды, находящихся соответственно на стадиях декодирования (Program Counter decode, PCdec), исполнения (Program Counter execute, PCexe), обмена с памятью (Program Counter memory, PCmem), записи в регистровый файл (Program Counter write back, PCwb). 6. Доступ (запись или чтение данных) ко всему адресному пространству микроконтроллера. 7. Выполнение заданного числа команд в исполняемой программе. 8. Останов RISC-процессора при достижении программой DSP-сопроцессора заданной точки останова или выполнении им заданного числа команд. Этот механизм используется при совместной отладке программ RISC и DSP-процессоров. Функции отладчика, относящиеся к DSP-сопроцессору. Регистры аппаратных средств отладки DSP-сопроцессора, размещены в адресном пространстве памяти со всеми возможностями доступа к ним, описанными выше. С помощью этих регистров для DSP-сопроцессора может быть задан: останов выполнения программы при достижении заданного адреса команды; останов выполнения программы при выполнении заданного числа команд; останов выполнения программы при достижении заданного адреса команды или при выполнении заданного числа команд; пуск на выполнение программы и контроль её окончания при остановленном RISCпроцессоре. Это свойство позволяет автономно отлаживать программы DSP-сопроцессора. Блок-схема JTAG порта и модуля OnCD приведена на рис. 1. В блок-схеме можно выделить две части: собственно отладочные средства (модуль OnCD) и логику, поддерживающую стандарт IEEE 1149.1 (остальная часть, кроме модуля OnCD), которая называется Test Access Port (TAP) [2]. Согласно стандарту IEEE 1149.1 в ТАР присутствуют модуль Test Access Port Controller (TAP ctrl), представляющий собой по сути автомат на 16-состояний, регистр команд (Instruction Register, IR), одноразрядный сдвиговый регистр (Bypass), идентификационный регистр (ID Register) и BSR. Структурная схема модуля OnCD представлена на рис. 2. На структурной схеме модуля OnCD представлены регистры и логические блоки, составляющие основу модуля. Регистры, доступные как в OnCD, так и в RISC процессоре, реализуются в двух вариантах. Если изменение информации в регистре при его загрузке не влияет на состояние модуля OnCD или микроконтроллера, то такой регистр реализуется, как чисто сдвиговый регистр, в противном случае регистр реализуется «двухэтажным». Первый «этаж» - это сдвиговый регистр, а второй параллельный регистр, информация в который заносится одномоментно из сдвигового регистра во время фазы Updata_DR автомата, находящегося в модуле TAP ctrl . Чтение информации из параллельного регистра в последовательный регистр осуществляется в фазе Capture_DR автомата в TAP ctrl, а затем выводится в последовательном коде из сдвигового регистра в фазе Shift_DR автомата в TAP ctrl во время записи в него нового кода. Запись в регистры осуществляется по входу Test Data Input (TDI), а чтение через выход Test Data Output (TDO). В алгоритме отладки программ используются следующие процедуры. 1. Процедура первоначального перевода микроконтроллера в режим отладки. Обычно это осуществляется: при начальном включении микроконтроллера и действии системного сигнала RESET подачей команды DEBUG_REQUEST. После обнаружения внешним компьютером факта вхождения микроконтроллера в режим отладки сигнал RESET снимается; во время штатной работы программы микроконтроллера выполнением команды DEBUG_REQUEST; 395 выполнением в программе микроконтроллера команды BREAKD - команды входа в режим отладки. Для этого модифицируется исходная программа заменой штатной команды в требуемом логикой отладки месте на команду BREAKD. CPU OnCD модуль TAP MUX Boundary Scan Register Bypass ID Register 3 TDI 2 1 0 4-Bit Instruction Register (IR) MUX Decoder TDO TMS TCK TRST TAP Ctrl RESET Рис. 1. Блок-схема JTAG порта и модуля OnCD 2. Процедура загрузки в OnCD модуль условий останова исполняемой программы в контрольных точках и пуск программы на исполнение. 3. Процедура сканирования состояния микроконтроллера во время исполнения программы и определение момента перехода микроконтроллера в режим отладки. 4. Процедура индикации состояния микроконтроллера на момент останова. По способу доступа индицируемые компоненты подразделяются на: регистры, непосредственно доступные по каналу TDI-TDO. Это регистры конвейера РС (PC, PCdec, PCexe, PCmem, PCwb), регистр команд (Instruction Register decode, IRdec); регистры и ячейки памяти, которые проецируются в адресное пространство памяти микроконтроллера. Эти компоненты доступны без вмешательства в конвейер команд посредством контроллера памяти модуля OnCD; регистры и ячейки памяти, которые не проецируются в адресное пространство памяти микроконтроллера и доступны посредством выполнения команд в RISC-процессоре. К таковым относятся, например, регистры Системного Управляющего Сопроцессора (CP0) в RISC-процессоре, регистры регистрового файла и т.п. Для снятия состояния этих компонентов используется следующий механизм: в режиме исполнения команд по тактам конвейера производится выполнение команд, находящихся в конвейере (за исключением команды, находящейся на стадии декодирования) путем выполнения пяти тактов с принудительным заполнением регистра команд IRdec NOP операцией. Это является также очисткой конвейера команд и искусственным разделением программы на полностью выполненную до точки останова и невыполненную после точки останова части. Отметим, что статус выполнения команд при этом не меняется. Для того чтобы не возникло исключение эти пять тактов выполняются при установленном в статусном регистре OSCR в модуле OnCD необходимого флага, а в регистр РС каждый раз заносится адрес 0хbfc0_0000; 396 IRdec PCwb PCmem PCexe PCdec PC MEM_Ctr OMAR, OMDR DOUT_OnCD DIN_OnCD WRITE READ RDY R I S C TDO TRACE Logic OTC ISTRACE PC[31:0] ABUS[31:0] WR RD BP Logic OMLR0, MLR1, OMBC, OBCR M U X R I S C ISBPT OSCR Trv_num[2:0] EXC Vector BP Lgic ISVBP TDI IRd Instraction OnCD TCK Cpt_DR Sh_DR Updt_DR DEBUG_EN reset Contrl Signals Ctr_Stall_DB Ctr_OnCD Sel GO DEBUG_Req Stall_DB Stall_CPU BREAKD RUN BP_dsp R I S C DSP Рис. 2. Структурная схема модуля OnCD В силу того, что все последующие операции проводятся с использованием регистрового файла, необходимо предварительно снять и запомнить его исходное состояние, для этого выполняется 31 раз следующая последовательность действий: один такт конвейера с предварительно занесенной командой перехода (Jamp Register, JR) в IRdec и затем чтение РС. В РС будет находится содержимое регистра регистрового файла, по которому был сделан переход. Заметим, что выполнение команд, занесенных в IRdec, здесь и в последующем должно сопровождаться занесением в РС адреса 397 0хbfc0_0000. (Это начальный адрес программы, выполняемой RISC-процессором после снятия сигнала RESET. Адрес - не транслируемый и не кэшируемый и всегда обеспечен системой). Перед началом снятия состояния регистрового файла в регистре OSCR устанавливаются необходимые флаги, которые блокируют возникновение исключений, связанных с трансляцией виртуальных адресов, появляющихся в счетчике команд PC при последующих операциях, и блокирует возникновение исключений из-за невыравненных на границу слова адресов в РС и прерываний. После этого процессор готов для выполнения команд, заносимых в IRdec и необходимых для индикации (или изменения) состояний регистров; выполняются привилегированные команды по чтению системных регистров в регистровый файл (при необходимости можно также менять в них информацию). Выполняются эти команды следующим образом. Заносится в IRdec требуемая команда, а в РС адрес 0хbfc0_0000, после чего конвейер команд продвигается на пять шагов, заполняя на каждом шаге, начиная со второго, в IRdec NOP операцию, а в РС адрес 0хbfc0_0000. Чтение информации из регистрового файла производится так же, как описано выше. 5. Процедура восстановления состояния микроконтроллера. Восстанавливается конвейер РС (на фоне NOP команд), а затем заносится команда в IRdec, которая была на момент останова. Загружаются в модуль OnCD новые условия останова исполняемой программы, и производится пуск программы на исполнение. В микроконтроллерах серии «Мультикор» предусмотрена возможность отладки программ в многопроцессорной системе. Адаптер может обеспечить отладку многопроцессорной системы, в которой применяется до восьми микроконтроллеров серии «Мультикор». Схема соединения адаптера для многопроцессорной системы с JTAG портами микропроцессоров приведена на рис. 3. При отладке адаптер обеспечивает следующие функции: в каждый процессор индивидуально загрузку программы, данных, условий останова; одновременный запуск всех микропроцессоров на выполнение задания; сканирование состояния системы на признак её останова по заданным условиям. Отметим, что останов всей системы при выполнении условий останова хотя бы в одном из микропроцессоров, обеспечивается встроенными в микропроцессор средствами отладки через сообщение по двунаправленному выводу Debug Enable (nDE); одновременный останов микропроцессоров по требованию адаптера через JTAG порт. Мультикор №1 Мультикор №8 nDE IBM PC TDI TMS TDO TCK nDE TDI TMS TDO TCK Адаптер TDI TMS [7:0] TDO [7:0] TCK Рис. 3. Схема соединения адаптера с JTAG портами микропроцессоров Обобщенная последовательность действий при отладке программ для однопроцессорной системы представлена на рис. 4. Приведенные в статье процедуры отладки далеко не исчерпывают всех возможных приёмов по отладке. Например, для отладки кэшируемых программ или программ, расположенных во флэшпамяти, в OnCD предусмотрены аппаратные точки останова, для наблюдения прохождения программы (без её модификации) по тактам продвижения конвейера с визуализацией состояния РС конвейера, регистра команд и любого объекта, адрес которого находится в адресном пространстве микроконтроллера, и многие другие сервисные функции, весьма полезные при отладочных операциях. Применение разработанных программных отладочных средств нижнего уровня, наряду с использованием инструментальной среды отладки программ MCStudio, предоставляет пользователям микроконтроллеров серии «Мультикор» широкие возможности по организации отладочных работ, как на уровне программ, так и на уровне аппаратуры. 398 Начало Запрос режима отладки под системным сигналом RESET нет режим отладки ? да Снятие состояния микроконтроллера после системного сигнала RESET Загрузка отлаживаемой программы в память Задание контрольных точек останова программы, запуск программы на исполнение с контролем точек останова режим отладки ? нет да Снятие состояния микроконтроллера после остановки программы, анализ полученных результатов продолжить отладку без коррекции программы? да нет Коррекция и компиляция программы да продолжить отладку после коррекции программы? нет Конец Рис. 4. Блок-схема процедуры отладки программы ЛИТЕРАТУРА 1. Михаил Гук. Аппаратные средства IBM PC. Энциклопедия. Издательство «Питер», 2000. – 816 с. 2. IEEE Standard Test Access Port and Boundary-Scan Architecture IEEE Std 1149.1-2001 (Revision of IEEE Std 1149.1-1990). 399